电子设备应用越来越多地涉及信号处理。家庭影院、计算机图形学、医学成像和电信都依赖于信号处理技术。信号处理需要在复杂但重复的算法中进行快速数学运算。许多应用需要实时计算:即,信号是时间的连续函数,必须对其进行采样并将其转换为数字,以进行数值处理。因此,处理器必须执行算法,在样本到达时对样本执行离散计算。

数字信号处理器(DSP)的架构经过优化,可处理此类算法。一个好的信号处理引擎的特点包括:快速、灵活的算术计算单元(例如,乘法器、累加器、桶形移位器);进出计算单元的不受约束的数据流;扩展计算单元的精度和动态范围(以避免溢出并最大限度地减少舍入误差);双地址发生器(用于同时处理二元运算的两个输入);高效的程序排序(包括有效处理循环和中断的能力);和易于编程。

DSP与精简指令集计算机(RISC)具有其中一些共同特征。此外,两者都是围绕某些核心指令构建的,使它们能够以非常高的指令速率运行;两者都避开了内部微码。然而,它们是根本不同的“动物”。RISC和DSP之间的差异在处理器的

计算单位

数据地址生成器

内存架构

中断功能

循环硬件

条件指令

界面特点

DSP 属于两个基本类:定点,一种基于 16 位整数数据类型的(通常)16 位架构,以及浮点,通常具有 32 位架构,基于同时具有尾数和指数的数据类型。

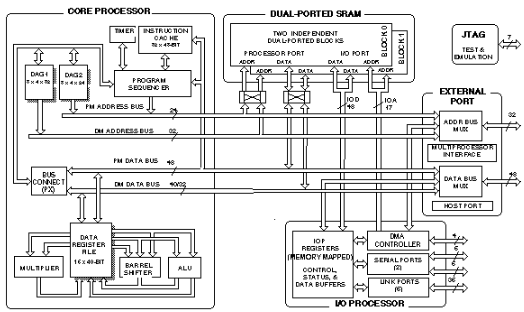

图1.SHARC 内部架构。

计算单元:DSP都包含并行硬件乘法器以支持单周期乘法,其乘法器通常在单个周期中组合乘法和累加。DSP 具有专用累加器,其寄存器明显宽于标称字大小,以保持精度,例如 32 位 ADSP-2106x SHARC 系列中的 80 位(图 1)。硬件可能支持从累加器溢出中恢复,如ADSP-21xx系列。此外,DSP都包含功能齐全的算术逻辑单元(ALU),与乘法器无关。

ALU 可能具有特殊功能,例如能够同时生成求和和差分以加速快速傅里叶变换 (FFT) 中的内核例程,FFT 是一种用于在时域和频域之间转换信号的算法。高级DSP将在计算单元中包含饱和逻辑,以防止数据溢出。它还可以提供零开销(即,不需要额外的时钟周期)陷阱来中断算术异常的例程。

复杂的DSP还可能包含单周期桶移器(即能够在一个时钟周期内将一个单词向左或向右移动任意数量的位),以及用于数据缩放,数据压缩/扩展或打包/解包和位操作的优先级编码器。它还可能包括专用硬件,以最大限度地减少快速除法、平方根和超越函数计算所需的时间。具有这些特殊功能的计算元件在RISC处理器上找不到。

地址生成: 高效的DSP将使其计算单元至少提供来自两个独立数据地址生成器的数据。分接延迟块和系数缓冲器是DSP的特征,但在通用计算中大多是未知的。高效的DSP需要循环缓冲器硬件来支持缓冲器。循环缓冲区指针需要每个周期更新,而不会产生开销。此外,缓冲区结束的比较测试需要一个无延迟命令来重置缓冲区结束处的指针。另一方面,RISC处理器需要为每个比较测试提供一个额外的周期。

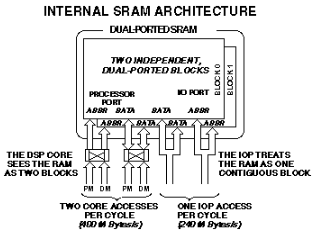

内存架构: DSP 通常支持与通用计算系统不同的系统存储器架构。DSP采用哈佛架构,允许从两个不同的外部存储器持续单周期访问两个单词的数据。例如,ADI公司的SHARC DSP具有集成在片内的2或4 Mb双端口SRAM。该内存是直接寻址的,而不是像RISC处理器那样的缓存。对于CPU来说,这种片上存储器看起来像一个独特的存储器,而不仅仅是系统中其他位置的存储器的高速复制品。原因是DSP通常是嵌入式处理器。它们的片上存储器通常足以容纳任务所需的完整、重复的DSP程序。每个内存块都是双端口,用于内核处理器和 I/O 处理器或 DMA 控制器进行单周期独立访问(图 2)。双端口存储器和独立的片上总线允许在一个周期内从内核传输两个数据,从I/O传输一个数据。

中断功能: 由于DSP旨在在实时系统中运行,因此高效、复杂且可预测的中断处理对于DSP至关重要。RISC处理器具有高度流水线的架构,往往具有缓慢的中断响应时间和有限的中断能力。上下文切换应该非常快。高级DSP,如新型ADSP-21csp01和ADI公司的ADSP-2106x浮点系列,支持完整的替代寄存器集,允许单周期上下文切换以支持中断处理。(寄存器文件窗口不同,因为它的目的是加速参数传递,而不是保存整个上下文。

除内部中断外,高级DSP还将支持至少四个独立的外部中断。中断延迟将保持在几个周期内,并且必须是可预测的。中断应该是可嵌套的和可优先的。此外,应该很容易实时启用和禁用特定中断。

硬件循环:高效环路对于数字信号处理至关重要,因为信号处理算法是重复的。一个好的DSP将支持具有专用内部硬件的零开销环路。也就是说,芯片将监控环路条件和终止,以与所有其他操作并行决定是否将程序计数器或分支递增到环路顶部,而不会造成周期时间损失。另一方面,RISC处理器必须在每个循环结束时进行测试和分支,每个循环和每次通过至少要花费一个额外的周期。嵌套循环在信号处理算法中也很常见;DSP 环路硬件应支持至少四级嵌套环路的深度。RISC处理器尚未发展到支持这些基本的信号处理需求。

条件执行:数据相关执行对于信号处理非常重要。因此,ADSP-2100系列和ADSP-2106x SHARC浮点系列等高级DSP支持有条件地执行其大部分基本指令:在单个指令中,处理器测试条件代码,如果为真,则在同一周期内执行操作。这可以对计算密集型算法产生巨大的影响。英特尔在 i860 中发现了这个问题,并添加了一个图形单元来处理高性能 Z 缓冲所需的条件存储操作。

接口: DSP基于来自模数转换器的实际信号工作,并将结果发送到D/A转换器。因此,DSP通常包含串行端口,用于与这些设备进行廉价接口。高级DSP增加了硬件以提高操作效率,例如双缓冲和自动缓冲。由于这些输入/输出信号可能来自非线性编解码器,因此高级DSP可能具有用于零开销A律和μ律扩容的专用硬件。此外,串行端口可能具有简化与T1和CEPT数据传输线接口的功能。

图2.高效的 SHARC 内存架构允许 I/O 带宽跟上计算速度。

SHARC串行端口旨在通过灵活的硬件最大限度地提高吞吐量,但针对各种信号类型进行了调整。它们的特点包括:每个串行端口可以自动接收和/或发送整个数据块,独立发送和接收每个数据缓冲寄存器以及移位寄存器,TDM多通道模式。

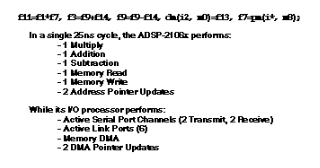

编程注意事项: 曾经,DSP和RISC之间的显着区别在于它们的编程模型。DSP本质上是性能驱动的,因此DSP的编程主要使用汇编语言完成,以便从处理器获得最佳性能。对于定点DSP,通常仍然如此,但使用ADSP-2100系列的直观代数汇编语言则更容易(图3)。在不牺牲性能的情况下,它改善了易用性问题,这个问题促使许多程序员偏爱像C这样的高级语言。

图3.FFT 代码示例。

另一方面,浮点DSP用高级语言编程效率更高。浮点计算避免了分数数据类型,C 中不存在分数数据类型。此外,体系结构决策可能会影响编译器效率。例如,ADSP-2106x SHARC系列的大而统一的地址空间使编译器更容易分配存储器。此外,其大而灵活的寄存器文件提高了效率。

我们产品战略的核心是提供工具和DSP内核,以便能够使用高级语言对定点和浮点DSP进行高效编程。这就是ADSP-21csp背后的驱动力,ADSP-21csp是一个新的并发信号处理器系列。然而,尽管使用高级语言,DSP程序员必须能够在语言级别下降(以最小的痛苦)来提高时间关键例程的性能。

DSP设计越来越多地按照这样的顺序进行编程:首先,用高级语言编写和调试软件原型。此原型通常会产生足够的性能。然而,更一般地说,需要提高性能,因此在模拟中对高级代码进行直方图处理,以找到需要最多执行时间的部分。然后用汇编语言手工编码关键部分。直方图和手动编码过程将迭代,直到达到性能目标。

虽然DSP和RISC之间的差异很多,但这两种架构往往在编程领域趋同,这种融合是由上市时间和DSP在应用中不断变化的作用驱动的。程序员擅长快速开发工作C程序,使用它们更快地将产品推向市场。同时,DSP承担更多的系统管理功能,如用户界面或系统控制,并且需要提供高水平的语言效率,以与以前分配这些控制任务的μC和RISC处理器竞争。

审核编辑:郭婷

-

dsp

+关注

关注

553文章

7987浏览量

348763 -

嵌入式

+关注

关注

5082文章

19106浏览量

304829 -

计算机

+关注

关注

19文章

7488浏览量

87854

发布评论请先 登录

相关推荐

采用光线传感与DSP嵌入式技术实现地震加速度信号处理系统设计

为了在嵌入式系统中实现高效的信号处理请使用DSP

为了在嵌入式系统中实现高效的信号处理请使用DSP

评论