刚写了一段 Verilog代码,辛辛苦苦花了很长时间综合,在debug的过程中,却找不到需要debug的信号了,查看网表发现没有?

这种情况是因为我们的某些中间信号被优化掉了。

被优化掉的原因有可能是你这个信号确实对后面的输出没用,我写的这个项目由于还在中间过程,功能还没有完善,所以不想把大量的中间信号作为输出,所以被优化掉了,以至于在debug过程中找不到这些信号。

如何解决这个问题呢?

很简单,最常用的就是在变量定义的时候添加语句:

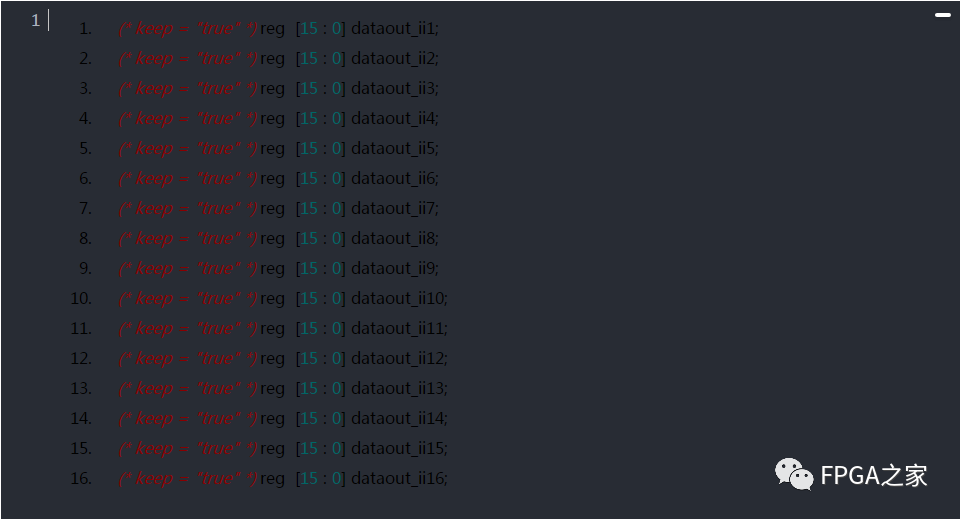

(* keep = "true" *)

例如:

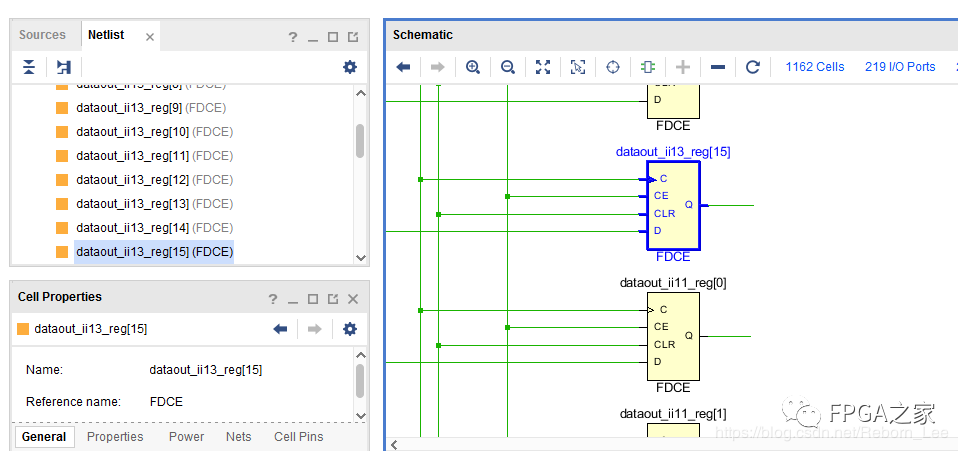

这样即可,从网表中可以找到这些变量了。

当然还有其他办法,例如:

1、 信号前面将keep hierarchy选择yes ,或者选择soft(在综合时保持层次),这样有利于你从模块中找到你想抓取的信号和信号名不被更改。

(* keep_hierarchy = "yes" *)module fre( a, b, c, d);

(* keep_hierarchy = "yes" *)fre fre_inst( a, b, c, d);

2、 信号前面使用(* DONT_TOUCH= “{TRUE|FALSE}” *),可以防止信号在综合,以及布局布线的时候被优化掉。

(* dont_touch = "true" *) wire a;

不在话下。

-

信号

+关注

关注

11文章

2791浏览量

76800 -

DEBUG

+关注

关注

3文章

94浏览量

19928 -

Vivado

+关注

关注

19文章

812浏览量

66582

原文标题:Vivado中如何避免信号被优化掉?

文章出处:【微信号:zhuyandz,微信公众号:FPGA之家】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

提高网络性能的阻抗优化技巧

Vivado之实现布局布线流程介绍

vivado导入旧版本的项目,IP核心被锁。

Vivado使用小技巧

Vivado怎么避免信号被优化掉

Vivado怎么避免信号被优化掉

评论