CXL 在大型数据中心内越来越受欢迎,作为提高不同计算元素(如内存和加速器)利用率的一种方式,同时最大限度地减少对额外服务器机架的需求。但该标准的扩展和修改速度如此之快,以至于很难跟上所有的变化,每一个变化都需要在越来越多的异构且通常是定制的设计中进行验证和确认。

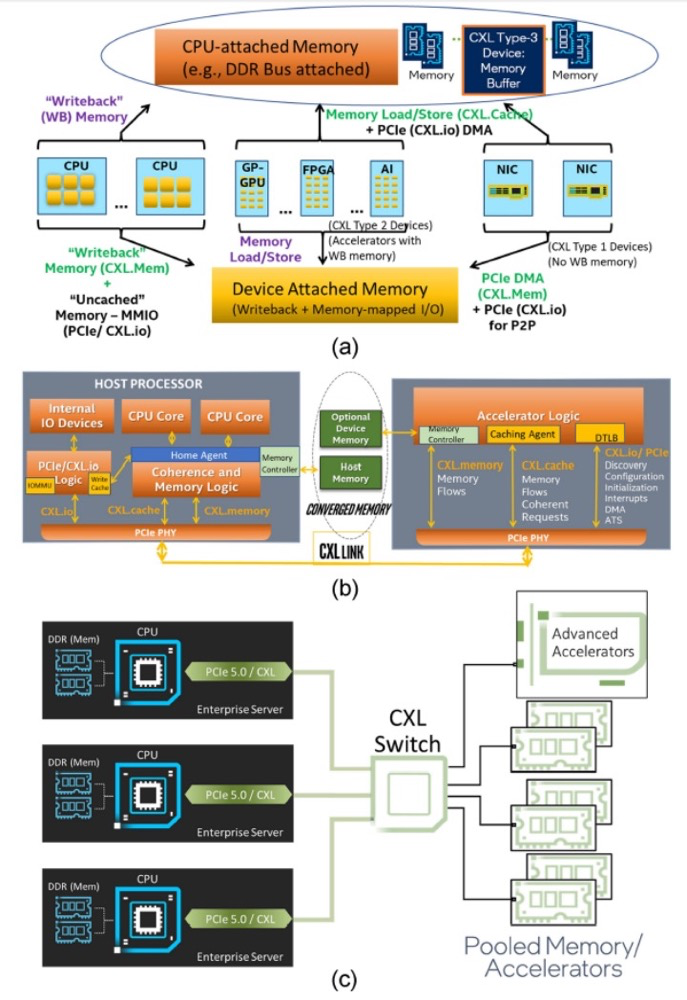

Compute Express Link(CXL)的核心是一种用于内存、处理器和加速器的高速缓存一致性互连协议,它可以使灵活的架构更有效地处理不同的工作负载类型和大小。反过来,这将有助于减轻数据中心的压力,以更少的资源做更多的事情,考虑到需要处理的数据量激增,这似乎是一个巨大的挑战。

过去,典型的解决方案是针对任何容量问题投入更多的计算资源。但随着摩尔定律的放缓,以及为服务器机架供电和冷却所需的功率持续增加,系统公司一直在寻找替代方法。随着电网达到极限和社会对可持续性的需求增加,这一点变得更加重要。

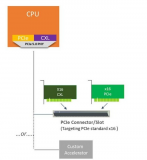

CXL 主要由 Intel 开发,基于 PCIe 标准,在这些相互冲突的动态中提供了一个有吸引力的提议。优化数据中心使用内存的方式可以提高性能,同时还可以降低堆栈复杂性和系统成本。具体来说,CXL 允许 CPU 和连接设备上的内存之间的低延迟连接和内存一致性,从而使这些区域中的数据保持一致。

这对于大容量工作负载尤其重要,例如 AI 训练,其中更多的数据通常等同于更高的准确性,以及日益电动化的车辆、智能工厂、药物发现和气象图等所需的大规模模拟,仅举几例一些。

CXL 联盟由创始成员谷歌、微软、HPE、戴尔易安信、思科、Meta 和华为于 2019 年成立,当年推出了基于 PCIe 5.0 的第一版规范。此后,AMD、NVIDIA、三星、Arm、瑞萨、IBM、Keysight、Synopsys、Marvell等以各种身份加入,Gen-Z技术和OpenCAPI技术相继加入。8月,Specification 3.0被引入,具有两倍的带宽,支持多级切换,以及内存共享的一致性改进。

就标准而言,这个标准进展得非常快。鉴于财力雄厚的公司对 CXL 的支持日益高涨,这一标准似乎很可能会普及。但其快速发展也让 IP 开发人员难以快速从一个版本的标准转向下一个版本。

前景被看好

“我们应该在未来几年真正看到它的起飞,”Cadence的 PCIe、CXL 和接口 IP 产品营销组总监Arif Khan 说。他指出,根据一些内存制造商的预测,到 2030 年,基于 CXL 的应用程序的潜在市场总额预计将达到 200 亿美元。

其他人也同样乐观。“有大量客户在他们的下一代 SoC、加速器、SmartNIC 和GPU 以及内存扩展设备中采用 CXL,” Synopsys PCI Express 控制器 IP 技术营销经理 Richard Solomon 说。

“几乎每个人都在构建具有 CXL 功能的服务器,” Keysight Technologies高级规划和营销经理 Brig Asay 说。“JEDEC 等标准已与 CXL 达成协议,在标准之间开展工作并确保可操作性。CXL 还获得了来自 Gen-Z 和Open CAPI 的资产,它们提供与 CXL 类似的功能,但CXL 具有强大的后劲。”

尽管如此,无论标准进展得有多快,广泛采用都需要时间。尽管共享资源具有吸引力,但数据中心在采用任何新技术时都比较保守。任何故障都可能导致数百万美元的停机时间。

“虽然 CXL 令人兴奋,但该技术仍处于早期阶段,”Arm基础设施业务线产品管理高级总监 Jeff Defilippi 说。“要实现扩散,这些解决方案在进行生产部署之前需要与 OEM 和云服务提供商一起进行严格的功能和性能验证过程。”

Synopsys 高级产品营销经理 Varun Agrawal 观察到,在过去三年中,无数内存和服务器 SoC 公司都表示支持 CXL。但将完全支持 CXL 拓扑和带宽的产品推向市场是一个较慢的过程。“越来越多的设计现在选择通过 cxl.io 为其 PCIe 数据路径采用 CXL,以期扩展到其他类型的设备。就产品推出而言,CXL 在数据中心的扩散一直很缓慢,原因之一是缺乏验证和验证基础设施。”

Agrawal 指出,用户社区越来越多地将 CXL 交易处理器、虚拟模型和主机解决方案、在线速度适配器和接口卡硬件解决方案作为他们的首要要求,同时计划他们的验证/验证。“CXL 为希望同时启动硬件-软件验证、软件启动和合规性以实现其上市时间目标的公司提供了软件优先方法的范例。”

系统级验证也是一项要求。“根据支持的特性,验证可以跨越资源共享、池化和扩展等内存特性;主机和设备之间的一致性;安全和路由;热移除和添加;具有不同虚拟层次结构的多个域;和互连性能——尤其是 .cache 和 .mem 的延迟,”Agrawal 解释道。

流行属性

那么,尽管存在这些差距,为什么仍采用 CXL?Synopsys 的 Solomon 表示,CXL 最初的重点是缓存一致性,业界对其非对称一致性协议很感兴趣。直到后来,重点才转移到解决传统内存附件和 DRAM 接口的局限性上。

“现在你有了这种缓存方法和这种内存连接,它们中的每一种都以不同的方式将 CXL 推向数据中心,”他解释道。“对于人工智能和机器学习,SmartNIC、数据处理单元、服务器附加设备专注于智能处理服务器中的数据,而不是主机 CPU。这些人真的对高速缓存一致性互连很感兴趣。对于超大规模器,CXL 在处理器和内存之间创建了一个分离,允许在需要不同数量的易失性和非易失性内存的作业之间更有效地分配资源。”

此外,低延迟、跨互连的一致性以及能够支持数据中心应用程序的内存分层需求使 CXL 具有吸引力,”Agrawal 说。“由于它使用现有的 PCIe PHY 层,互操作性有助于推动早期采用并延长产品生命周期。”

这使得 CXL 成为数据中心应用的理想选择。“CXL 为内存访问 CPU 提供缓存一致性,”Keysight 的 Asay 说。“它还支持内存资源池,这是理想的,因为它提高了数据中心 DRAM 的整体利用率。”

虽然 CXL 有多个用例,但 Arm 的 Defilippi 表示,云提供商对跨一组节点共享内存容量并增加关键应用程序的 GB/vCPU 的能力非常乐观。“对于云供应商来说,在他们所有的系统中大量配置 DRAM 成本过高。但通过访问 CXL 附加的 DRAM 池,他们现在可以采用仅具有 2GB/vCPU 的系统并分配额外的 DRAM 容量,使这些系统更适合广泛的工作负载。对于已经高度配置的系统(即8GB/vCPU),额外的 CXL 附加内存现在可以使它们适合需要大量内存占用的应用程序,例如某些 ERP 系统,这些系统目前可能无法在云中运行。在此示例中,CXL 成为将额外工作负载迁移到云的网关。”

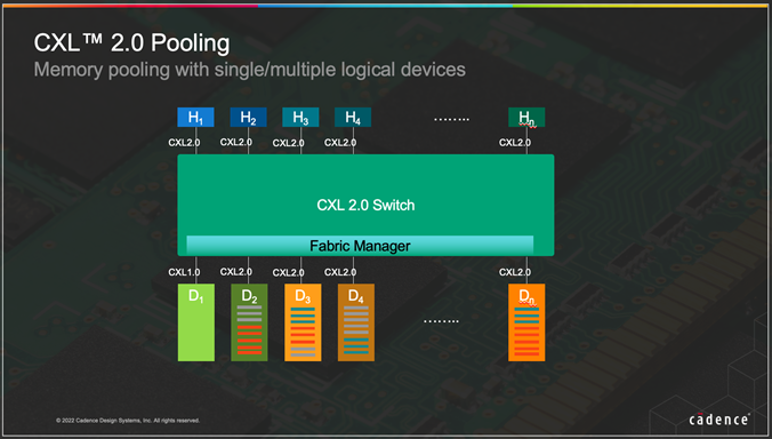

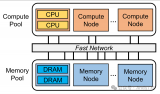

2020 年 11 月发布的CXL 2.0 引入了具有多个逻辑设备的内存池,Cadence 的 Khan 表示这是对规范的关键改进。“这种池功能允许跨多个系统共享资源,包括系统内存。虽然 CXL 是为加速器设计的,但它也支持内存接口。分层配置还可以支持异构内存——封装上的高带宽内存、连接到处理器的快速 DDR5 以及 CXL 模块上的较慢内存。内存是数据中心的一项重要成本项目,而池化是管理系统的有效方式。”

图 1:CXL 2.0 引入了具有单个和多个逻辑设备的内存池

CXL 和定制

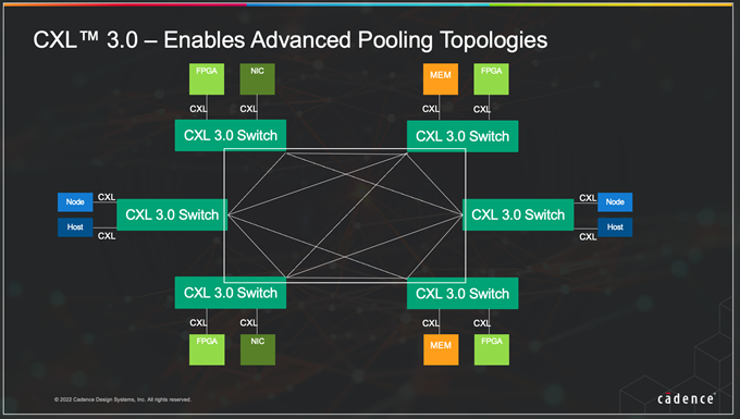

去年推出的 CXL 3.0 更进了一步,通过多级交换实现类似结构的实现。“这允许实施全局结构连接内存,将内存池与处理单元分开,”Khan 说。“内存池也可以是异构的,具有各种类型的内存。在未来,我们可以设想一个叶/主干架构,其中包含用于 NIC、CPU、内存和加速器的叶子,以及一个围绕 CXL 3.0 构建的互连主干交换机系统。”

图 2:CXL 3.0 提供类似结构的多级交换实现

这与数据中心相关,因为在 AI/HPC 世界中没有通用的系统架构。

Khan 解释说,今天的服务器提供了这些应用程序可能需要的合理超集,经常导致利用率不足和能源浪费。“异构应用程序需要非常独特的解决方案来优化实施。HPC/AI/ML 的常见应用程序工作负载各有不同的系统需求。分解系统的愿景是构建大型资源库:内存、GPU、计算和存储资源,以根据需要构建灵活、可组合的架构。换句话说,CXL 通过启用这些功能为分解和可组合的系统铺平了道路。”

CXL 的内存范例还为新的自定义 CXL 设备打开了大门,例如池内存控制器。

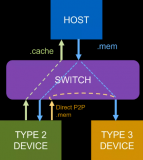

“另一个新兴用例是异构计算,利用 CXL 设备内的缓存一致性在主机 CPU 和 CXL 连接设备之间共享内存。这里的编程模型仍在制定中,但目标是能够在主机和加速器之间共享更大的数据集,这对于 ML 训练等事情非常有吸引力。对于开发中的大量定制 AI 芯片和 GPU/NPU,这可能是一个有吸引力的选择,”Defilippi 说。

当谈到数据中心定制芯片设计中的 CXL 时,Keysight 的 Asay 指出,如果这些设计需要缓存一致性或访问某些共享内存资源,则这些设计必须确保与 CXL 规范的互操作性。“一种常见的定制芯片设计是 SMART NIC,其中 CXL 作为一种传输数据的技术已经变得非常普遍。”

安全性也很重要,Synopsys 的 Agrawal 认为交易和系统级别的安全功能可能会推动数据敏感应用程序的定制设计,因为多家公司都在 CXL 上开发自己的应用程序级接口以优化其设计。

结论

在与数据中心和 HPC 相关的更广泛的内存生态系统中还有其他定制可能性,包括结合开源标准来创建新产品。

Blueshift Memory 是一家总部位于英国的芯片初创公司,其背后是一种名为 Cambridge Architecture 的替代内存架构。该公司正在使用 RISC-V 和 CXL 来部署 is 技术。该公司首席执行官兼首席技术官 Peter Marosan 表示,使用这些开放标准使公司在制造商购买现成 CPU 方面节省了 1000 万美元的潜在支出,并“为我们和我们的整个团队打开了市场大门。”

至于即将发生的事情,Synopsys 高级产品营销经理 Gary Ruggles 表示,他开始看到汽车行业对 CXL 2.0 和 CXL 3.0 的第一批询价。“当你现在看汽车时,它们就像漫游的超级计算机。这些人看到的与我们在数据中心看到的完全一样,这不足为奇。”

审核编辑:刘清

-

处理器

+关注

关注

68文章

19281浏览量

229789 -

cpu

+关注

关注

68文章

10860浏览量

211723 -

加速器

+关注

关注

2文章

799浏览量

37863 -

PCIe

+关注

关注

15文章

1238浏览量

82639

原文标题:CXL的崛起

文章出处:【微信号:TenOne_TSMC,微信公众号:芯片半导体】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

内存扩展CXL加速发展,繁荣AI存储

韩国无晶圆厂初创公司Panmnesia展示第一个支持CXL的AI集群

研华科技推出SQRAM CXL 2.0 Type 3内存模块SQR-CX5N

如何利用CXL协议实现高效能的计算架构

打造异构计算新标杆!国数集联发布首款CXL混合资源池参考设计

新思科技CXL 3.1验证解决方案

国数集联发布业界首款CXL多级网络交换机,IB时代的颠覆者

国数集联研发出首款CXL多级网络交换机

三星携手红帽成功构建全球首个CXL认证基础设施

工程智能:崛起中的中国力量

三星研发CXL混合存储模组,实现闪存与CPU数据直传

利用CXL技术重构基于RDMA的内存解耦合

什么是CXL技术?CXL的三种模式、类型、应用

CXL的崛起之路

CXL的崛起之路

评论