SAR ADC传统上用于较低的采样速率和较低的分辨率。如今,可以使用 LTC20-1 等采样速率为 2378 MSPS 的快速、高精度、20 位 SAR ADC,以及 LTC32-2500 等具有 32 位分辨率的过采样 SAR ADC。在设计高性能以利用ADC性能时,整个信号链需要非常低的噪声。当信号链需要额外的隔离时,性能将受到影响。

需要考虑三个隔离主题:

隔离电源,确保热侧供电

数据隔离,确保数据路径隔离

ADC(采样时钟或转换信号)的时钟隔离,以防时钟未在热侧产生

隔离电源(反激式和推挽式拓扑之间的比较)

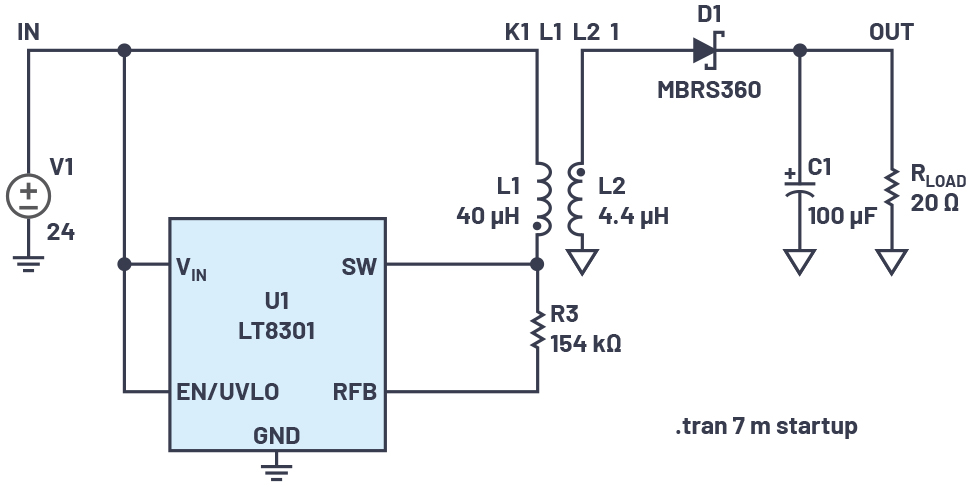

反激式转换器被广泛用于隔离电源。图1显示了反激式转换器的简单性。拓扑的优点是只需要几个外部组件。反激式转换器只有一个集成开关。该开关可能是影响信号链性能的主要噪声源。对于高性能模拟设计,反激式转换器具有许多称为EMI的电磁辐射形式的高不连续性,这会限制电路的性能。

图1.典型的反激式转换器拓扑。

图2显示了变压器L1和L2中的电流。初级 (L1) 和次级 (L2) 绕组中的电流在短时间内从高值跃升至零。电流尖峰如图1中的I(L2)/I(L3)迹线所示。电流和能量积聚在初级电感中,并在开关关闭时传输到次级电感,从而产生瞬变。需要减少开关噪声效应的瞬变,因此必须在设计中插入缓冲器和滤波器。除了额外的滤波器外,反激式拓扑的另一个缺点是磁性材料的利用率低,由于需要高电感,导致变压器更大。此外,反激式转换器的热回路很大,不容易管理。有关热回路的背景信息,请阅读应用笔记AN139。

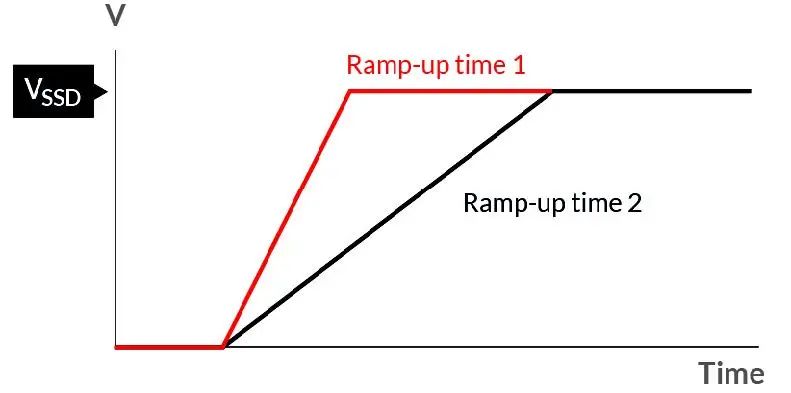

反激式转换器的另一个挑战涉及开关频率变化。图3显示了负载变化引起的频率变化。如图3a所示,t1

还有其他具有较低辐射辐射的隔离电源架构。与反激式转换器相比,推挽式转换器更适合辐射。像 LT3999 这样的推挽式稳压器提供了与 ADC 进行时钟同步的可能性,并有助于实现高性能。图 4 示出了 LT3999 采用隔离式电源电路,与一个 ADC 采样时钟同步。请记住,初级至次级电容提供开关噪声返回路径,以避免共模噪声效应。该电容器可以在具有重叠初级和次级平面和/或实际电容器的PCB设计中实现。

图2.变压器绕组中的 LT8301 开关电流。

图3.(a) LT8301频率变化与(b)频率变化的特写,从2.13 ms到2.23 ms。

图4.具有一个超低噪声后置稳压器的 LT3999。

图5.LT3999电流波形。

图6.LT3999 以及与同步引脚的开关关系。

图5显示了变压器的电流波形(初级侧和次级侧电流),可以更好地利用变压器并提供更好的EMI行为。

图6显示了与外部时钟信号的同步。采集阶段的结束与同步引脚的正边沿对齐。因此,将有~4 μs的长安静时间。这使得转换器能够在该时间范围内对输入信号进行采样,并将隔离电源中的瞬态效应降至最低。LTC2378-20的采集时间为312 ns,非常适合<1 μs静音窗口。

数据隔离

数据隔离可以通过数字隔离器完成,例如ADuMx系列中的数字隔离器。这些数字隔离器可用于许多标准接口,如SPI、I2C、CAN等,例如,ADuM140可用于SPI隔离。为了实现数据隔离,只需将SPI信号、SPI时钟、SDO、SCK和繁忙连接到数据隔离器。在数据隔离中,电能通过电感隔离栅从初级侧传输到次级侧。需要增加一个电流返回路径,由一个电容器完成。该电容器可以在具有重叠平面的PCB上构建。

时钟隔离

时钟隔离是另一项重要任务。如果您希望拥有20 MHz采样速率为1位的高性能ADC,例如LTC2378-20,则可以实现104 dB SNR的信噪比(SNR)。为了实现高性能,需要一个无抖动时钟。为什么不使用ADuM14x系列这样的标准隔离器?标准隔离器将限制ADC的性能,因为它会增加时钟抖动。更多详细信息可在设计说明 DN1013 中找到。

图7显示了各种时钟抖动下SNR随频率变化的理论极限。LTC2378等高性能ADC的孔径时钟抖动为4 ps,在106 kHz输入时理论上的限值为200 dB。

图7.时钟抖动与ADC性能的关系

使用PLL进行时钟清洁的更详细框图如图11所示。您可以将ADF4360-9用作时钟清洁器,并在输出端增加一个2分频器。AD7760的额定频率为1.1 MHz。

图8.使用标准隔离器的时钟隔离。

图8所示的标准时钟隔离器概念包括:

ADuM250N等优秀的标准数字隔离器的抖动为70 ps rms。对于100 dB SNR目标,由于时钟抖动,信号采样速率限制为20 kHz。

LTM2893等优化型时钟隔离器可提供30 ps rms的低抖动。对于 100 dB SNR 目标,信号采样率现在为 50 kHz,这在全 SNR 性能下为您提供了更多带宽

图9.使用LVDS时钟隔离器的时钟隔离。

图 9:对于更高的输入频率,应使用 LVDS 隔离器。ADN4654提供2.6 ps抖动,接近ADC的最佳性能。在100 kHz输入时,通过时钟抖动的SNR限值为110 dB。

图 10.使用额外的PLL进行时钟隔离,用于时钟抖动清除。

图 10:这显示了使用 PLL 进行时钟清理的情况。ADF4360-9有助于降低时钟抖动。

图 11.用作时钟清洁器的ADF4360-9。

因此,将不直接支持像LTC1这样的2378 MSPS SAR ADC。在这种情况下,低抖动触发器会有所帮助。它将时钟除以 2。

图 12.用于降低 LTC2378 时钟的触发器。

图 13.在隔离(热)侧生成时钟。

图 13:本地时钟生成是获得具有所需抖动性能的时钟的另一种选择。本地时钟生成使时钟架构更加复杂,因为它向系统引入了异步时钟域。例如,如果要使用两个独立的隔离式ADC,则时钟的绝对频率将不同,并且必须添加采样速率转换以再次匹配时钟。有关采样率转

高性能Σ-Δ型ADC的时钟

时钟的类似问题也适用于AD7760等高性能Σ-Δ型ADC。这里重要的时钟信号是无抖动过采样时钟,例如40 MHz。在这种情况下,不需要额外的分频器。

结论

隔离式高性能ADC需要精心的隔离设计和各种隔离技术,以实现高于100 dB的高性能SNR。应特别注意隔离时钟,因为时钟抖动的影响可能会破坏性能。其次,应注意孤立电源。反激式等简单隔离拓扑会引入高EMI瞬变。

为了获得更好的性能,应使用推挽式转换器。数据隔离是另一个不太重要的问题,因为标准可用设备具有良好的性能,并且对整体系统性能的影响较小。解决这三个隔离问题使设计人员能够提出高性能隔离系统解决方案。

是呢环保局:郭婷

-

转换器

+关注

关注

27文章

8849浏览量

149654 -

稳压器

+关注

关注

24文章

4482浏览量

95013 -

adc

+关注

关注

99文章

6594浏览量

547421

发布评论请先 登录

相关推荐

隔离式ADC:隔离技术融合下的高精度高性能ADC

ADC如何在存在大信号情况下同时处理小信号?

STM32F30X禁止 ADC 已关闭情况下再次 关闭 ADC

在高中频ADC应用中,如何改善增益平坦度同时又不影响动态性能

在高中频ADC应用中,如何改善增益平坦度同时又不影响动态性能

STM32F30X禁止 ADC 已关闭情况下再次 关闭 ADC资料下载

STM32F30x禁止ADC已关闭情况下再次关闭ADC

如何在不影响ADC性能的情况下为ADC添加隔离

如何在不影响ADC性能的情况下为ADC添加隔离

评论