我可以使用放大器的禁用引脚在不损失性能的情况下节省功耗吗?

电池供电的应用在物联网时代越来越流行。在本文中,我们将展示不必在省电和精度之间进行权衡。

一些运算放大器具有禁用引脚,如果使用得当,它们可以在不影响精度的情况下节省高达99%的功耗。禁用引脚主要用于静态操作(待机模式)。在这种模式下,所有IC都切换到低功耗状态,而无需将器件用于信号处理。这将功耗降低了几个数量级。

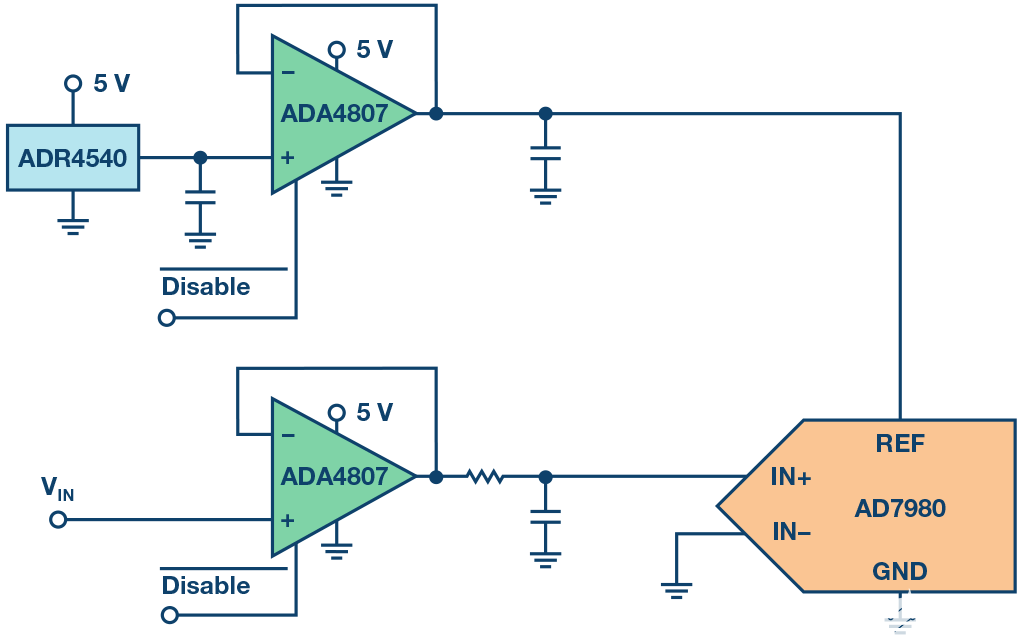

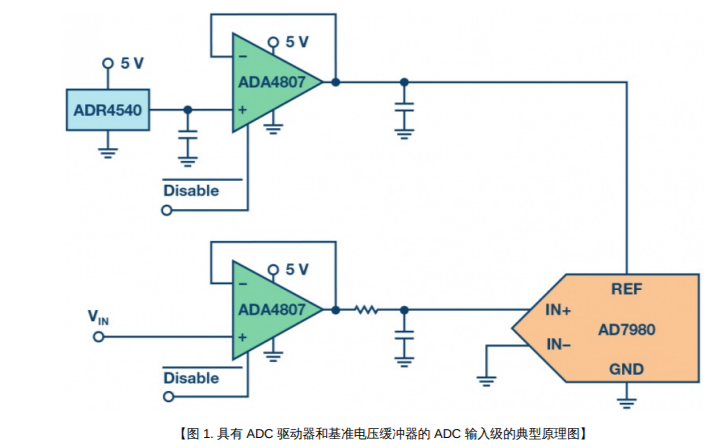

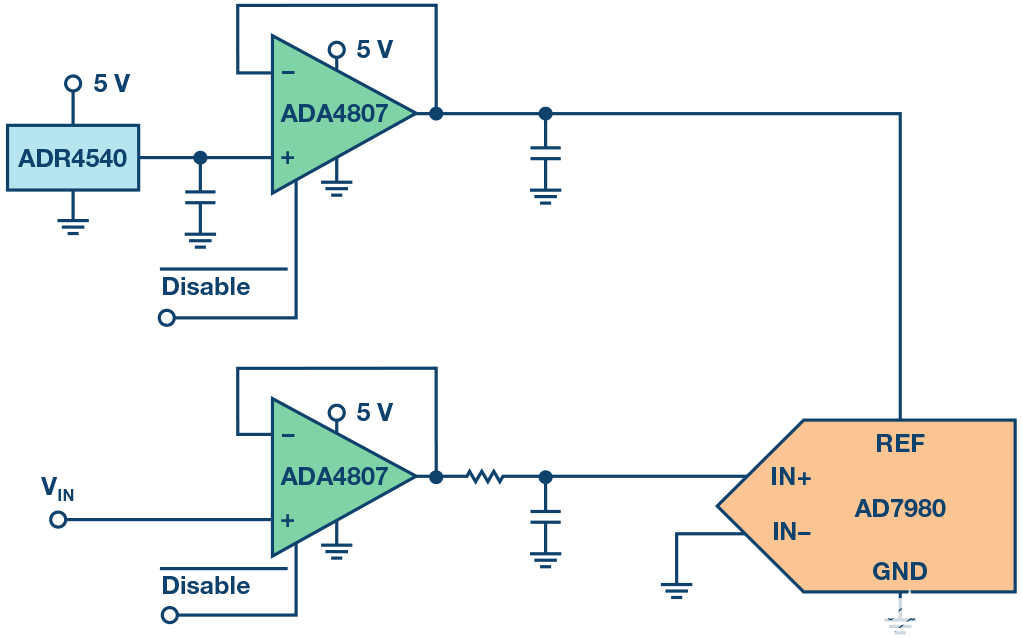

如果需要运算放大器作为ADC的缓冲放大器,如图1所示,它必须处于活动状态才能执行其功能。但是,如果放大器通过禁用引脚切换到关断模式,则功耗仍可保持较低水平。通常,只要ADC不必将任何新值读取到其采样并保持功能块中,就会使用省电模式。

图1.具有ADC驱动器和基准电压缓冲器的ADC输入级的典型原理图。

实现此目的的最简单方法是通过 start 命令进行转换。在标准ADC中,输入(采样和保持)电容首先充电至待测值。直到信号发送到ADC进行转换。然后,输入电容被隔离并连接到转换器级的输入端,此时转换开始。然后完成并设置完成信号,这取决于转换器类型。现在实际问题来了:运算放大器何时必须处于活动状态?它必须在转换开始信号之前足够长的时间处于活动状态,以确保内部输入电容具有与待测信号相同的值。时间长短取决于输入电容的尺寸、待测电压的大小以及运算放大器驱动容性负载的速率等因素。

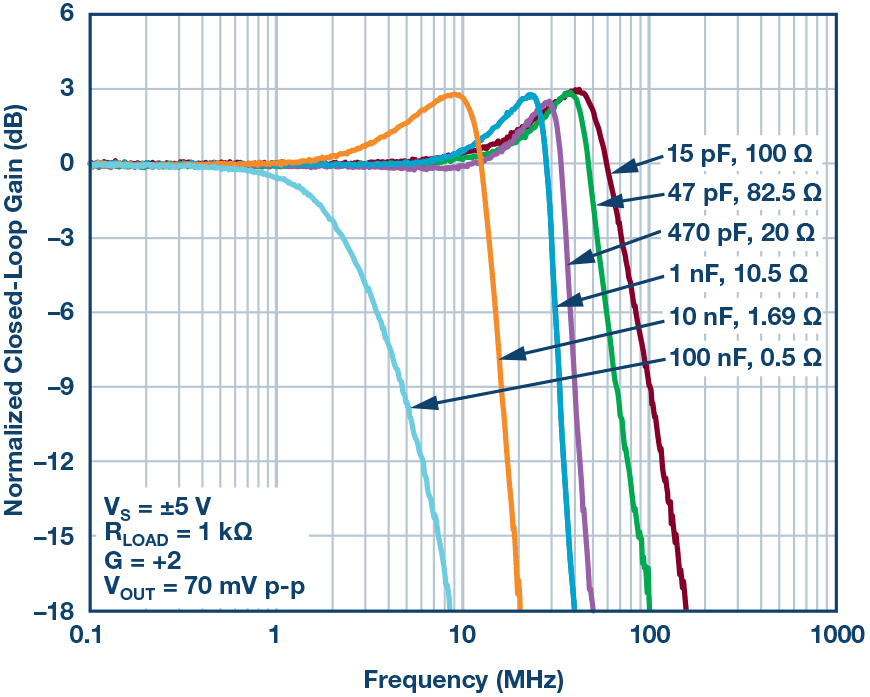

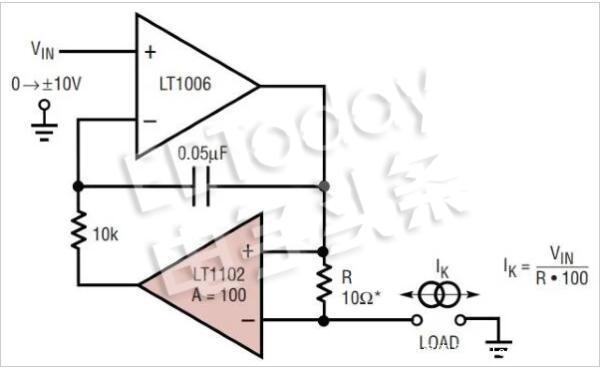

ADC (AD7980)的数据手册给出了30 pF的输入电容值,阻抗为400 Ω。然而,对于运算放大器,事情就不是那么简单了。参数表中给出了15 pF的容性负载,但可能还有更多,如相应的图表所示(图2)。还需要考虑具有2.7 nF和20 Ω的低通滤波器。

图2.ADA4807的频率响应。

该图显示该模块可以驱动足够高的容性负载。禁用后,放大器需要大约500 ns才能建立到全输出电平,在本例中为最大5 V或4.096 V。

为了安全起见,我们假设放大器在转换开始前750 ns开启。比较了1 kSPS至1 MSPS的外推数据。

节省潜力从99 kSPS时的83.0%(总功耗为02.1 mW)到92 MSPS时的41.10%(总功耗为75.1 mW)不等。这只是ADC驱动器节省的成本;参比缓冲器还具有节约潜力。

此示例旨在展示现代设备的功能。在500 ns的最小采样时间下,SINAD偏差为<0.5 dB。就驾驶员而言,值得关注更快的衍生产品并动态操作它们。我们仅将应用程序视为缓冲器(增益 = 1)。对于反相或其他放大器,节省的成本将根据条件而有所不同。应进行测量以检查这一点。

审核编辑:郭婷

-

放大器

+关注

关注

143文章

13640浏览量

214396 -

运算放大器

+关注

关注

215文章

4974浏览量

173712 -

adc

+关注

关注

99文章

6538浏览量

546019

发布评论请先 登录

相关推荐

问题:可以使用放大器的禁用引脚来节省功耗而不影响性能吗?

灵活利用运算放大器的禁用引脚

灵活使用放大器的禁用引脚

灵活使用放大器的禁用引脚

灵活使用放大器的禁用引脚

【微信精选】一招教你如何正确使用运算放大器的禁用引脚

放大器的禁用引脚使用技巧

如何正确使用运算放大器的禁用引脚?

运算放大器禁用引脚能节省多少功耗

放大器上禁用引脚的动态使用

放大器上禁用引脚的动态使用

放大器上禁用引脚的动态使用

评论