摘要:

翘曲问题广泛存在于基板类封装产品中,对于堆叠芯片FPBGA 产品来说,控制产品的翘曲十分重要。在分析堆叠芯片FPBGA 产品翘曲度与材料的热膨胀系数、体积、温度变化量关系的基础上,将翘曲仿真模拟和DOE 相结合,确定出模塑料和芯片是影响翘曲度的主要因素,并找到最优化值。测量基板和产品的实际翘曲度,对比印证了仿真模拟的正确性,为设计开发类似产品时减小翘曲度提供了有效参考。

1 引言

在电子封装产品中,因为各种材料的热膨胀系数(coefficient of thermal expansion,缩写为CTE)不同,加上各材料的模量差异,在封装生产过程中又经过不同的温度变化,产品很容易出现翘曲变形的问题。对于一些高端封装产品来说,翘曲的程度对产品的质量及可靠性尤其重要,特别是一些超薄堆叠芯片和微间距球栅阵列(Fine pitch ball grid array,缩写FPBGA)封装的产品,如果在前期产品设计时未充分考虑到翘曲问题,在后面的实际产品中就会有很大的风险出现产品内部芯片裂损、材料分层、产品外部平面度异常等一系列问题,最终可能造成产品无法成功生产。针对产品翘曲问题,国内外研究人员做过很多相关的分析研究,有关于模塑料原因产生的翘曲分析与解决,有关于堆叠芯片的翘曲仿真模拟分析,还有倒转芯片产品的翘曲改善,但对于超薄芯片堆叠的FPBGA 产品的翘曲研究很少涉及。本文以一款超薄芯片堆叠FPBGA 产品为实例,通过翘曲理论分析和仿真模拟、试验设计(Design of experiment,缩写为DOE)与产品实际翘曲相结合,分析影响产品翘曲的关键因素,找到改善产品翘曲的途径。

2 翘曲影响因素与类型

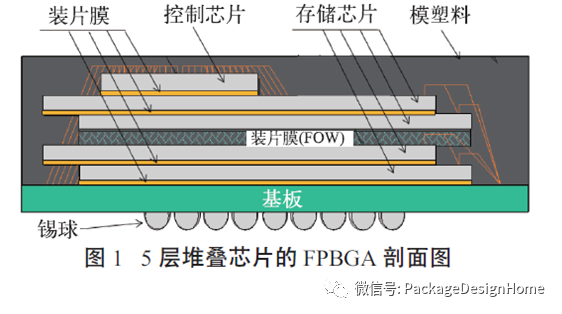

2.1 堆叠芯片FPBGA 产品封装结构

该产品为一款典型的堆叠芯片封装,球栅阵列的节距为0.50 mm,锡球采用Ф0.22 mm 的,根据产品的存储容量不同,存储芯片堆叠数目也不同,分为1 层、2层、4 层和8 层,产品第二颗和第三颗芯片之间采用线上盖膜FOW(Film over wire)工艺,其他均采用通用装片膜工艺,图1 为前期设计概念图,产品为5 层堆叠芯片的剖面图,产品尺寸为13 mm×11.5 mm×1.3 mm,存储芯片尺寸为12mm×10.7mm,控制芯片尺寸为4.8mm×1.5 mm。

2.2 产品翘曲影响因素

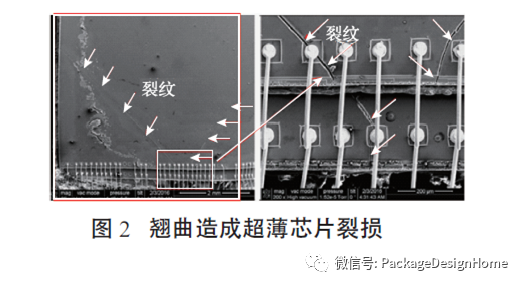

由于不同封装材料的热膨胀系数不同,在温度发生变化后,导致各种材料的收缩率不一致;同时这些材料的弯曲模量也不同,当温度发生变化后,CTE 大的材料其收缩率也大,如果其模量也大于其他材料,那么其他材料一定会被迫拉伸变形,当拉伸力达到超过不同种材料间的粘合力时,不同材料间的粘合处就会出现分层/剥离,如CTE 差异大的模塑料和基板经过高低温循环后,会出现翘曲甚至导致模塑料与基板分层;当拉伸力超过某种材料模量的极限强度时,就会造成该材料裂损,如翘曲导致的模塑料的拉伸力大于芯片的弯曲强度,导致芯片碎裂,如图2 所示。产品是否会发生分层还是发生材料拉裂,受材料间的粘合力与材料弯曲强度影响。

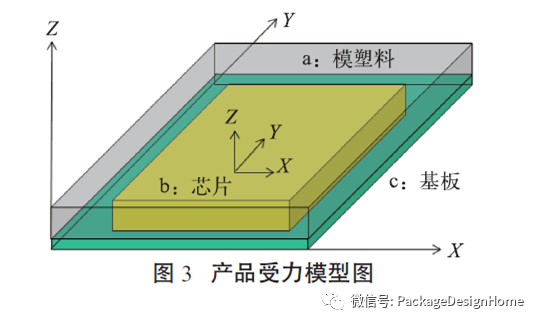

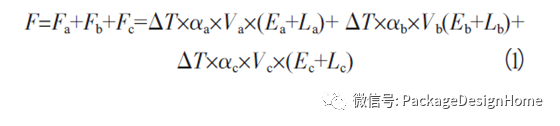

将图2 所示产品简化结构建立如图3 所示的简化模型:将多层复合基板作为一种合应力材料;芯片装片膜模量远远小于芯片且非常薄,对整个产品的影响可忽略不计,最终简化模型由模塑料、芯片、基板组成,结合产品受力模型图,对产品不同受力情况进行分析,温度变化后,产品组成材料的CTE 不同产生的合应力使产品发生形变,随着产品形变逐渐变大,需要的形变力也会增大,从而逐渐抵消因CTE 不同而产生的合应力,最终使产品受力平衡,产品翘曲形变停止。

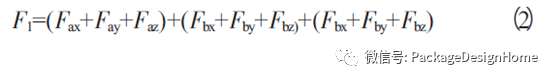

公式(1)中,F 为温度变化时不同材料产生的合应力,Fa、Fb、Fc 为模塑料、芯片、基板由于温度变化产生的应力,ΔT 为温度变化量,Va、Vb、Vc 分别为模塑料、芯片、基板的体积,Ea、Eb、Ec 表示模塑料、芯片、基板的拉伸模量,La、Lb、Lc 表示模塑料、芯片、基板的弹性模量。

假设产品在175℃塑封模具中所有材料的应力为初始状态,当温度降低或者上升时,不同材料的应力开始发生变化,同时不同材料模量不同,合应力F 不断变化,为使产品整体受力为零以达到平衡状态,产品发生翘曲。

公式(2)是产品翘曲稳定后,各材料因CTE 不同在温度变化后产生的应力。各材料变形既有横向拉伸力,也有纵向弯曲力,如Fax、Fay、Faz 为模塑料翘曲后在X 方向、Y 方向和Z 方向产生的应力。由于翘曲后方向通常都趋向于材料模量大的一侧,实际封装结构复杂使应力方向比较复杂,很难得到准确的翘曲角度。

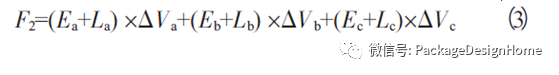

公式(3)是产品翘曲稳定后,通过各材料收缩量不同引起的应力。ΔVa、ΔVb、ΔVc 表示模塑料、芯片、基板收缩量(体积变化量)。

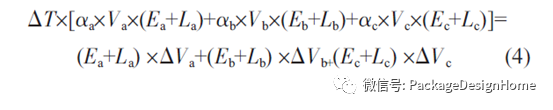

根据力学原理,在力的平衡下,产品整体受力平衡,即F1=F2,得出公式(4):

ΔT×α×V 实际上就是材料体积变化量ΔV,通过公式(4)可以发现,产品温度发生变化,产品的体积跟着变化(收缩或膨胀),而各材料的CTE 不同,体积变化也不同,随着温度变化越大,各材料的体积变化量差异越大,这种体积变化差异的不匹配,最终只能以翘曲的形式出现在产品上。各材料产生的应力ΔT×α×V× (E+L)和温度变化量、热膨胀系数、总体积及模量都有关系。

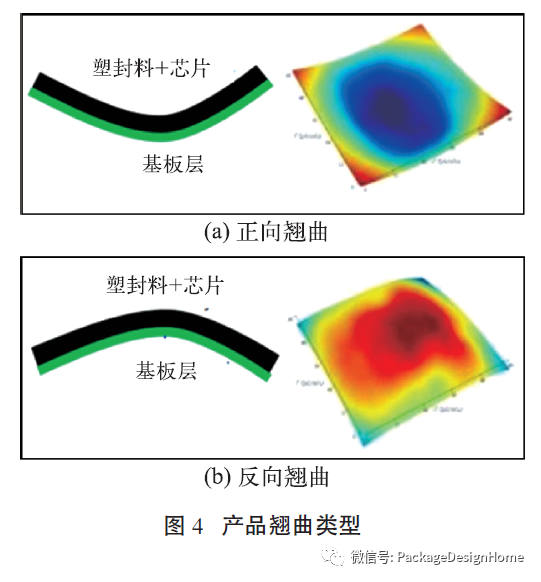

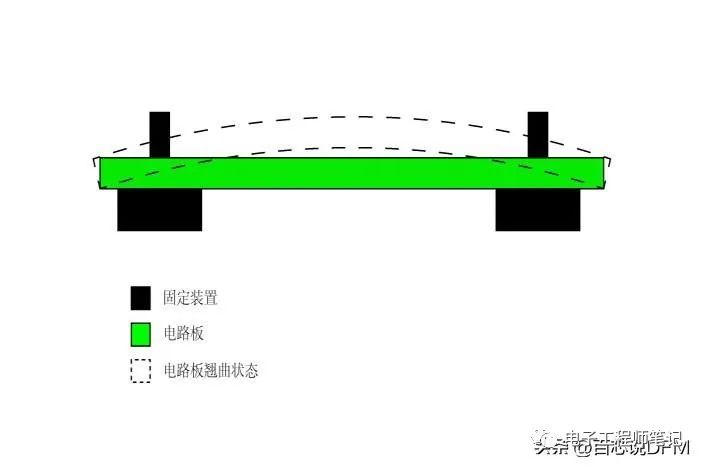

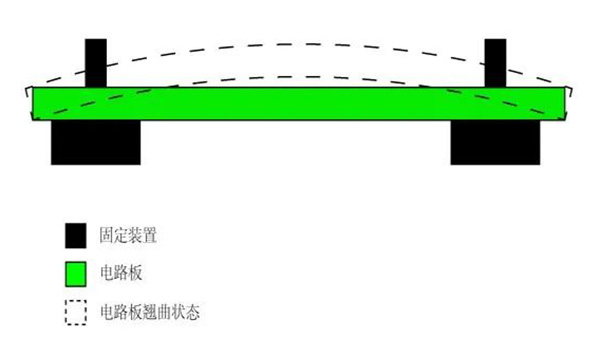

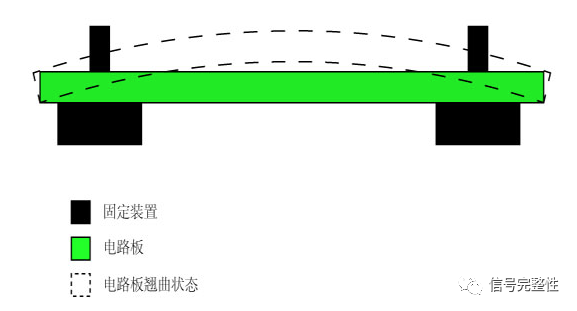

2.3 翘曲类型

以6 mm×6 mm×0.7 mm 的栅格阵列封装产品为例,裸芯片尺寸为4 mm×4 mm×0.2 mm,基板厚度为0.2 mm,由于产品各材料的CTE 不同,温度变化不同,各材料收缩/膨胀量的不匹配使产品出现不同类型的翘曲:正向翘曲(笑脸型)与反向翘曲(哭脸型),如图4所示。正向翘曲是由于模塑料和芯片的CTE 大,从注塑高温降低后,模塑料和芯片层收缩/膨胀大于基板的收缩/膨胀,就产生应力差,当这个应力差大于基板抗形变的力度时,基板因受力被迫变形。反向翘曲产生的机理则与之相反。

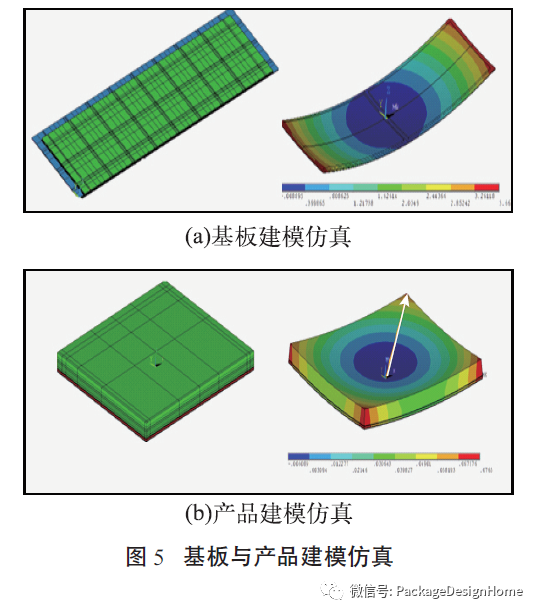

3 基板与产品翘曲仿真模拟

产品发生翘曲的影响因素较多,使用ANSYS13.0软件进行翘曲仿真模拟,并结合DOE 验证,如图5 所示,对该FPBGA 产品建立模型,分别仿真模拟整条基板和单颗产品的翘曲程度。该产品基板翘曲太大将无法进行锡球焊接,在对产品翘曲仿真进行模拟的同时,也对基板翘曲程度进行仿真模拟。

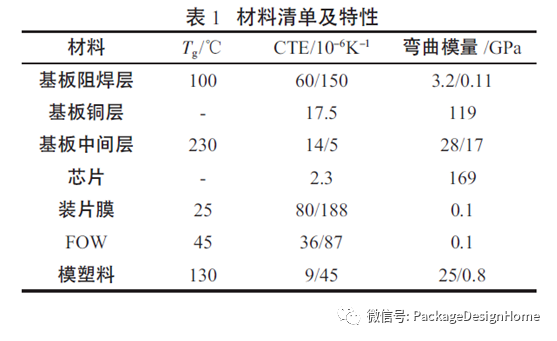

封装产品的各材料特性如表1 所示。

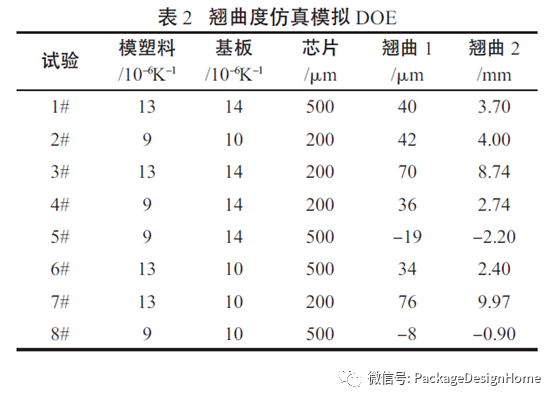

由于芯片的CTE 和模量是定值,DOE 中只取芯片厚度为变量因子;模塑料厚度由塑封模具厚度0.9mm确定,模塑料CTE 为变量因子,其体积随芯片厚度变化而改变;基板厚度固定为200 μm,取其CTE 为变量因子(以基板CTE 为准),DOE 设计如表2 所示,产品、基板翘曲程度分别为翘曲1 和翘曲2(175 ℃塑封时为初始状态,冷却到室温25℃时)。

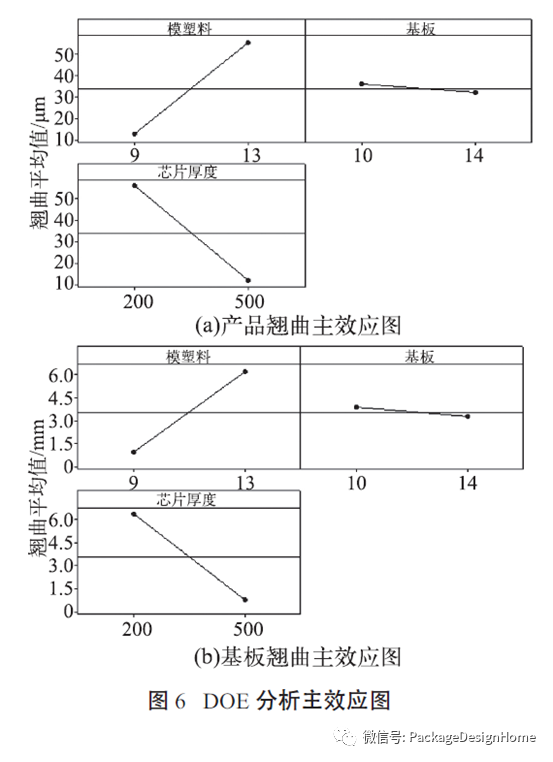

将DOE 结果展开如图6 所示,从图上可以看出,模塑料CTE 和芯片厚度是影响产品、基板翘曲的主要因素,基板CTE 是影响翘曲的次要因素。结合2.2 节应力大小由ΔT×α×V×(E+L)决定,可以推断出模塑料CTE 是影响产品、基板翘曲的主要因素。模塑料CTE与体积乘积量大,影响因子大;芯片厚度的变化也在改变模塑料的体积,这更进一步说明模塑料是影响产品、基板翘曲的最关键因素。

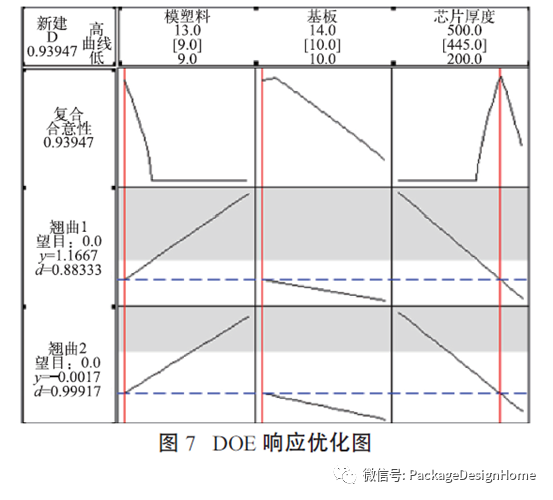

通过DOE 响应优化图(图7)找到产品最小翘曲的因子组合,当模塑料、基板的CTE 最小、芯片厚度为445 μm 时,基板翘曲和产品翘曲最小。

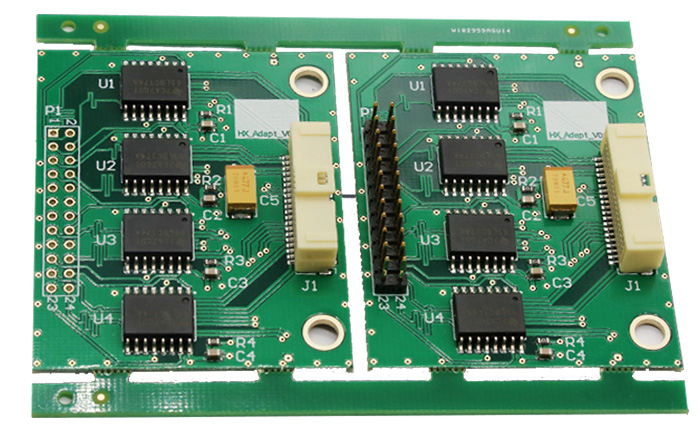

4 基板与产品翘曲测量验证

通过测量制作样品的翘曲,确认是否和仿真模拟结果相同,为了减少样品试验数,仅验证确认芯片在不同厚度下的翘曲程度,样品中有2 层、3 层、4 层、5层堆叠芯片,芯片总厚度分别为200 μm、300 μm、400 μm、500 μm,分别测量基板翘曲和产品翘曲。

4.1 基板翘曲测量与分析

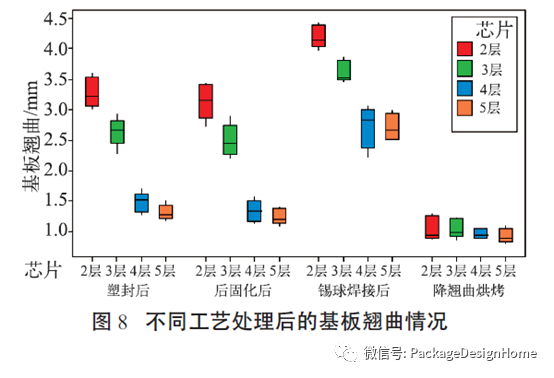

测量在175 ℃塑封、150 ℃后固化、锡球260 ℃焊接、175 ℃降翘曲烘烤后的基板翘曲,结果如图8 所示。400 μm 和500 μm 芯片厚度(4 层芯片和5 层芯片) 的基板经过各温度条件后回到室温翘曲最小, 200 μm 芯片厚(2 层芯片)的基板翘曲最大,后固化后基板翘曲都稍有降低,主要是模塑料进一步充分反应以及部分应力受热释放;降翘曲烘烤基板翘曲减低较小,外在机械矫正时应力已经非常小,应力释放有限。

4.2 产品翘曲实际测量与分析

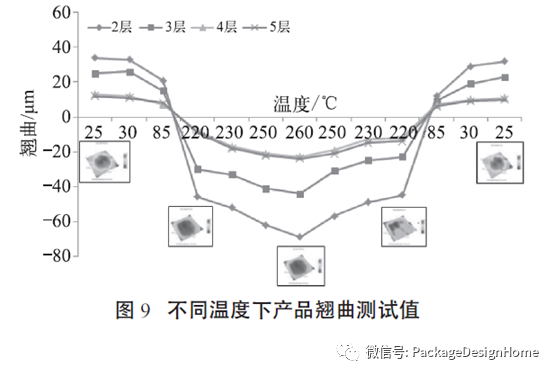

使用投影波纹仪shadow morie 测量实际产品在不同温度下的翘曲:从25 ℃到175 ℃,所有产品呈反向翘曲由大变小;从175℃到260℃,所有产品呈正向翘曲由小变大;无论是室温25 ℃还是高温260 ℃, 200 μm 芯片厚度的产品翘曲都是最大的,如图9 所示。

从翘曲仿真模拟翘曲度和实际产品翘曲度来看,模塑料和芯片的厚度是影响产品翘曲度的主要因素,通过选择低CTE 模塑料和改变芯片厚度/体积可以有效地减小基板和产品的翘曲度。

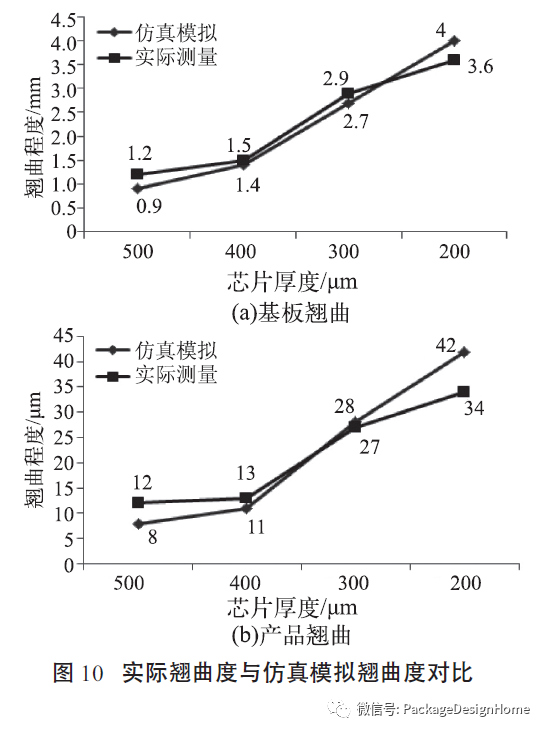

将基板和产品的仿真模拟翘曲度和实际产品翘曲度(从175 ℃降到室温25 ℃时)进行比较,如图10所示,翘曲度存在一定的差异,这是由于实际产品中芯片厚度及其堆叠厚度均会有一定的误差而影响其一致性,但翘曲度随芯片厚度变化的变化趋势是一致的———随着芯片厚度/体积增加(模塑料体积减小),翘曲度减小。

5 结论

文章以一款典型堆叠芯片FPBGA 产品为实例,从理论上分析产品翘曲是由于各种材料CTE 不匹配、体积收缩不一致造成应力不同而导致,其与温度变化量、材料CTE 和总体积相关。研究分析表明,模塑料CTE 和芯片厚度/体积比是影响翘曲的最主要因素,低CTE 的模塑料和基板、厚芯片能够降低基板翘曲和产品翘曲,为类似堆叠芯片FPBGA 产品设计时减小翘

曲提供了较好的参考。

审核编辑 :李倩

-

芯片

+关注

关注

458文章

51521浏览量

429448 -

存储芯片

+关注

关注

11文章

907浏览量

43453 -

封装结构

+关注

关注

0文章

5浏览量

301

原文标题:芯片堆叠FPBGA 产品翘曲度分析研究

文章出处:【微信号:半导体封装工程师之家,微信公众号:半导体封装工程师之家】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

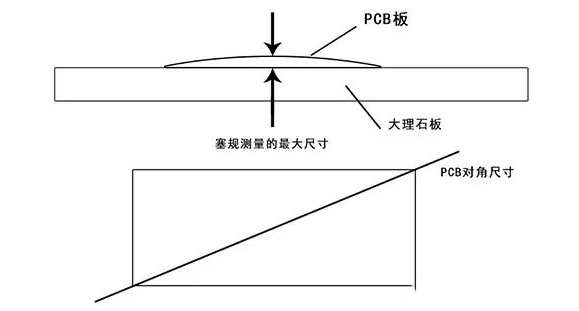

pcb的弯曲和翘曲怎么计算

PCB板的翘曲度

如何预防PCB板翘曲?

常见PCB弓曲扭曲翘曲挠曲分析改善方案

如何预防PCB板出现翘曲的现象

芯片堆叠FPBGA产品翘曲度分析研究

芯片堆叠FPBGA产品翘曲度分析研究

评论