模数转换器(ADC)是任何系统中不可或缺的组件,它依赖于从外部(模拟)世界收集信息进行(数字)处理。这些系统的应用范围各不相同,从通信接收器到电子测试和测量,再到军事和航空航天,仅举几例。硅处理技术(如65纳米CMOS和28纳米CMOS)的进步使高速ADC能够跨越GSPS(每秒千兆采样)障碍。这为系统设计人员提供了对越来越宽的带宽进行采样以进行数字处理的能力。出于环境和成本原因,系统设计人员不断尝试降低总功耗。传统上,ADC制造商推荐使用低噪声LDO(低压差)稳压器为GSPS(或RF采样)ADC供电,以实现最大性能。但是,这不是高效的供电网络 (PDN) 实现。系统设计人员越来越要求使用开关电源稳压器直接为 GSPS ADC 供电,而不会显著降低 ADC 性能。

解决方案在于仔细的PDN实现和布局,以确保ADC性能不会受到影响。本文讨论了线性电源和开关电源之间的区别,并演示了将GSPS ADC与DC-DC转换器结合使用可以显著提高系统电源效率,而不会对ADC性能造成任何影响。本文讨论了使用供电网络组合的GSPS ADC的性能,并对成本和性能进行了比较分析。

传统上推荐用于 GSPS ADC 的 PDN

高带宽、高采样速率ADC(或GSPS ADC)可以有多个电源域(如AVDD或DVDD)。随着几何尺寸的缩小,不仅电源域的数量增加了,而且为ADC供电所需的不同电压的数量也增加了。例如,AD9250,114位、170 MSPS/250 MSPS,双通道模数转换器JESD204B,采用180 nm CMOS工艺构建,具有三个域:AVDD、DVDD和DRVDD。但是,所有三个域的电压相同:1.8 V。

现在考虑AD9680,214位、1.25 GSPS/1 GSPS/820 MSPS/500 MSPS JESD204B双通道模数转换器,采用65 nm CMOS工艺。这款GSPS ADC具有七个不同的域(AVDD1、AVDD1_SR、AVDD2、AVDD3、DVDD、DRVDD和SPIVDD)和三种不同的电压:1.25 V、2.5 V和3.3 V。

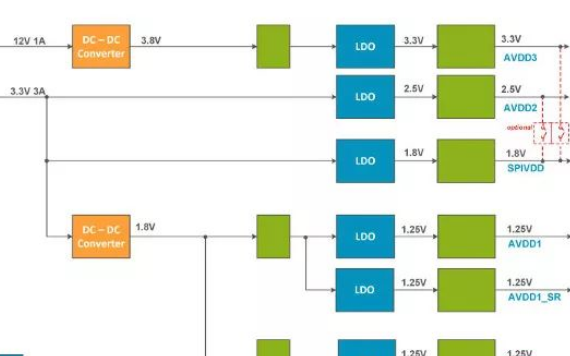

这些电源域和各种电压的扩散对于在这些采样速率下工作是必要的。它们需要确保各种电路域(如采样、时钟、数字和串行器)之间的适当隔离,同时提供最佳性能。正是出于这个原因,ADC制造商设计了评估板,并推荐了精心设计的电源设计,以确保最小的风险和最大的性能。例如,图1显示了AD9680评估板中使用的默认PDN的框图表示。电源输入来自采用 Vita12.1 规范的 FMC(FPGA 夹层卡)连接器提供的 3 V/3 A 和 3.57 V/1 A 电源。ADP23843和ADP21644DC-DC转换器用于将电压降压至可管理的水平,因此LDO无需进入热关断状态即可进行调节。

图1.AD9680评估板的默认PDN。

无需太多时间就能意识到这是一个昂贵的实施方案,有七个LDO稳压器,每个域一个。就性能而言,此 PDN 可能是最佳的,但就运营成本而言,它肯定不是最具成本效益或效率的。系统设计人员发现,实现具有多个ADC的系统具有挑战性。例如,相控阵雷达方案将包含数百个AD9680同步工作。要求系统设计人员在数百个ADC的每个电压域使用一个LDO稳压器是不合理的。

用于 GSPS 模数转换器的更简单的 PDN

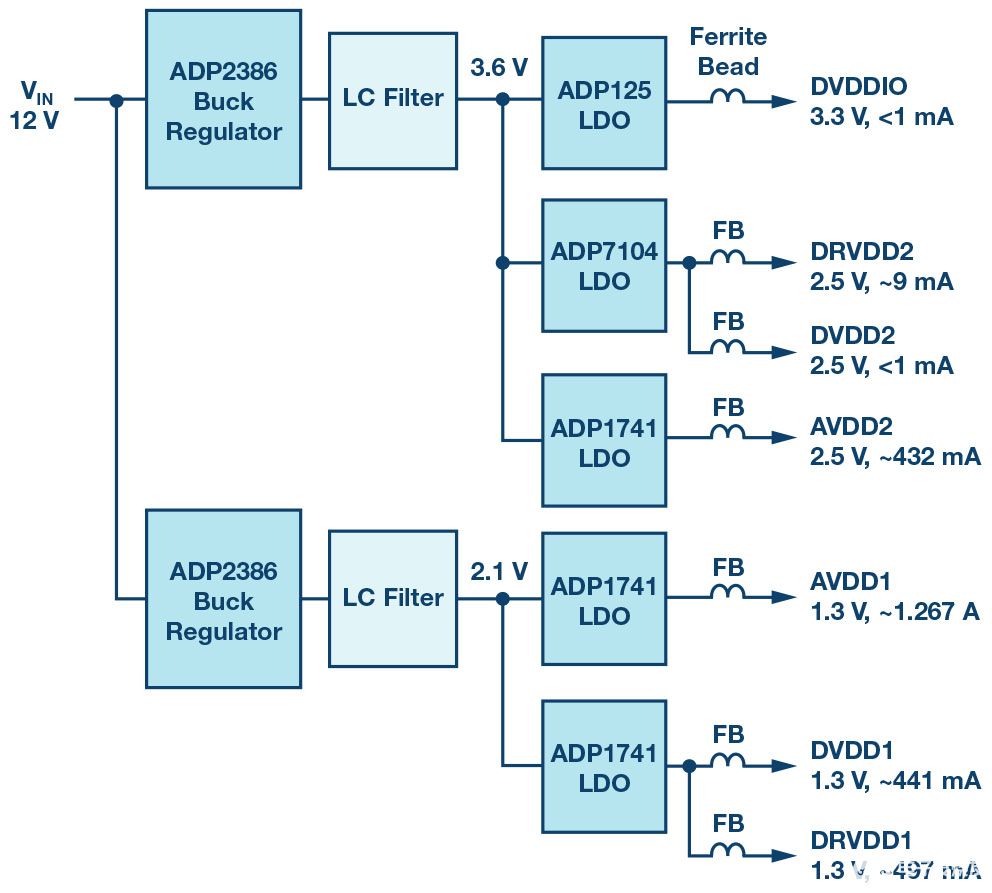

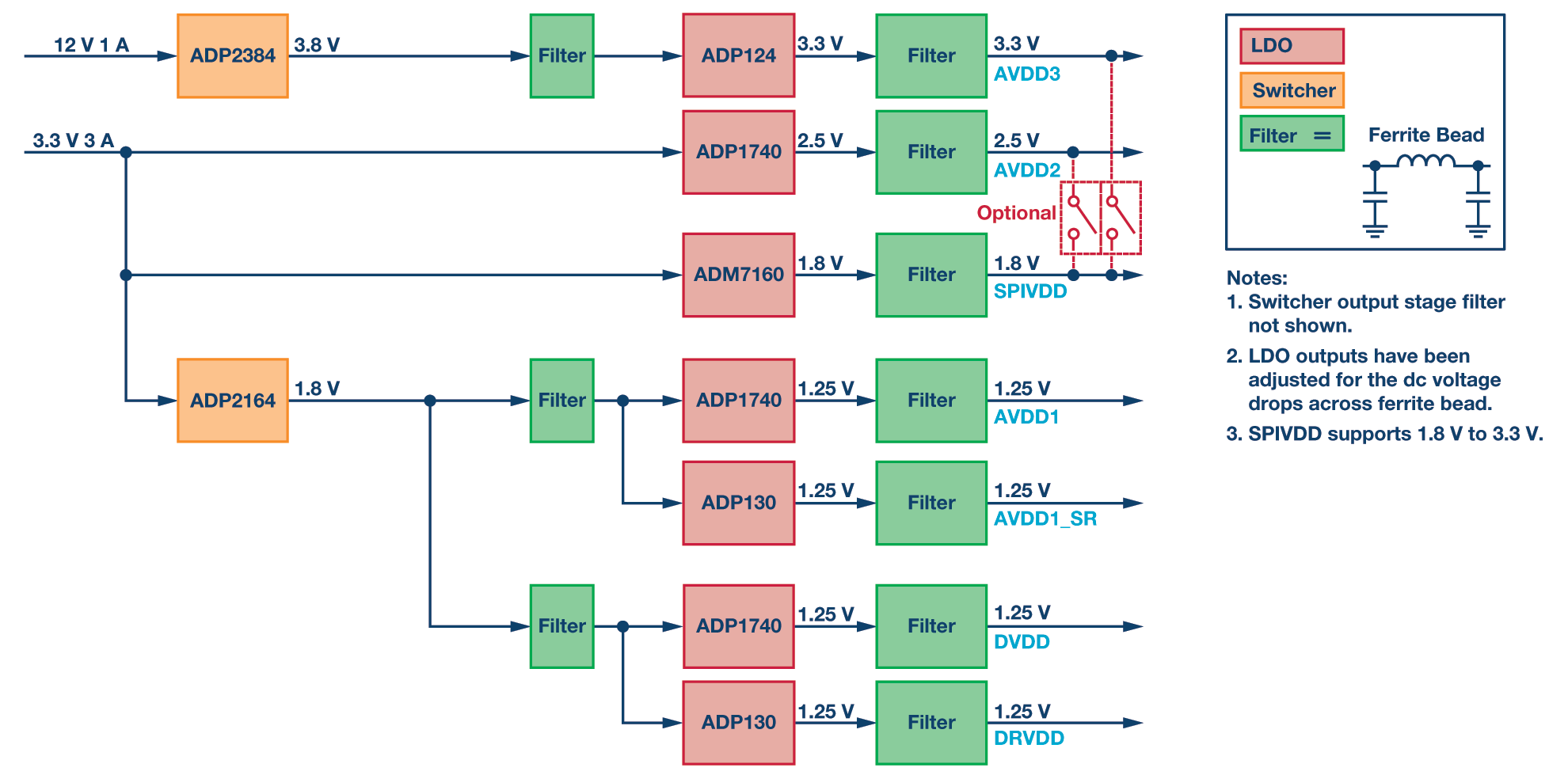

PDN 设计的一种更具成本效益的方法是组合具有相同电压值的域(例如所有具有 1.25 V 模拟域的域),并从同一 LDO 驱动它们。这减少了元件数量(和物料清单 - BOM 成本),并且可能适用于某些设计。简化的PDN如图2所示,在AD9680评估板上实现。在此实现中,整个AD9680可以使用3.3 V单输入供电。

图 2:AD9680 评估板的简化 PDN。

驱动AD9680的DC-DC转换器

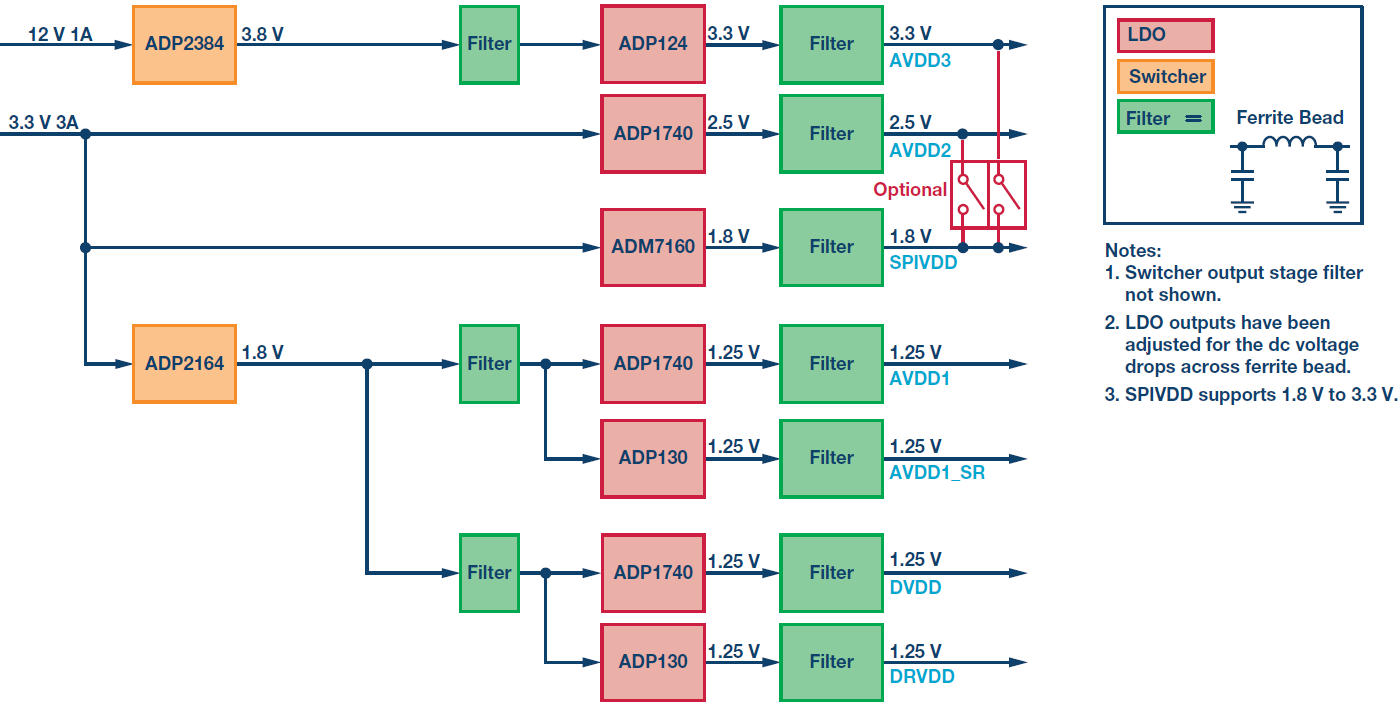

通过完全移除为1.25 V域供电的LDO,可以进一步简化PDN。这将是最有效和最具成本效益的解决方案。这里的挑战是确保DC-DC转换器稳定运行,从而不影响ADC的性能。ADP2164驱动AD1的所有25.1 V域(AVDD1、AVDD9680_SR、DVDD和DRVDD)的PDN如图3所示。

图 3:使用 DC-DC 转换器为 AD9680 供电。

比较各种 PDN

上面讨论的三个PDN与第四个网络一起进行测试,其中AD9680评估板由台式电源供电。表1列出了AD9680评估板上实现的各种供电网络。

表 1.供电网络列表

|

PDN 设置 |

描述 | ||

| 板凳 | AD9680使用台式电源运行 | ||

| PDN #1 |

评估板上的默认 PDN (如图 1 所示) |

||

| PDN #2 |

所有1.25 V域均由一个LDO驱动 (如图 2 所示) |

||

| PDN #3 | 所有1.25 V域均由DC-DC转换器驱动(如图3所示) | ||

由于SPIVDD可以支持1.8 V至3.3 V,并且被认为是非关键节点,因此它使用1.8 V LDO输出供电。在常规系统实现中,SPIVDD可以连接到2.5 V或3.3 V域。也就是说,在许多ADC和DAC之间共享SPI总线的系统中,仍应监控SPIVDD连接。如果是这种情况,必须注意确保正常的SPI操作不会导致SPIVDD域上的电源瞬变。如果SPIVDD低于阈值电平,它们的电源瞬变可能会触发上电复位(POR)情况。

表 2.信噪比性能比较

| 频率(兆赫) | 板凳 | 默认值 (PDN #1) | 简化 (PDN #2) | 切换台 (PDN #3) |

|

63 |

66.5 |

66.5 |

66.6 |

66.7 |

|

170 |

66.4 | 66.1 | 65.9 | 66.2 |

| 340 | 64.8 |

64.5 |

64.5 | 64.7 |

| 450 | 64.0 | 63.7 | 63.6 | 63.8 |

| 765 | 62.5 | 62.2 | 62.2 | 62.3 |

| 985 | 61.3 |

61.0 |

61.0 | 61.1 |

|

1283 |

59.8 |

59.5 |

59.5 | 59.5 |

| 1725 | 57.7 | 57.4 | 57.4 | 57.5 |

| 1983 | 56.7 | 56.4 | 56.5 | 56.6 |

表 3.SFDR 性能比较 (dBFS)

| 频率(兆赫) | 板凳 | 默认值 (PDN #1) | 简化 (PDN #2) | 切换台 (PDN #3) |

|

63 |

83 |

82 |

88 |

83 |

|

170 |

86 | 85 | 85 | 84 |

| 340 | 77 |

76 |

76 | 76 |

| 450 | 72 | 72 | 71 | 71 |

| 765 | 77 | 76 | 76 | 82 |

| 985 | 77 |

76 |

76 | 83 |

|

1283 |

74 |

74 |

74 | 75 |

| 1725 | 67 | 67 | 68 | 67 |

| 1983 | 60 | 60 | 60 | 60 |

表2和表3分别显示了AD9680使用各种PDN时的SNR和SFDR性能。根据AD9680数据手册,遵循了各种奈奎斯特区域的前端网络和寄存器设置建议。2

仅使用DC-DC转换器为AD9680的1.25 V域(PDN #3)供电的PDN在输入频率范围内表现出良好的性能。这证明,可以组合域并高效、经济地为其供电,而不会对ADC性能造成巨大损失。工作台提供的 PDN 是噪声最低的电源,可提供最佳的噪声性能。但是,值得注意的是,PDN #3 始终比默认网络 (PDN #1) 表现出更好的 SNR 性能。这可能是由于LDO适用于低频清理,但即使在电路中,在超过100 kHz的频率上也不会做太多事情。这可以解释使用 PDN #0 时 SNR 的 2.3 dB 优势。

FFT 图

图4和图5分别显示了170 MHz和785 MHz输入时的单音FFT。FFT没有显示频谱衰减,因为1.25 V域由单个DC-DC转换器供电。

图4.170 MHz 输入时的单音 FFT,带 PDN #3。

图5.785 MHz 输入时的单音 FFT,带 PDN #3。

开关杂散

除了噪声性能外,还应检查DC-DC转换器方案是否由于涉及开关元件和磁性元件而产生杂散成分。这就是减少接地环路和地面反弹的仔细布局技术将有益的地方。有许多资源可以帮助测量开关电源噪声。5,6边带杂散出现在开关频率(在本例中为1.2 MHz)的基波偏移的任一侧。必须注意的是,图2或图3所示的输出滤波器级是一个两级滤波器。该两级滤波器是降低开关噪声(纹波)的主要因素,有助于改善ADC噪声(SNR)性能。同样,两级滤波器还有助于减少输出FFT中出现的开关杂散。图6和图7分别显示了170 MHz和785 MHz的这些频率。

图6.1.2 MHz 边带开关杂散,输入频率为 170 MHz。杂散水平 = –105 dBFS。

图7.1.2 MHz 边带开关杂散,输入频率为 785 MHz。杂散水平 = –94 dBFS。

边带杂散的电平可以通过了解PSRR(电源抑制比)或ADC的电源域来估算。7

模拟DC-DC转换器开关电路

DC-DC转换器输出端的两级滤波器可以使用ADIsimPE等工具进行仿真。8图8显示了为仿真PDN的输出噪声和稳定性特性而生成的ADIsimPE原理图。ADIsimPE是一款方便而强大的工具,可帮助系统工程师设计、优化和分析电源网络。

图8.驱动2164.1 V域的ADP25的ADIsimPE原理图。

图9显示了在ADIsimPE中仿真的第一级输出和电路第二级之后的滤波输出。此处所示的纹波约为3 mV p-p。

图9.ADIsimPE仿真的第1级和第2级输出。

物料清单

表4显示了AD9680评估板简化PDN的物料清单,如图2所示。通过使用图 3 所示的网络,系统设计人员可以节省高达 40% 到 45% 的 BOM 成本。BOM 成本是通过计算流行的电子元件供应商网站上的组件的 1k 单价来估算的。

表 4.PDN 物料清单如图 2 所示

| REFDES | 数量 | 描述 |

制造 |

部件号 |

价值 |

|

C1 |

1 | 22 μF、6.3 V、X5R 0805 电容器 |

村田 制作所 |

GRM21BR60J226ME39L |

22 微法 |

|

C2 |

4 | 22 μF、6.3 V、X5R 0805 电容器 |

村田 制作所 |

GRM21BR60J226ME39L |

22 微法 |

| Cf | 1 | 0.1 μF、10 V、X5R 0402 电容 | 村田制作所 |

GRM155R61A104KA01D |

0.1 μF |

| C3, C4, C5, C6, C7, C8, C9, C10, C11, C12, C13, C14, C15, C16, C17, C18, C19 | 17 | 4.7 μF、6.3 V、X5R 0402 电容器 |

村田 制作所 |

GRM155R60J475ME47D | 4.7 μF |

| E1, E2, E3, E4, E5, E6 | 6 | 铁氧体芯片 10 Ω 0402 | 村田制作所 | BLM15AX100SN1D | 10 Ω |

| L1 | 1 | 1.0 μH屏蔽功率电感器,10 mΩ | 线艺 | XAL5030-102ME | 1.0微小时 |

| L2 | 1 | 2.2 μH屏蔽功率电感器,0.1 Ω | 线艺 | ME3220-222ML | 2.2微小时 |

| Rf1 | 1 | 4.99 kΩ, 1% 1, W/10 W 0402 电阻 | 松下 | ERJ-2RKF4991X | 4.99 千分电阻 |

| Rf2 | 1 | 41.2 kΩ, 1% 1, W/10 W 0402 电阻 | 松下 | ERJ-2RKF4122X | 41.2 千分电阻 |

| Rb | 1 | 23.2 kΩ, 1% 1, W/10 W 0402 电阻 | 松下 | ERJ-2RKF2322X | 23.2 千分电阻 |

| ADP2164 | 1 | IC, REG, 降压调节, 4 A, 同步, 16 引脚 LFCSP | ADI公司 | ADP2164ACPZ-R7 | |

| ADP1741 | 3 | 集成电路、注册、线性控制、调整后、2 A、16 引脚 LFCSP | ADI公司 | ADP1741ACPZ-R7 | |

| ADP171 | 2 |

集成电路、正控、线性稳压、调整、0.3 A、5 引脚 TSOT-23 |

ADI公司 | ADP171AUJZ-R7 |

组件选择和布局

ADC 在各种 PDN 上运行时的性能不仅取决于精心设计,还取决于组件的选择及其在 PCB 上的布局。开关电源中产生的高电流通常会导致强磁场,这些磁场会耦合到电路板上的其他磁性元件中,包括匹配网络中的电感器和用于耦合模拟和时钟信号的变压器。必须采用谨慎的电路板布局技术,以防止这些磁场耦合到关键信号中。

电感器选择

由于构成输出滤波级的电感和电容器执行大部分功率传输,因此需要仔细选择它们。在本例中,混合使用了屏蔽和非屏蔽电感。第一滤波级使用屏蔽电感。在这种情况下,第二级可以使用非屏蔽电感。但是,建议在两级都使用屏蔽电感,以最大程度地减少可能的EMI辐射。电感器还被选择在饱和电流(ISAT)和直流电阻(DCR)方面具有足够的裕量,以确保它们不会进入饱和或导致自身电压降过大。

电容器选择

建议使用 X5R 或 X7R 电容器作为输出滤波电容器。电容器还必须具有低ESR(等效串联电阻)。低 ESR 有助于降低输出端的开关纹波。另一个使总ESR和ESI(等效串联电感)最小化的技巧是将电容器并联组合在一起。如图3和表4所示,第一滤波级使用2×22 μF电容,而第二滤波级使用4× 22 μF电容。电容器的额定电压也是其选择的重要因素。这是因为陶瓷电容器的电介质随着直流偏置的增加而降低。这意味着,在6 V直流偏置下,额定电压为3.22 V的50 μF电容可能会降低高达4%的电压9,10。 在本例中,额定电压为6.3 V的电容用于1.25 V电源。在输出端增加更多电容确实会略微增加BOM成本和电路板空间,但这可以很好地防止开关噪声和纹波干扰ADC性能。

铁氧体磁珠选择

如图3所示,铁氧体磁珠用于隔离各种域。铁氧体磁珠的选择也至关重要,因为铁氧体磁珠高于所需的DCR(直流电阻)将导致域电压低于最佳电压。这种低电压导致ADC性能(SNR和SFDR)低于最佳性能。必须充分注意铁氧体磁珠的阻抗特性、最大直流承载能力和DCR。11

PCB 布局注意事项

为了尽量减少开关稳压器和ADC之间的相互作用,DC-DC转换器及其开关元件应远离与ADC相互作用的任何磁性元件(例如前端匹配网络或时钟网络)。在DC-DC转换器布局中,两级滤波器应尽可能靠近DC-DC转换器放置,以最小化环路电流。

结论

RF采样(或GSPS)ADC允许对宽带宽进行数字化,从而在系统设计中具有独特的优势。业界热衷于降低这些GSPS ADC电源设计的复杂性、尺寸和成本。通过充分注意设计、元件选择和 PCN 布局,可以拥有低噪声且具有成本效益的 PDN,从而为 GSPS ADC 供电。通过实施,开关稳压器还有助于提高电源系统效率,并提供运营成本和BOM节省,而不会对性能造成任何影响。

审核编辑:郭婷

-

转换器

+关注

关注

27文章

8707浏览量

147262 -

稳压器

+关注

关注

24文章

4241浏览量

93841 -

DC-DC

+关注

关注

30文章

1949浏览量

81707

发布评论请先 登录

相关推荐

通过输电网络合探讨GSPS ADC性能

RF采样ADC 可对宽带宽进行数字化处理

如何利用开关稳压器为GSPS ADC供电

DC–DC转换器为GSPS ADC提供高效输电网络

DC1818A配置为使开关稳压器提供也为LDO供电的输出

静音开关稳压器μ模块稳压器可为GSPS采样ADC供电

为GSPS或RF采样ADC供电:开关稳压器与LDO

为GSPS或RF采样ADC供电:开关稳压器与LDO

Silent Switcher µModule稳压器为GSPS采样 ADC提供低噪声供电

ADC12D1800RF一款RF采样GSPS ADC数据表

ADC12D1x00RF 12位、3.2 GSPS和2 GSPS RF采样ADC数据表

为GSPS或RF采样ADC供电:开关稳压器与LDO

为GSPS或RF采样ADC供电:开关稳压器与LDO

评论