内置自检(BIST)曾经是为复杂的数字芯片保留的,现在可以在许多数字内容相对较少的设备中找到。向更精细的直线工艺几何形状的转变使ADI公司的多个数据转换器能够包含BIST功能。对于芯片制造商来说,BIST可以通过提供对器件的更大可见性来帮助简化器件表征过程,并通过允许对芯片的某些子集进行自主测试来缩短制造测试时间。当片上BIST功能被整合到系统级设计中时,BIST在系统级实现了更大的优势。随着系统变得越来越复杂,将单个组件与BIST集成,可以实现分层测试策略,从而为增强系统可靠性提供强大的功能。

在系统层面,BIST功能可用于设计阶段,以表征数字处理器和数据转换器之间的数字接口时序。如果没有BIST,数字接口中的位错误必须通过转换器本底噪声的变化来检测。这种类型的错误检测远不如基于数字的BIST签名检查敏感,后者可以检测单个比特错误。同样的数字接口检查可以在生产测试车间执行,也可以在现场的系统级自检中执行。

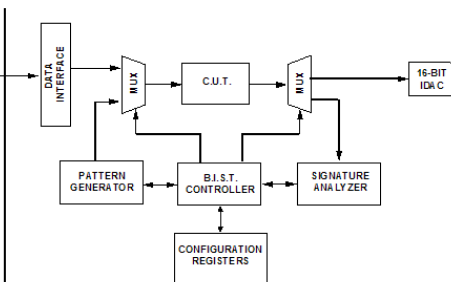

图1 – BIST电路的功能框图

图 1 显示了一个基本的 BIST 实现。将BIST集成到设备中需要添加三个功能块:模式生成器,签名(或响应)分析器和测试控制器。码型发生器激励被测电路(CUT)。特征码分析器收集 CUT 对测试模式的响应,并将其压缩为单个值,称为特征码。测试控制器协调测试电路的动作,并提供一个简单的外部接口。

模式生成器和特征分析器通常使用线性反馈移位寄存器(LFSR)实现。带有n个触发器的LFSR如图2所示。这种类型的模式生成器可以产生宽度为 n 的伪随机模式,具有 2n重复前有 -1 个唯一组合(除所有零之外的所有可能组合)。当初始条件已知时,该模式是完全确定的。

图2 – BIST功能所需的基本组件

特征分析也利用LFSR。 利用第二个类似构造的LFSR可以将CUT对整个模式的响应压缩为单个值。该值在测试完成后存储在寄存器中。然后可以将签名与预期的签名进行比较,以验证设备的正确操作。压缩响应的过程引入了使错误的CUT产生正确特征的可能性,但是随着模式长度的增加,未检测到故障的可能性变得非常小。

在系统级别使用 BIST

在板级,BIST功能可以帮助进行多种类型的测试。例如,测试DAC和数字数据源之间的接口可以通过调用BIST特征分析电路并使用数字源提供测试模式来完成。在这种情况下,DAC制造商将提供测试模式和预期的签名。该设备已经过制造商的测试,因此不正确的签名可能归因于数字接口故障。或者,DAC制造商可以提供一种算法,用于为任意测试模式生成预期的签名。这为源可以提供的模式提供了更大的灵活性。ADI公司提供AD9736高速DAC的BIST模型、测试模式和预期特征。

签名测试是通过/失败类型的测试。不正确签名的特定值无助于诊断故障。但是,设备被激励的方式可以提供有关故障类型的一些信息。例如,不同的测试模式可以将故障隔离到特定的输入引脚。在表征数字接口时,这种类型的测试可用于确定是否存在任何导致降低整个总线时序裕量的外围连接。此信息可用于在后续修订中改进电路板布局。

在某些情况下,可以使用BIST码型发生器代替外部数字码型发生器,从而简化器件和下游信号链其余部分的评估。AD9789内置片内QAM映射器、插值滤波器、数字上变频器,后接14位DAC。可以将 BIST 模式生成器配置为将数据发送到 QAM 映射器。设备将此数据作为调制信号传输。模拟性能可以在DAC的输出端和发射路径信号链的其余部分测量,而无需任何额外的数字激励。这可以加快设计模拟部分的评估,因为它将模拟评估与数字开发分离,并消除了数字测试模式生成所需的特殊电路。

预计在数据转换器和其他“模拟”器件上集成BIST电路将变得越来越普遍,并且功能更强大,因为这些器件转向更小的工艺几何形状。随着 系统 的 复杂 化, 包含 测试 能力 变得 重要。随着数字接口速度的提高,验证这些接口是否可靠变得更加重要和困难。寻找在单个设备上使用 BIST 功能的方法,以提高系统级可测试性和设备评估。

审核编辑:郭婷

-

转换器

+关注

关注

27文章

8778浏览量

148716 -

滤波器

+关注

关注

161文章

7919浏览量

179506 -

变频器

+关注

关注

252文章

6624浏览量

146576

发布评论请先 登录

相关推荐

虚拟设备,模拟实体设备和云端通信

数字BIST的基本原则

适用于低频测量应用的AD7195

USB标准适用于哪些应用

钮扣电池都有哪些类型分别适用于哪些设备?

7000应用开发技巧:模拟设备驱动(Mocking)

模拟设备高速转换器

常见的PLC模拟量IO有哪些?

适用于模拟输出模块的双极Fly-Buck-Boost解决方案

适用于TI超声AFE的模拟时间增益控制(ATGC)解决方案

适用于模拟设备的BIST

适用于模拟设备的BIST

评论