在 2022 年 12 月的 IEDM 会议上,Imec 展示了“Semi-damascene Integration of a 2-layer MOL VHV Scaling Booster to Enable 4-track Standard Cells”,我不仅有机会阅读这篇论文并看到它的展示,而且采访其中一位作者 Zsolt Tokie。

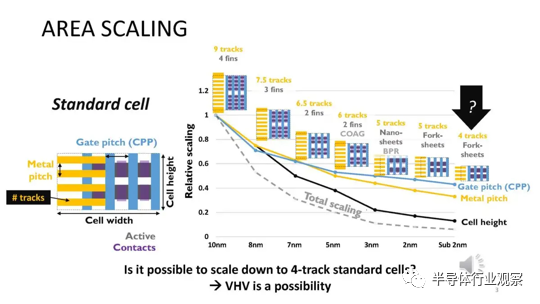

逻辑设计由标准单元构建,例如反相器、与非门、扫描触发器和其他单元。标准单元的宽度是一定数量的接触多晶硅间距 (CPP),具体取决于单元类型以及单元是否具有单扩散中断或双扩散中断,例如,对于单扩散中断,2 输入 NAND 门的宽度为 3CPP,并且4CPP 宽,用于双扩散断裂。标准单元的高度的特征在于金属 2 间距 (M2P) 乘以轨道(M2P 的数量)。

由于扩展 CPP 和 M2P 变得越来越困难,设计技术协同优化 (DTCO) 在使用减少轨道等技术进行扩展时变得越来越重要。目前最小单元一般为6轨,也出现了一些5轨单元格。在本文中,Imec 讨论了实现 4 轨道单元的路由技术。

图 1. 展示了 Imec 从 9 轨到 4 轨的路线图。

在进入这里描述的路由技术之前,我想简单地谈谈单元高度缩放的其他要求,简单地谈论 M2P 和轨道忽略底层设备结构。单元高度必须适合 n 和 p FET、n 到 p 间距和边界宽度。从 FinFET 到水平纳米片 (HNS) 的过渡通过从占据水平空间的多个鳍片切换到垂直方向的纳米片堆叠来提供 n 和 p FET 的缩放。

Forksheets (FS) 和埋入式电源轨 (BPR) 等技术是 Imec 正在开发的用于解决器件高度问题的其他选项,例如 BPR 可以用基板中的高薄电源轨代替宽金属 2 电源轨,从而减少边界宽度,和 forksheets 可以减少 n-to-p 间距。

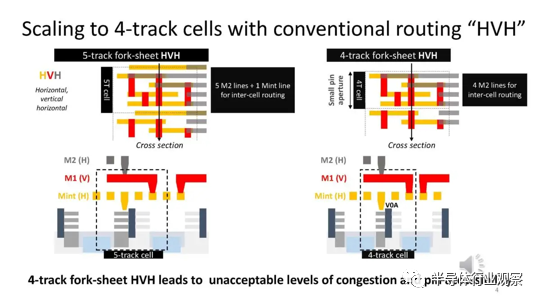

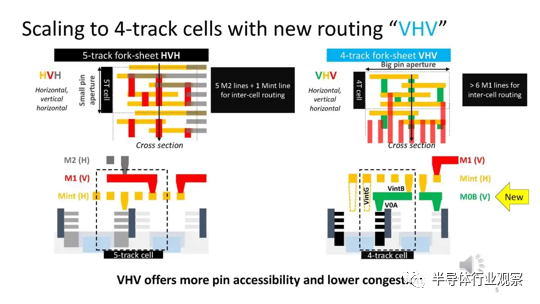

前沿工艺已经在 metal-1 层下引入了中间互连层,这些附加层在 Imec 的术语中通常称为 Metal 0 (M0) 或 Mint。要获得 4 轨道单元,单个 M0 层不足以互连设备。在这项工作中,M0A 和 M0B 添加到 Mint 下方,并且在一种新颖的工艺架构中,Mint 用作掩模以在 M0B 中执行尖端到尖端的切割。

Mint 通过 VintB 向下连接到 M0B,并通过 VintG 向下连接到栅极触点。M0B 通过 Via V0A 向下连接到 M0A 的源极漏极。

图 2 说明了具有 Mint 的 4 轨道单元中的拥塞,图 3 说明了添加 M0B 和 M0A。

图 2. 仅包含 Mint 的拥塞单元格。

图 3. 通过添加 M0B 和 M0A 解决拥塞问题。

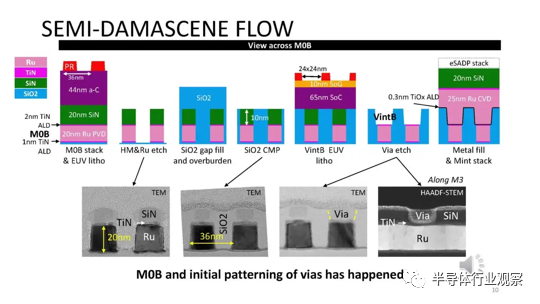

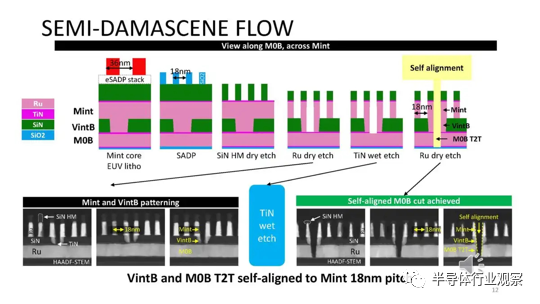

为了实现所需的尖端到尖端的紧密间距,M0B 使用自对准切割,其中 Mint 作为掩模,这需要减法金属化工艺。这里使用的金属化层是使用半镶嵌技术沉积的钌(与铜不同,钌可以干法蚀刻),见图 4。

图 4. 半镶嵌。

自对准 M0B 切割如图 5 所示。

图 5. M0B 自对齐切割。

通过添加两层并使用自对准切割和 4 轨道单元可以互连。如果底层器件结构也可以实现所需的缩放,则此互连方案提供了通往 4 轨道单元和继续缩放的路径。

imec用四张图,展示芯片未来发展路线图

上个月中,SEMICON West 2022于旧金山的 Moscone 中心隆重举行。展会前,Imec 在Moscone 中心附近的Marriott Marquee 举办了一场技术论坛。近年来,Imec 论坛已经从我介绍的工艺技术转向更多的系统和应用论坛,但仍有一些工艺内容。

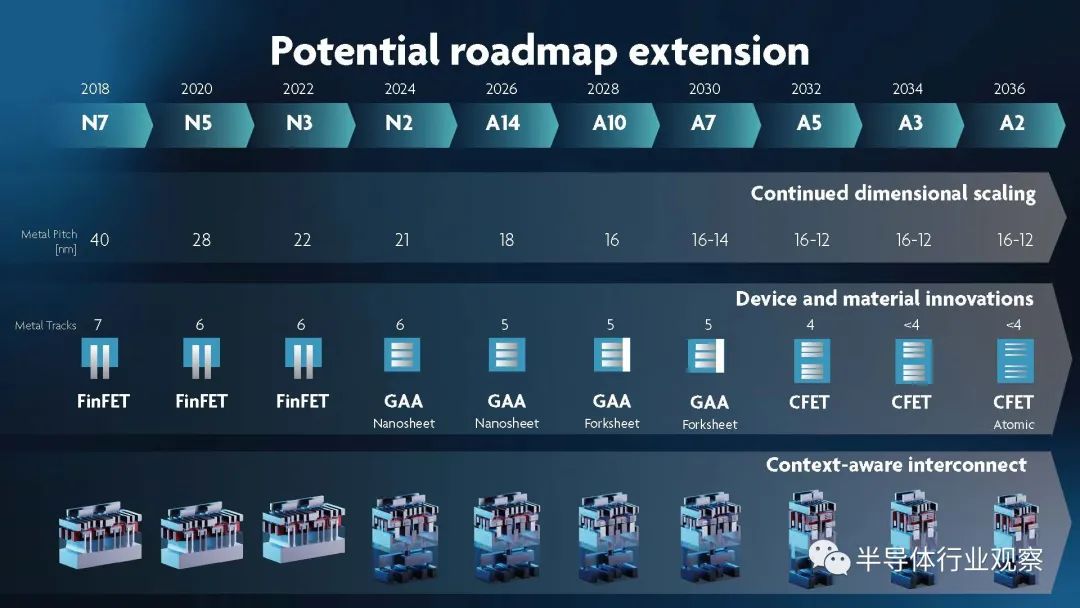

在 Luc Van den hove 的演讲中,他展示了如图 1 所示的路线图幻灯片。

图 1. Imec 路线图

对于某些圈子里关于摩尔定律死亡的所有讨论,Imec 路线图展示了十多年的持续逻辑扩展。

在 N2 节点上,Imec 展示了向 Gate-All-Around (GAA) 纳米片的过渡,三星正在为其 3nm 节点引入 GAA 纳米片,英特尔和台积电宣布用于 2nm(英特尔 20A)的 GAA 纳米片。经过两代纳米片后,Imec 过渡到了 Forksheets。这是纳米片的一种变体,可降低cell的轨道高度。

目前,我不清楚 Imec 的 Forkseheet 提案在设备制造商中的吸引力有多大,因为我真的没有看到除Imec 之外的 供应商在Forksheets 上做任何的工作。在 Forksheet 的两代之后,Imec 开始引入 CFET。供应商们在 CFET 方面做了大量工作,尤其是英特尔和台积电。上一代 CFET 引入了原子级薄片。

在 Geert Van der Plas 的演讲中,关于潜在路线图的更多细节被提出。

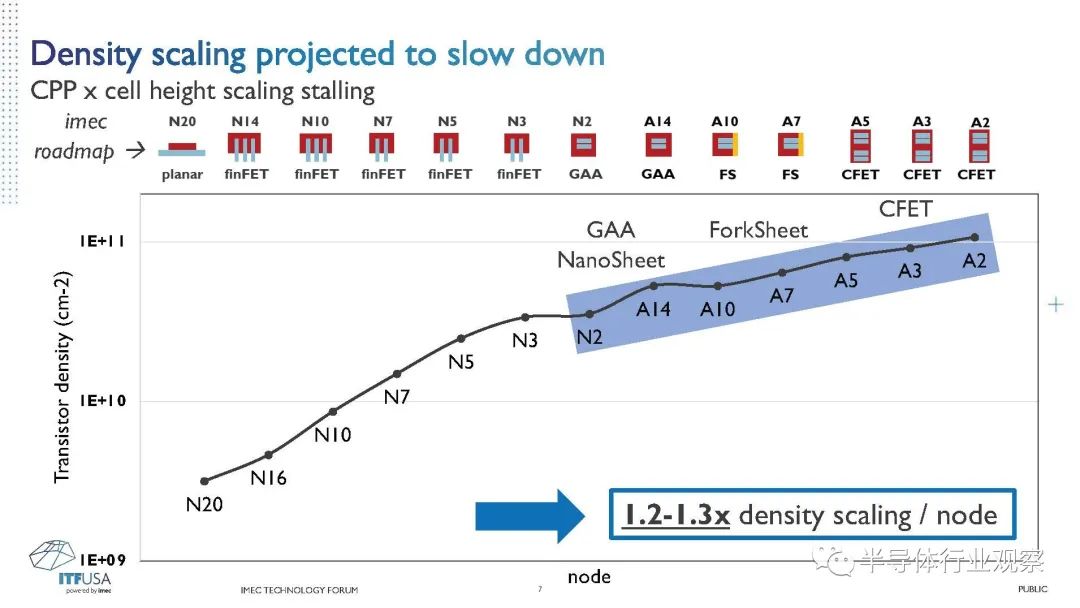

图 2. Imec 路线图晶体管密度

从图 2 中可以看出,尽管密度继续增加,但速率下降到每个节点的 1.2 倍至 1.3 倍。

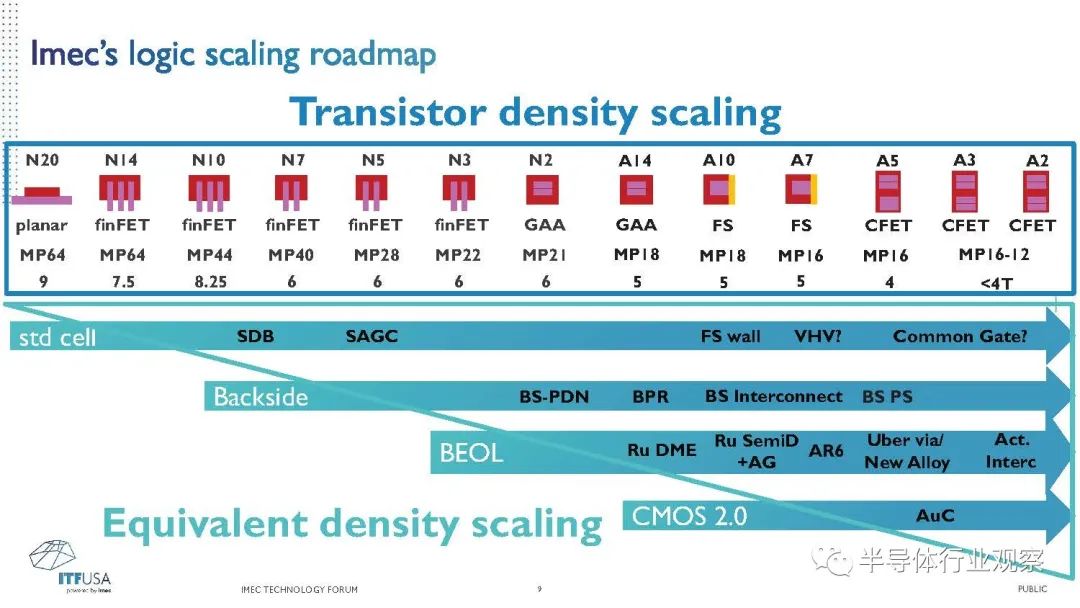

图 3 显示了标准单元、背面、生产线后端和 CMOS 2.0 创新的扩展路线图的一些额外细节。标准单元微缩越来越受到设计-技术-协同优化 (DTCO) 的推动,例如单扩散中断(single diffusion break)、有源栅极上的接触(contact over active gate)、叉板墙(forksheet wall)等。晶圆背面正成为通过背面功率传输进行微缩的关键部分。BEOL 将需要新的材料和图案化技术来支持更密集的设备。

图 3. 晶体管缩放创新

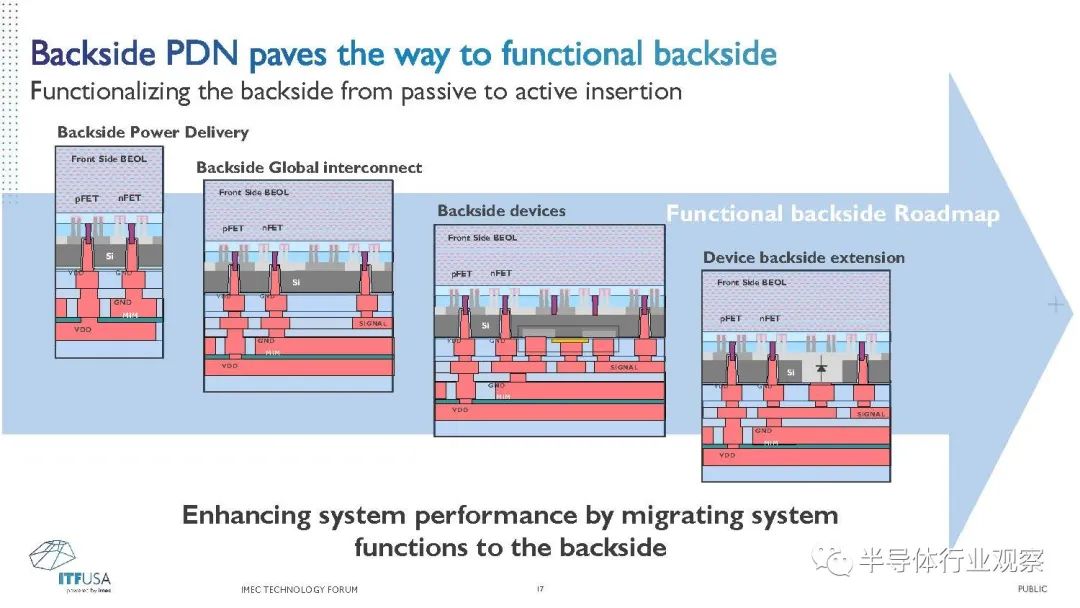

图 4 展示了晶圆背面的一些选项,不仅提供背面功率传输,还可能包含有源器件。

图 4. 背面选项

之后,我参加了由 Linx Consulting 主持的“与制造 3D 设备和结构相关的独特挑战,包括 GAA、3D DRAM 和 3D NAND”技术讲座。

三星的演讲者 Nabil Mistkawi 表示,在 7nm 及以下的drying 可能需要五个步骤来防止图案塌陷(pattern collapse),这确实说明了前沿技术带来的制造困难.

Screen 的 Ian Brown 更详细地介绍了前沿的图案塌陷以及cleaning 和drying挑战。

对于逻辑器件,浅沟槽隔离/鳍的形成和多晶硅后蚀刻是关键步骤。纳米片增加了很多表面,其中一些是隐藏的,水平纳米片释放非常关键。3D NAND 氮化硅去除需要一个快速的过程,但您必须避免二氧化硅沉淀。DRAM 有源和电容器的形成非常关键。

拉普拉斯压力和表面张力会导致 3D 结构坍塌。Spin dryers已被 IPA dryers取代,但它们对表面状态很敏感。今天,在干燥前修改亲水表面使其具有疏水性是最先进的逻辑。

在工业早期,颗粒通过在其下方蚀刻去除,然后过渡到兆声波(megasonics),但在 65nm 以下存在损坏问题。今天使用spin cleaners ,但如果压力过高,它们会造成损坏。目前可用的最佳drying技术是超临界二氧化碳,但由于设备成本的原因,它速度慢且成本高。

最后,应用材料公司的 Aviram Tam 讨论了检测和计量挑战。3D 结构需要一种可以查看结构的技术。高能电子束能够观察结构并表征结构尺寸与深度的关系。随着 EUV 光学覆盖的出现不再足够准确,这里也正在研究 eBeam。

未来二十年,芯片要到这些墙

近日,在 SEMICON West 开始之前,imec 举办了年度国际技术论坛 (ITF)。会上,imec 总裁兼首席执行官 Luc Van den hove 介绍了他对 20 年技术路线图的看法,他表示,该路线图比该行业过去几十年取得的成就更加激进。而imec将利用我们的核心半导体专业知识,通过在半导体技术层面、系统和应用层面的共同创新。

Luc Van den hove首先表示,半导体行业长期以来一直遵循传统的Dennard 缩放推动行业发展,它希望以更低的功耗和更低的成本提供更高的性能和更高的密度。“但这个一维版本的路线图在未来可能已经不够用了,”Luc Van den hove说。“我们将不得不针对特定应用调整我们的设备。”

传统的扩展在功率、性能、扩展和成本方面遇到了多重障碍。而只是基于光刻的微缩也变得越来越难。“它并没有停止,而是变得越来越难。我们习惯于从节点到节点的单个晶体管的性能改进一直在放缓。这就是我们必须进行大规模并行化的原因。”Luc Van den hove强调。

系统性能越来越受到核心处理器和内存之间的数据路径限制的支配,这造成了数据处理限制,尤其是在 AI 应用程序中。“这就是我们所说的记忆墙。内存峰值带宽无法跟上处理器峰值吞吐量,”Van den hove 接着说。

另一面墙是电源墙。“将所有功率输入我们的芯片变得越来越难,而且从每个芯片中提取热量也变得越来越难。因此,我们需要新的冷却技术,”Van den hove 表示。

成本也在爆炸式增长,这是芯片未来面临的另一堵墙,这个问题则需要通过复杂性增加来弥补。

“传统的缩放显然正在击中许多这样的墙,我们将不得不开发技术解决方案来真正拆除这些墙,以使摩尔定律得以延续,”Van den hove 说。

对于这种墙壁拆除,需要多种方法,包括尺寸缩小、新开关/晶体管的开发、第三维度的增加使用以及设计优化的系统级方法。

而按照Van den hove的说法,我们3 年内需要High NA EUV***

Imec 主持了一些关于 EUV 的最早工作,Van den hove 表示,随着 EUV 进入大批量制造,光刻路线图最近经历了“惊人的推动”。“这发生在5纳米节点。这比最初预期的要难得多。这要花更长的时间,但要感谢 ASML 和蔡司等公司的非凡奉献和承诺,”他说。“我们相信当前版本的 EUV 可以扩展到2纳米甚至更远的节点,但要超越这一点,我们将需要下一个版本的 EUV。” 这将需要开发更大的镜头和新的系统平台。光学器件必须符合惊人的规格,直径为 1 米的镜头,其精度将超过 20 皮米。“如果我们将其推断为地球的大小,这意味着我们必须以人类头发粗细的精度来打磨地球。这令人难以置信,令人难以置信,”Van den hove说。“我们预计第一台机器将在明年准备就绪。”

High NA EUV 的引入也将在工艺方面带来许多挑战。“为了以积极主动的方式解决这些问题,我们正在与 ASML 一起建立一个联合High NA 实验室,该实验室围绕第一台原型机建造,将与 TEL 轨道连接,并配备最先进的计量能力。我们这样做是因为及时引入High NA EUV 的挑战将是巨大的,”Van den hove 说。“从第一台 EUV 扫描仪到投入大批量生产,我们花了大约 10 年的时间。对于High NA,我们将有更少的时间,只有三年。为了避免在制造中引入这种情况,我们正在建立一个非常密集的计划,以开发所有关键的支持构建模块,例如掩模技术和使用湿式或干式紫外线抗蚀剂的材料。”

与此同时,Van den hove 还谈了一些设备的创新

Van den hove 描述了几项针对破坏性晶体管架构提出的创新,以实现进一步的扩展,包括由纳米片堆叠构成的环栅设计(gate-all-around),以及一种称为叉片(forksheet )器件的新晶体管概念,其中 N 和 P沟道晶体管靠得更近。“这种forksheet 设备,我们将其视为标准纳米片概念的延伸,我们相信它将在相当于一纳米一代的情况下推出,”Van den hove 说。他还描述了一种将 N 和 P 沟道晶体管堆叠在彼此顶部的选项,称为互补 FET (CFET) 器件。

“很明显,您可以在缩小单元尺寸方面实现另一个非常重要的步骤,但显然是以更复杂的接触方案来接触源极和漏极区域为代价的。但我们相信,我们已经找到了开发的集成方案,可以通过优化外延工艺、图案化工艺以及利用非常复杂的沉积工艺来实现接触结构,从而实现这种晶体管,”Van den hove 说。

其他创新包括减少硅沟道的厚度以减少通道长度。这可以通过使用新材料来实现,如用二维材料、原子平坦的单层(例如,钨或钼的硫化物或硒化物)代替硅。“我们最近展示了使用 300 毫米设备制造的第一批设备,”他说。

Van den hove 表示,持续的尺寸缩放、新的晶体管架构、新材料的引入以及创新的互连架构(埋入式电源轨)相结合将是成功的秘诀。他说:“我们相信,我们可以为未来 8 到 10 代芯片提出路线图——以 2 到 2 年半的节奏推出——这将为我们带来未来 20 年的路线图。

审核编辑:刘清

-

反相器

+关注

关注

6文章

311浏览量

43290 -

FET

+关注

关注

3文章

632浏览量

62948 -

触发器

+关注

关注

14文章

2000浏览量

61132 -

MBPR

+关注

关注

0文章

2浏览量

1489 -

cpp

+关注

关注

0文章

10浏览量

2111

原文标题:关于芯片微缩,imec的新方法

文章出处:【微信号:wc_ysj,微信公众号:旺材芯片】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

光耦技术助力轨道交通智慧化建设

基于4G工业路由器的信息发布系统物联网应用方案

远程户外监控组网方案,工业4G路由器ZR2000

告别繁琐设置,轻松实现4G插卡路由器的快速设置

4G插卡路由器使用指南

4G插卡路由器:便携式网络解决方案的优势与选择

4G路由器的应用场景有哪些

告别传统路由!4G路由器让你轻松上网

4G路由器设置技巧,轻松实现高速畅游互联网

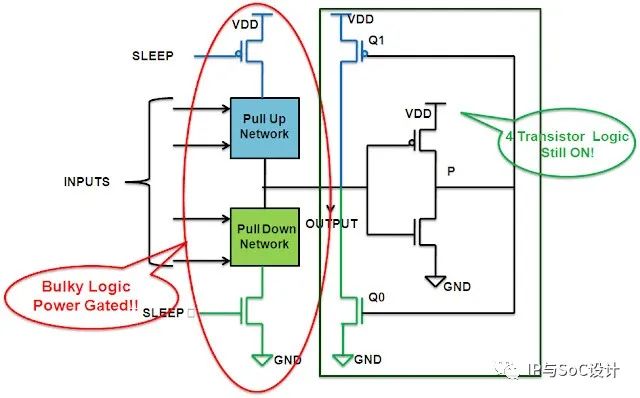

电源门控单元的实现原理

讨论实现4轨道单元的路由技术

讨论实现4轨道单元的路由技术

评论