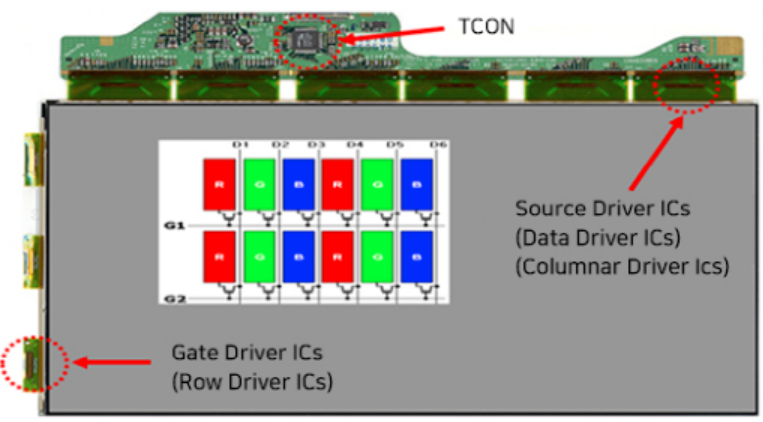

我们的常规设计,一片液晶面板需要两种DDIC:

源极驱动芯片(source driver IC),驱动面板X轴上的信号

栅极驱动芯片(gate driver IC),驱动面板Y轴上的信号

目前,GOA(gate-on-array)技术得到了广泛使用。面板厂商可以通过将栅极电路直接集成到阵列玻璃的边缘来消除Y轴栅极驱动IC。GOA在减少DDIC的使用数量和促进超薄边框方面起到了很大作用。

然而,在X轴上使用源极驱动IC仍然是至关重要的。

之所以要发展此项技术,是因为TFT 的驱动IC里面 Source IC 是要比 Gate IC 贵很多的, 同样的分辨率下 如果是2颗Source+ 1颗Gate的方案 成本比 1颗Source +2颗Gate 方案高很多, 而且在Gate Chanel数比较少的情况下, 还可以做成1+1 的方案, 成本就更低了。

下面我们分别介绍下:

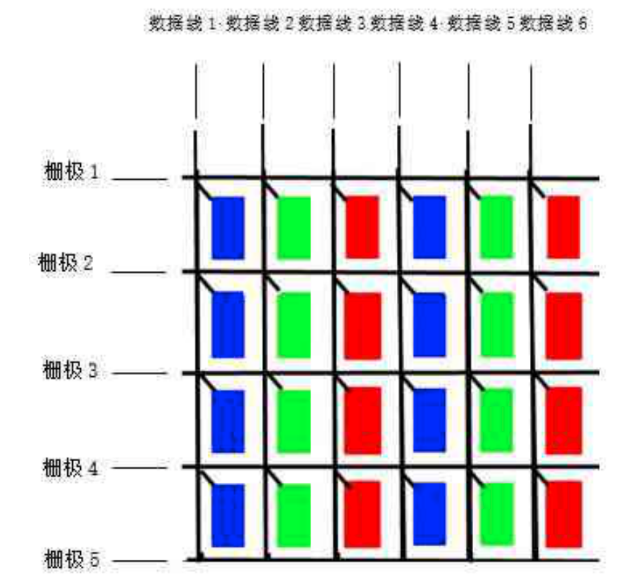

1Sigal-gate

Sigal-gate 驱动架构是红绿蓝子像素横向排列,每一列子像素对应一个数据线,每一行像素对应一个栅极,如下图所示。为最常见驱动结构。

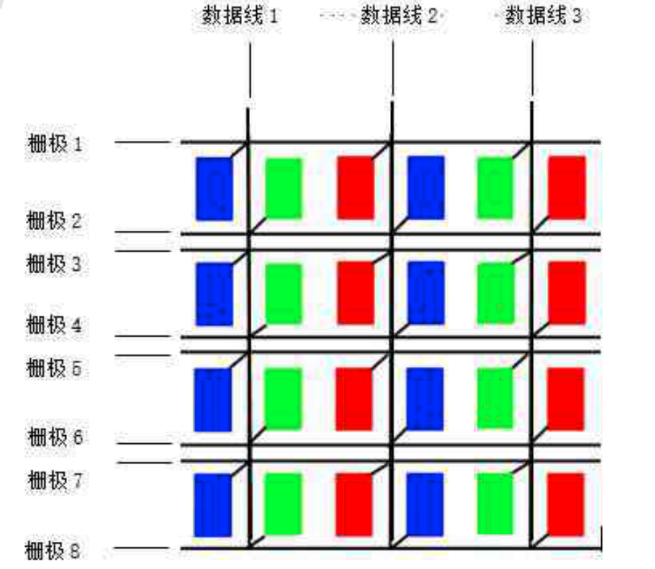

2Dual-gate

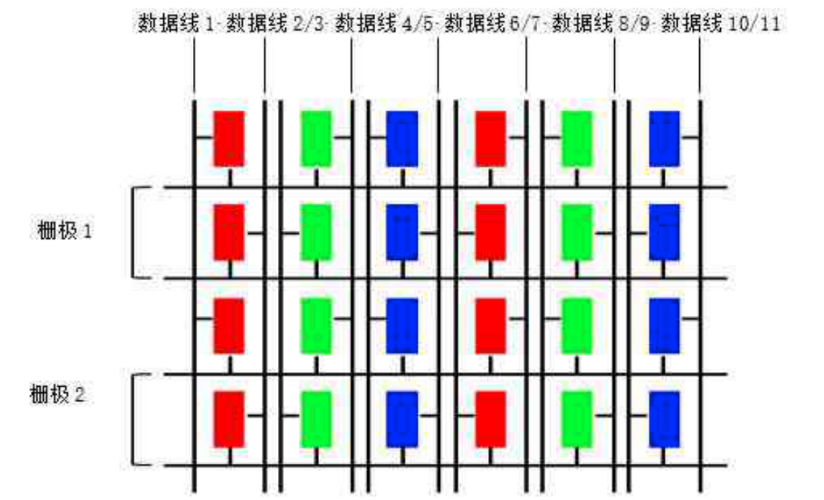

Dual-Gate 驱动架构是红绿蓝子像素横向排列,每两列子像素共用一个数据线,每一行像素对应两个栅极,如下图所示。相比Sigal-gate,数据线数量 (COF 数量)减半,栅极数量 (GOA 级数)加倍

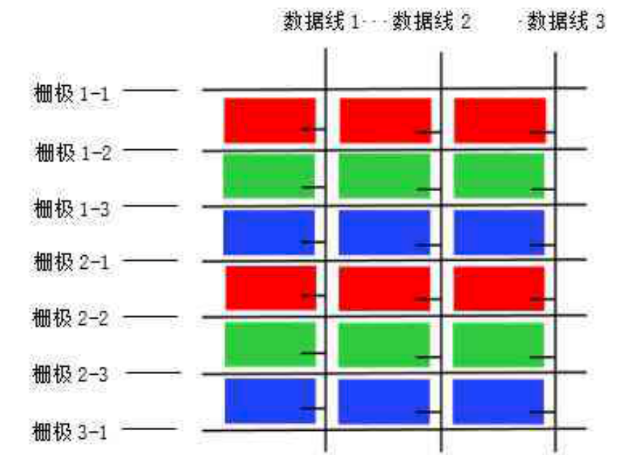

3Triple-gate

Tri-Gate 驱动架构是红绿蓝子像素纵向排列,相当于每三列子像素共用一个数据线,每一行子像素对应三个栅极,如下图所示。相比Sigal-gate,数据线数量(COF 数量)减为 1/3,极数量(GOA 级数)加为信

4HG2D驱动架构

红绿蓝子像素横向排列,每一列子像素使用两个数据线,每两行子像素对应一个栅极,如下图所示相比 Sigal-gate,数据线数量 (COF 数量)加倍,栅极数量 (GOA 级数)减半。

5面板驱动架构的区别与特点

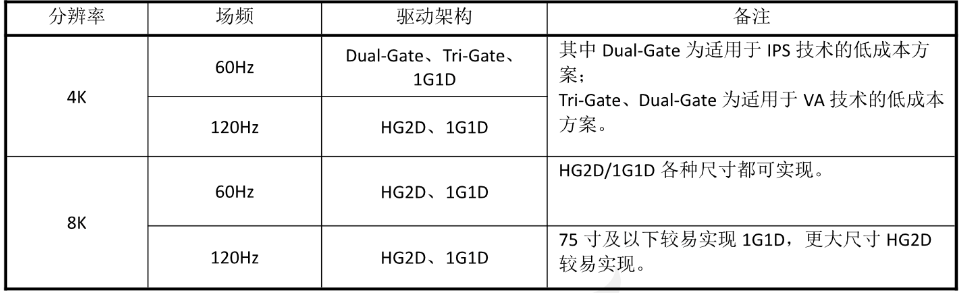

在4K 分辨率的情况下,常用的驱动架构有 Dual-Gate Tri-Gate、HG2D、Sigal-gate 等多种;其中 Dual-Gate和 Tri-Gate 一般是低成本方案,HG2D 则会降低穿透率。

在8K 分辨率的情况下,Dua-Gate 和 Tri-Gate 架构已经无法支持,常用的驱动架构只剩下 HG2D和Sigal-gate(1G1D)。具体如下表所示。

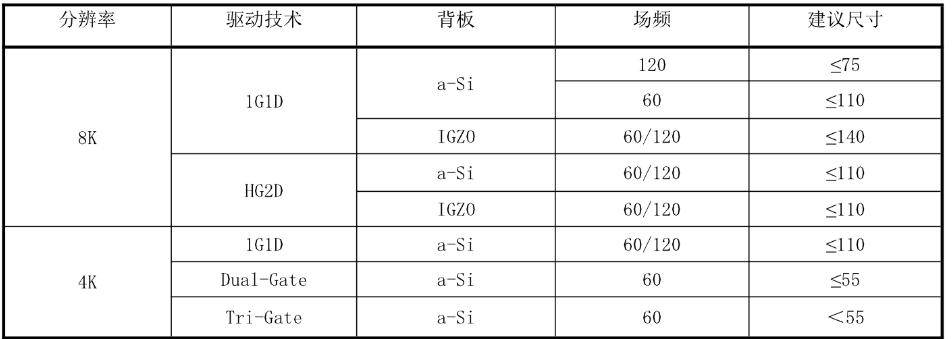

6驱动架构配合面板参数建议

驱动方式与显示面板配合时,背板、场频及尺寸建议如下表所示

7结束语

一般会根据项目的预算及客户的要求进行选择。除了成本方面的取舍,还有就是功耗方面的抉择,Sigal-gate、Dual-gate和Triple-gate的source IC用量逐级减少,相应的IC的功耗也会增加,影响整个模组的功耗;所以若客户对功耗要求严格,需提前做好评估工作。

审核编辑:汤梓红

-

面板

+关注

关注

13文章

1684浏览量

54005 -

驱动IC

+关注

关注

9文章

306浏览量

33898 -

驱动芯片

+关注

关注

13文章

1295浏览量

54844 -

面板驱动

+关注

关注

0文章

3浏览量

2239 -

驱动技术

+关注

关注

0文章

31浏览量

445

原文标题:Sigal-gate、Dual-gate和Triple-gate面板驱动技术

文章出处:【微信号:心植桂冠,微信公众号:心植桂冠】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

异或门(XOR Gate)的基础知识

Design And Application Guide For High Speed MOSFET Gate Drive Circuits

The HIP2030 MCT/IGBT Gate Driver Provides Isolated Control Signals To Switch

请问gate与active的间距的问题

Quartus编译报错Gate Level Simulation Netlist not found

请问6678中gate的用法有哪些?

Split-Gate技术的相关资料推荐

ADUM1420,pdf datasheet (Gate D

双栅型场效应管混频器射频电路图(Dual-gate MOSF

MM54HC11/MM74HC11 Triple 3-Input AND Gate

MM54HC27/MM74HC27 Triple 3-Input NOR Gate

Digital Signal Processing with Field Programmable Gate Arrays

UG-1932: Evaluating the ADuM4146 Single-/Dual-Supply, High Voltage, Isolated SiC Gate Driver with Miller Clamp

ADuM4146: Single-/Dual-Supply, High Voltage, Isolated SiC Gate Driver with Miller Clamp Data Sheet

clock gate时序分析概念介绍

Sigal-gate、Dual-gate和Triple-gate面板驱动技术

Sigal-gate、Dual-gate和Triple-gate面板驱动技术

评论