存储成本不断增加,以及更为现实的计算和带宽失衡困境,使得英特尔二十年前开创的PCI-e(PCI Express)技术逐渐乏力,我们越来越期待一种以内存为中心的、富有变革性的新技术出现,基于PCI-e协议的CXL技术便在此环境下出世。

2019年,英特尔推出了CXL技术,短短几年时间,CXL便成为业界公认的先进设备互连标准,其最为强劲的竞争对手Gen-Z、OpenCAPI都纷纷退出了竞争,并将Gen-Z协议、OpenCAPI协议转让给CXL。 这种业界瞩目的技术究竟有何来头?以及现在业界火热的内存池、内存共享等概念又是什么? 以下将分成上下两篇,和大家一起深度了解CXL技术。

本文要点:

CXL是一个全新的得到业界认同的互联技术标准,其正带着服务器架构迎来革命性的转变。

CXL可以有效解决内存墙和IO墙的瓶颈。

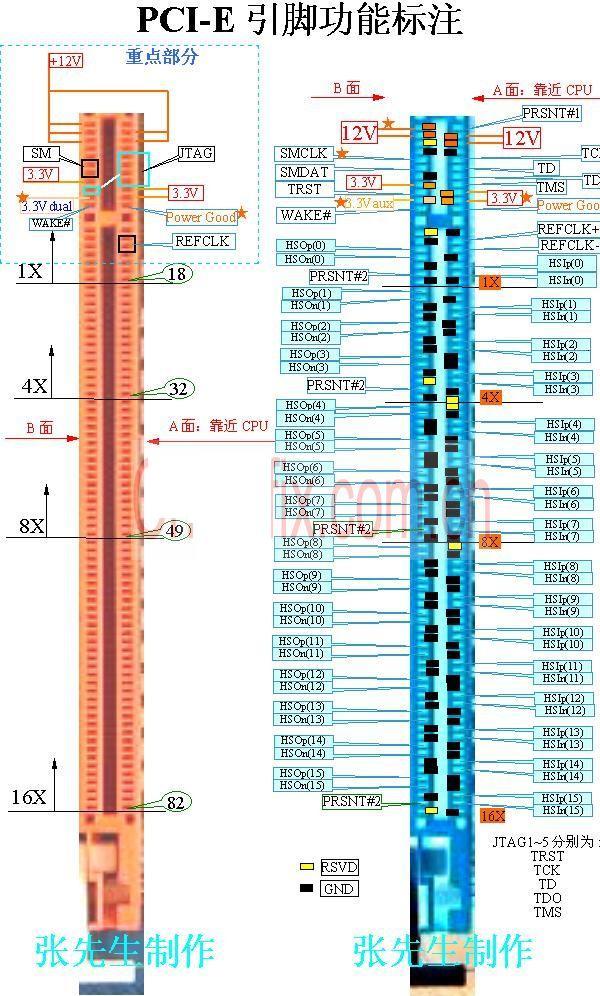

目前,PCI-e技术是当下CXL技术的底层基础,会较早进行迭代升级。CXL可视为PCI-e技术的再提高版本,并且,CXL延伸了更多变革性的功能。

CXL2.0内存的池化(Pooling)功能较好的实现了以内存为中心的构想,CXL3.0则实现Memory sharing(内存共享)和内存访问,在硬件上实现了多机共同访问同样内存地址的能力。

01CXL为何物?

CXL全称为Compute Express Link,作为一种全新的互联技术标准,其能够让CPU与GPU、FPGA或其他加速器之间实现高速高效的互联,从而满足高性能异构计算的要求,并且其维护CPU内存空间和连接设备内存之间的一致性。总体而言,其优势高度概括在极高兼容性和内存一致性两方面上。

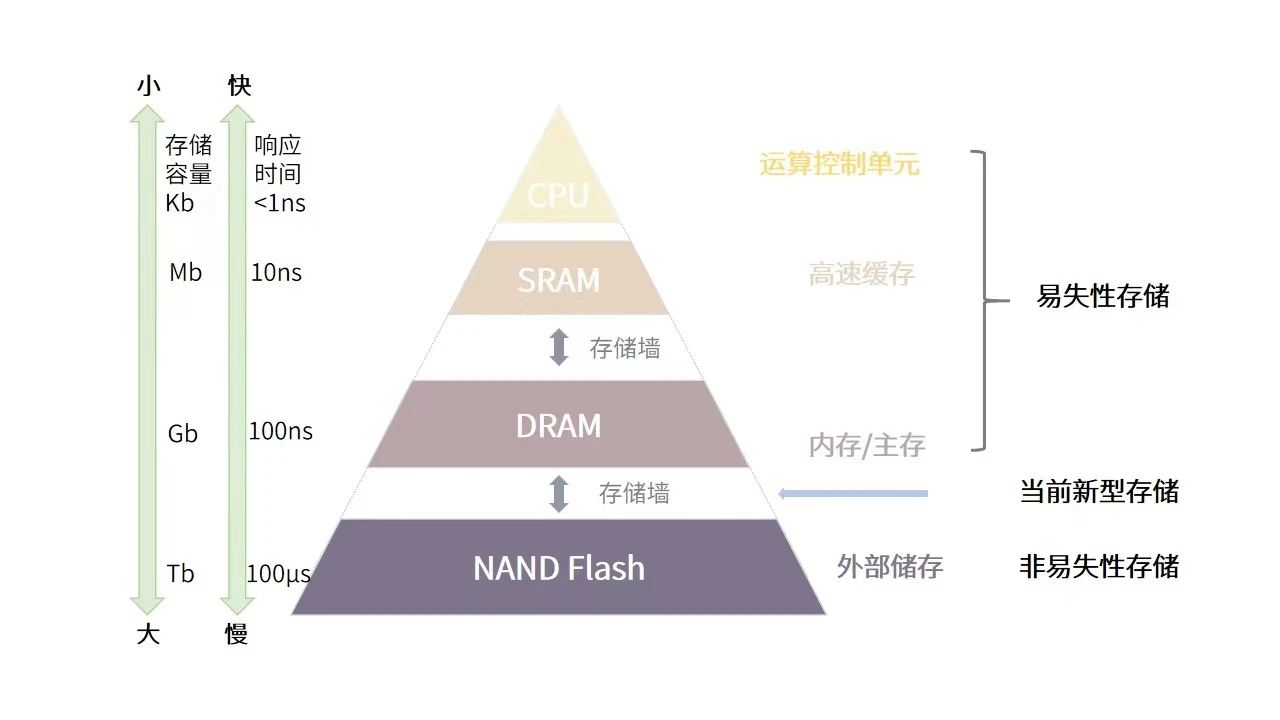

CXL技术之所以值得期待,是因为它提出了一种有效解决当下业界颇为头疼的内存墙和IO墙问题的方式。  △常见的存储系统架构及存储墙(全球半导体观察制图)

△常见的存储系统架构及存储墙(全球半导体观察制图)

内存墙和IO墙现象来源于当前计算架构中的多级存储。如图所示,当前的主流计算系统所使用的数据处理方案,依赖于数据存储与数据处理分离的体系结构(冯诺依曼架构),为了满足速度和容量的需求,现代计算系统通常采取高速缓存(SRAM)、主存(DRAM)、外部存储(NAND Flash)的三级存储结构。

每当应用开始工作时,就需要不断地在内存中来回传输信息,这在时间和精力上都有着较大的性能消耗。越靠近运算单元的存储器速度越快,但受功耗、散热、芯片面积的制约,其相应的容量也越小。如SRAM响应时间通常在纳秒级,DRAM则一般为100纳秒量级,NAND Flash更是高达100微秒级,当数据在这三级存储间传输时,后级的响应时间及传输带宽都将拖累整体的性能,形成“存储墙”。

IO墙则产生于外部存储中,因为数据量过于庞大,内存里放不下就需要借助外部存储,并用网络IO来访问数据。IO方式的访问会使得访问速度下降几个数量级,严重拖累着整体性能,这即是IO墙。

现代处理器性能的不断提升,而内存与算力之间的技术发展差距却不断增大。业界数据显示,在过去的20多年中,处理器的性能以每年大约55%速度快速提升,而内存性能的提升速度则只有每年10%左右。并且,当代内存容量扩展面临着摩尔定律的压力,速度在逐年减缓的同时,带来的则是成本的愈发高昂。随着大数据AI/ML等应用爆发,以上问题已经成为制约计算系统性能的主要因素。

02从CXL1到CXL3,

内存池和内存共享的奇妙构想

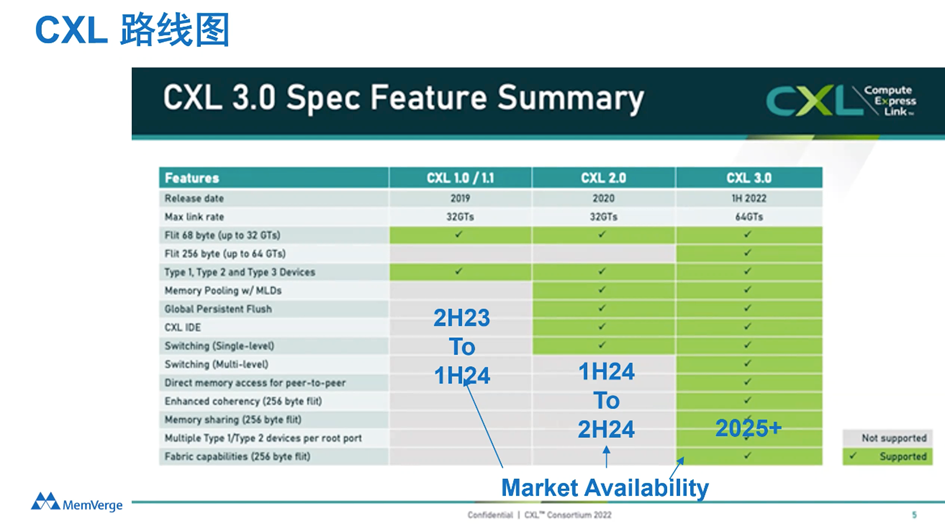

作为一项崭新的技术,CXL发展非常可谓非常迅速,过去四年时间CXL已经发表了1.0/1.1、2.0、3.0三个不同的版本,并且它有着非常清晰的技术发展路线图,业界也对它的未来充满期待。

△图片来源:CXL联盟

CXL1.1直球式连接,带来容量和带宽的拓展

在2019年,CXL的第一个版本CXL1.0/1.1诞生,其直面内存墙和IO墙瓶颈的直球式打法给业界留下了深刻的印象。CXL1.1起初解决的问题还只是单机设备的问题,主要是对一台服务器里的内存容量和带宽进行扩展(Memory Expansion)。

CXL在创立之初便支持三种协议,分别是CXL.io,CXL.cache,CXL.mem。CXL.io是PCIe5.0的增强版本,运行在PCIe总线的物理层上,CXL.cache用于一致的主机缓存访问,CXL.mem则用于主机内存访问。正如CXL1.0和1.1标准中定义的那样,这三种方法构成了连接主机和设备的新方法的基础。

创新来讲,CXL引入了Flex Bus端口,可以灵活的根据链路层协商决定是采用PCIE协议还是CXL协议。

这让我们更好的理解CXL和PCI-e的关系,正因为CXL较高的兼容性,更容易被现有支持PCI-e端口的处理器(绝大部分的通用CPU、GPU 和 FPGA)所接纳,因此,英特尔将CXL视为在PCIe物理层之上运行的一种可选协议,也就是说PCI-e的互联协议没有被完全抛弃,并且英特尔还计划在第六代PCI-e标准上大力推进CXL的采用。

从CXL1.0/1.1、PCIe5.0、CXL2.0以及PCIe6.0CXL3.0的发展轨迹,我们也可以清晰看出CXL和PCI-e的关系。PCI-e技术作为CXL技术的底层基础,会更早进行迭代升级。CXL可视为PCI-e技术的再提高版本,并且,CXL延伸了更多变革性的功能。 从CXL2.0开始,该技术就超出了单机的范畴,并衍生出了内存池的概念。

CXL2.0内存池带来的变革

鉴于CXL标准诞生并不久,目前,CXL2.0是市场最为关注的焦点。

在CXL1.0和1.1的基础上,2.0版本增加了热插拔(Hot Plug)、安全升级、持久内存(Persistent Memory)、Telemetry和RAS的支持,但最为重要的功能,还是可以改变服务器业界生态构型的Switching,以及它带来的加速卡(AI、ML和Smart NIC)和内存的池化(Pooling)。

关于设备的Pooling(池化),业界也曾进行过许多的构想与技术尝试,想要将各类资源或是数据放入一个共享的池子按需提取,如FaceBook致力于分离(disaggregate)和池化(pool)内存,IBM的CAPI和OpenCAPI、英伟达的NVLink和NVSwitch、AMD的Infinity Fabric、赛灵思的CCIX,以及HPE和戴尔提供支持Gen-Z。因为各种各样的原因,上述技术并没有很好的发展开来。直到CXL2.0的池化操作变成现实,业界再次燃起希望。

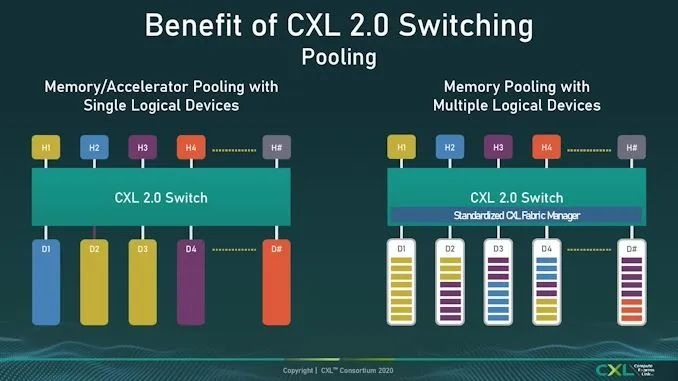

CXL1.1还只限于单一Node,是一种CPU到CPU,或者CPU到PCIe设备的cache一致性互联。2.0技术加入了一层(Single Level)的Switch(想一想PCIe的Switch),实现了多个设备连接到一个root port上,为后面的池化打下了技术基础。

△图片来源:CXL联盟

上图的H1到H4到Hn指的是一个个不同的主机(Host),也就是一个个服务器(Server),它可以通过CXL Switch连接多个设备,底下的D1、D2、D3、D4指的是不同的内存,也是通过CXL Switch连到上层的主机里。图中不同的颜色代表设备的拥有者,如D1属于H2,D2和D3属于H1。SLD一个设备只能被分配到一个Hos上。

在这套框架之下,它使得Memory Polling(内存池)成为可能,你可以跨系统设备实现共享内存池,这就增加了很多的灵活性。比如,如果有机器内存不够时,就可以灵活地在这个池子里寻找内存空间;如果这台机器不需要这些内存了还可以随时还回来。也就是说越靠近CPU的存储器(如DRAM)将被用来处理更为亟需的工作,这无疑将大大提高内存的使用率,或者降低内存的使用成本。

CXL3.0共享内存时代的到来

CXL 3.0是在2022年8月份发布的新标准,其在许多方面都进行了较大的革新,首先,CXL3.0建立在PCI-Express 6.0之上(CXL1.0/1.1和2.0版本建立在PCIe5.0之上),其带宽提升了两倍,并且其将一些复杂的标准设计简单化,确保了易用性。

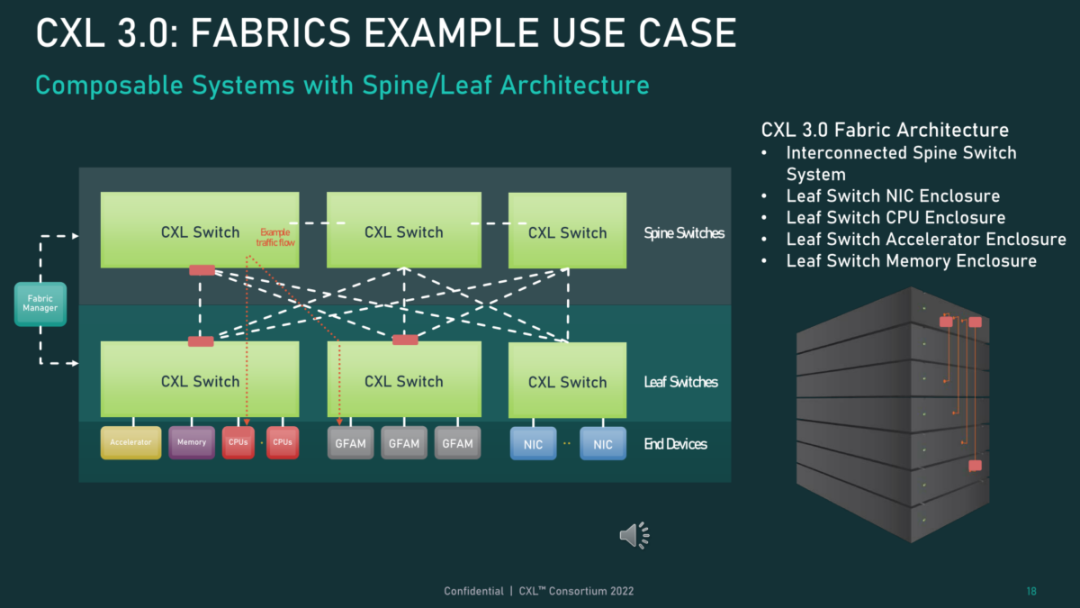

△图片来源:CXL联盟

最为关键的革新还在于物理和逻辑层面的升级,在物理层面,CXL3.0将每通道吞吐量提升了一倍,达到64GT/s。逻辑层面上,CXL3.0扩招了标准逻辑能力,允许更复杂的连接拓扑,以及一组CXL设备内可以灵活实现Memory sharing(内存共享)和内存访问。比如,它可以使得多个Switch互相连接,可以使得上百个服务器互联并共享内存。

Memory sharing是非常大的一个亮点,这种能力突破了某一个物理内存只能属于某一台服务器的限制,在硬件上实现了多机共同访问同样内存地址的能力。可以说,CXL的内存一致性得到很大的增强,因为此前的CXL2.0只能通过软件实现Memory sharing。

CXL来势汹汹,在CXL技术推出的那一年,CXL联盟也随之成立,由英特尔牵头,联合阿里巴巴、戴尔EMC、Facebook(Meta)、谷歌、HPE、华为和微软共同建立,随后AMD、Arm加入其中。

近两年,CXL联盟扩展出超过165个成员,几乎涵盖了所有主要的CPU、GPU、内存、存储和网络设备制造商。而在技术上,2022年,Gen-Z联盟、Open CAPI联盟均确认将所有技术规格和资产转让给CXL,确保CXL作为行业标准向前推进,对于业界而言,这是一个非常伟大的选择。

03从存储变革看CXL的未来意义

以内存为中心的构想由来已久,CXL对于未来的变革目前还无法想象,但是上世纪90年代,存储也经历了一场类似的变革,这或许可以帮助我们更好的理解它。

上世纪90年代之前,存储指的就是硬盘,由IBM研发的350 RAMAC的诞生标志着人类正式进入了硬盘时代。90年代初期,一个叫做Fiber Channel的网络出现,它使存储从服务器里独立出来,变成一个与计算分离的、可以独立扩展与管理的系统,这就是人们熟知的SAN系统。

随后的存储市场更是出现了各式各样的网络共享存储,这场技术革命,使得存储从一个简单的器件行业变成了一个软件和系统行业,并随着诞生了“存储软件”概念。

1995年,集合了软件和硬件的SAN系统开始出现,2000年左右,第一代NAS开始落地。不止的SAN系统,在这段技术革命中,也涌现了一大批成功的领导者公司,包括EMC、NetApp、Veritas、PureStorage等等,存储软件和系统迅速成长壮大为一个庞大的市场。

现在的内存和30年前的硬盘存储极为相似。

现在的内存还只是服务器里的一个设备,随着CXL的出现,内存可以和计算进行分离,就像90年代存储和计算分离一般,这意味着,内存也有望独立成为一个崭新的系统,并赋予更多的功能。

或许是看到了CXL潜力,2022年8月24日,JEDEC固态技术协会和Compute Express Link(CXL)联盟宣布签署合作备忘录开展合作,该协议表明将形成一个联合工作组,以提供一个促进信息、要求、建议和请求的交流和共享的论坛,目的是这种信息交流将有助于每个组织制定的标准相互增强。

业界表示,与具有380个引脚的DDR5接口提供32GB/s带宽相比,CXL内存控制器可以提供相同或更高的带宽,利用x8或x16CXL通道分别提供32GB/s或64GB/s带宽。CXL串行连接存储器可用于缓解当今解决方案的带宽限制。总体来看,CXL与JEDEC在DDR方面的合作将给内存行业带来新的转机。

此外,据TrendForce集邦咨询此前研判,CXL(Compute Express Link)原是希望能够整合各种xPU之间的性能,进而优化AI与HPC所需要的硬件成本,并突破原先的硬件限制。

CXL的支援仍是以CPU为源头去考虑,但由于可支援CXL功能的服务器CPU Intel Sapphire Rapids与AMD Genoa现阶段仅支援至CXL 1.1规格,而该规格可先实现的产品则是CXL存储器扩充(CXL Memory Expander)。

因此,TrendForce认为,在各种CXL相关产品内,CXL存储器扩充将成为前驱产品,其产品也与DRAM最为相关。

04结语

CXL时代将会很快到来,业界消息显示,2024年上半年,CXL1.1和CXL2.0可能会有落地产品,CXL3.0的落地还需要更长时间。现阶段,相关的合作伙伴也在找相应的厂商对一些工程样品搭建环境进行开发测试。

目前,各大企业动态频频,《大内存时代,振奋人心的CXL技术》下篇将会对业界大厂在CXL上的布局以及CXL技术现存的一些短板进行阐述。

审核编辑:刘清

-

DRAM

+关注

关注

40文章

2313浏览量

183463 -

存储器

+关注

关注

38文章

7487浏览量

163808 -

NIC

+关注

关注

0文章

23浏览量

12420 -

PCI-e

+关注

关注

0文章

11浏览量

6248

原文标题:大内存时代振奋人心的CXL技术(上)

文章出处:【微信号:算力基建,微信公众号:算力基建】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

在FPGA上设计PCI-e Gen2.0和PCI-e Gen3.0有什么不同

解决台式机PCI-E 1X不够难题 :乐扩PCI-E 1X转2口PCI-E 1X扩展卡

RapidIO与PCI-E哪个更适合通信

PCI PCI-X PCI-E介绍 精选资料分享

一窥CXL协议

PCI-e总线FPGA开发板资料说明

浅谈显卡PCI/AGP/PCI-E接口的区别

Intel的核显真的占用了CPU的4根PCI-E通道吗

pci-e插槽的规格有哪些 各个版本的pci-e的规范区别

基于PCI-e协议的CXL技术

基于PCI-e协议的CXL技术

评论