在某些协议的应用场合,需要对高速收发器的多个通道之间实现同步,通道间的相位延迟小于一定数量的UI,甚至小于1个UI。然而大多数情况下,高速收发器的相位延迟并不是固定的,导致上电后通道间会产生多个UI的相位延迟,并且每次上电后延迟的UI数量是随机的。

本文将介绍两种实现相位对齐的方法,可适用于US系列和US Plus系列的GTH和GTY器件。

1TX Buffer Enable

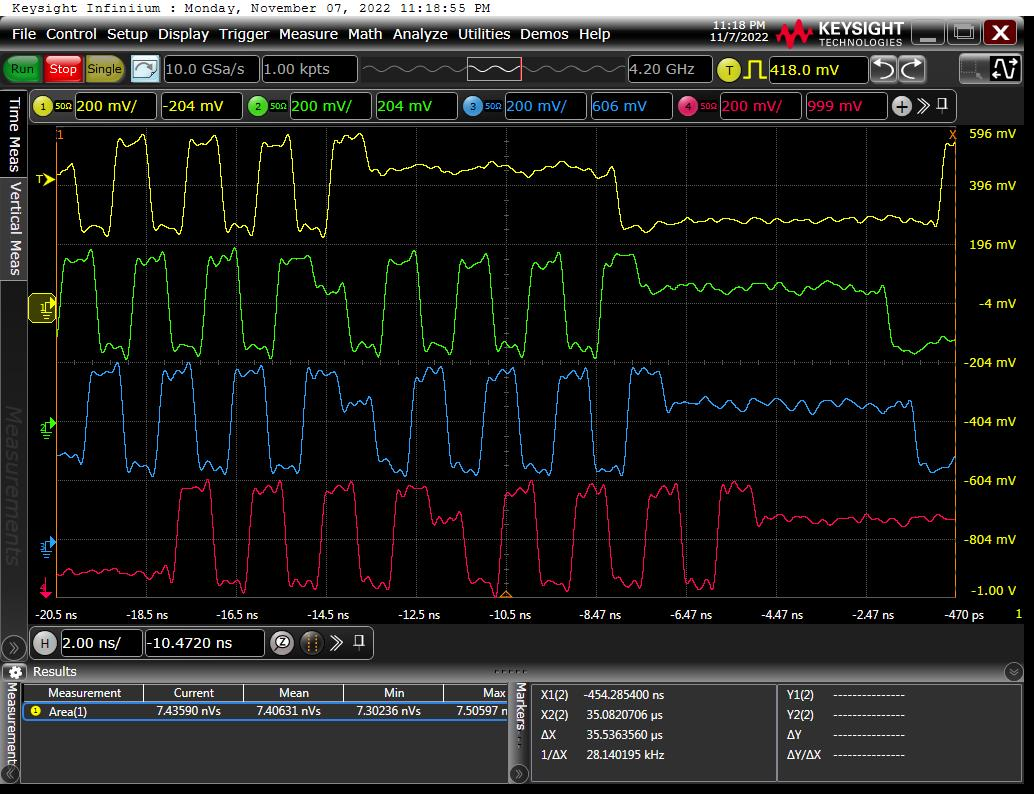

当TX Buffer被使能时,可以通过TXBUFSTATUS的Bit0(Half Full)的状态和TXPIPPM的调整实现TX通道同步。上电后TX通道间的相位和TXBUFSTATUS都处于随机状态,相位超前与延迟以及超前和延迟的UI数量都是不确定的,见下图:

1)TXPIPPM调整方法

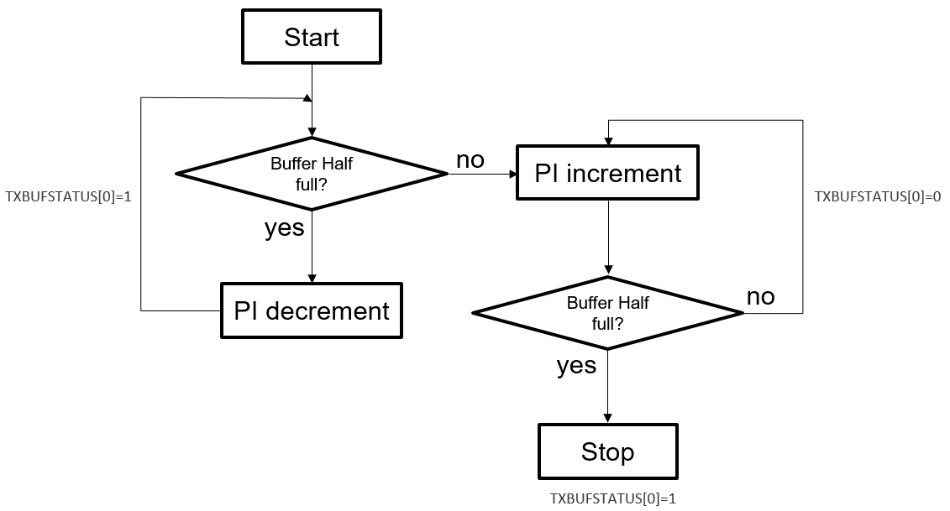

参照Article 70869的方法对每个通道做TXPIPPM调整:当TXBUFSTATUS[0]的状态为1时,通过调整TXPIPPMSTEPSIZE减少PI值;当TXBUFSTATUS[0]的状态为0时,通过调整TXPIPPMSTEPSIZE增加PI值。TXPIPPMSTEPSIZE是一个5bits端口,其中TXPIPPMSTEPSIZE[4]控制PI值增加或减少,TXPIPPMSTEPSIZE[3:0]为PI值增加或减少的数值。调整流程按下图所示:

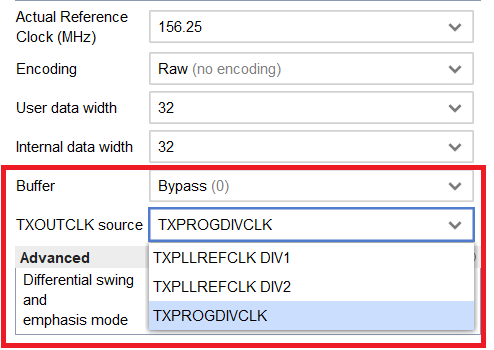

2)TXOUTCLK的时钟选择

TXOUTCLK的时钟不能选择TXOUTCLKPMA和TXOUTCLKPCS,对应TXOUTCLKSEL不能设置为 “001” 或 “010” ,建议选择TXPROGDIVCLK时钟作为TXOUTCLK,否则会导致调整无效的情况,即不管如何调整TXPIPPM控制器,TXBUFSTATUS都始终处于常高或者常低的状态。

3)TXPIPPM控制器端口和时序TXPIPPM控制器相关的端口如下所示:

| 信号名称 | 功能描述 |

| TXPIPPMEN | 置1开启TXPIPPMSTEPSIZE更新TX PI参数 |

| TXPIPPMOVRDEN | 置0为正常模式,置1时通过DRP端口设置PI Code |

| TXPIPPMPD | 置1开启TXPIPPM的Power Down,正常使用置0 |

| TXPIPPMSEL | 置1使能TXPIPPM控制器,置0为关闭控制器 |

| TXPIPPMSTEPSIZE [4:0] | Bit [4] 控制PI Code增减,Bit [3:0] 控制每次增减的步长 |

对于不同器件,TXPIPPM的时序略有不同,详细可参考对应GT的User Guide。

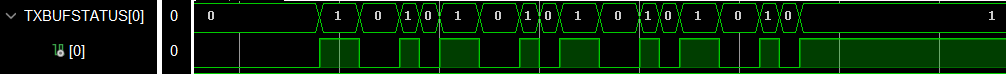

4)TXBUFSTATUS的状态变化

TXBUFSTATUS在调整过程中会有一段时间呈现出反复翻转的状态,此时TXPIPPMSTEPSIZE的设置需要一直保持之前的状态直到TXBUFSTATUS的状态稳定后再置为0。

5)调整完成后的对齐效果

此方法也可以在不同的GT QUAD中实现TX相位对齐,也可以用于控制PCB Deskew控制。

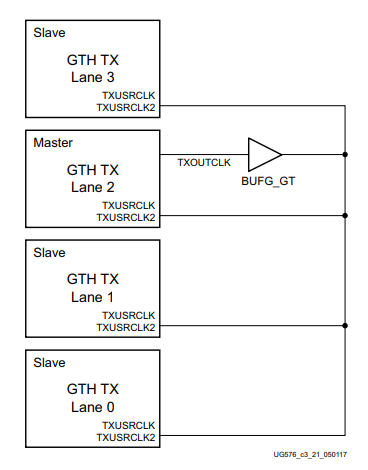

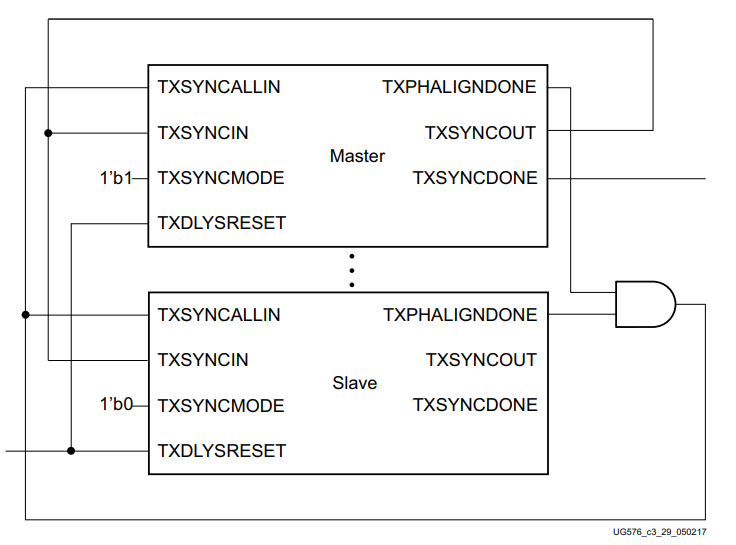

2TX Buffer Bypass

当TX Buffer被旁路时,在TX相位对齐电路工作之前,每个通道XCLK的相位差是随机的。TX相位对齐的基本原理是Master通道产生TXOUTCLK作为公共时钟通过BUFG_GT与各通道的TXUSRCLK和TXUSRCLK2相连,并且所有通道的XCLK时钟都设置为TXUSR时钟(如下图所示),这样就可以与Master通道产生的公共时钟对齐,从而实现每个TX通道数据的相位对齐,对齐后仅存在各通道与公共时钟微小的相位差。

TX相位对齐分为自动和手动两种模式,一般常用自动模式。多通道相位自动对齐需要设置以下参数:

1)TXOUTCLK时钟选择

在Basic菜单将TX Buffer设置为Bypass模式,Wizard会自动将XCLK的时钟选择为TXUSR。此时,TXOUTCLK只能选择为TXPLLREFCLK_DIV1、TXPLLREFCLK_DIV2或TXPROGDIVCLK。

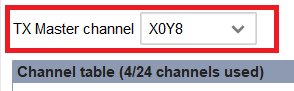

2)定义Master通道

Physical Resources中选择Master通道位置,对应产生公共时钟,推荐使用GT column中间位置的通道作为Master。Wizard会将TXSYNCMODE置1代表Master通道,其余通道置0代表Slave通道。四个GT通道需要使用同一个Reference Clock输入。

3)Structural Options将TX Buffer Bypass 的相关端口勾选。

| 信号名称 | 功能描述 |

| txdlysresetdone_out: | 指示TX相位对齐复位完成 |

| txphinitdone_out: | 指示TX相位对齐初始化完成 |

| txphaligndone_out: | 指示TX相位对齐完成,当txdlysresetdone_out置1后的第二个上升沿表示相位对齐完成。 |

在TX相位对齐完成前,即txphaligndone_out第二个上升沿到来前,需要关闭TXPIPPM调整的功能,将TXPIPPMSEL端口置为0。

4)GT内部连接关系

TX Buffer Bypass多通道相位自动对齐的内部端口连接如下图所示,Wizard会在后台自动生成连接关系,手动模式的连接方式可以参考相应的GT用户手册。

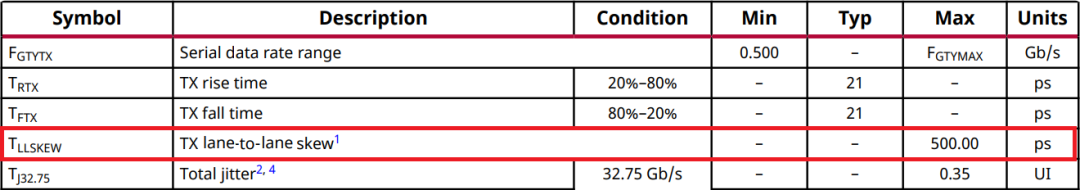

实际测试结果表明,在txphaligndone_out置1后,Channel0与Channel1-Channel3存在微小的相位差,测量结果如下表所示:

| 通道 | 相位延迟时间 |

| Lane0-Lane1 | 21.5ps |

| Lane0-Lane2 | -181.9ps |

| Lane0-Lane3 | -192.4ps |

参照Datasheet的描述,同一Reference Clock在开启相位对齐并且TX输出为最大速率时的TX lane-to-lane Skew最大值为500ps。

如果要实现更高精度的相位对齐,可再配合使用TXPIPPM控制器(TX Phase Interpolator PPM Controller)调整。

5)调整完成后的对齐效果

注意:TX Buffer bypass的相位对齐仅限于同一个Column的通道。如果器件有左右两组Column,无法实现左侧通道与右侧通道的相位对齐。

审核编辑 :李倩

-

收发器

+关注

关注

10文章

3489浏览量

106325 -

控制器

+关注

关注

112文章

16490浏览量

179837

原文标题:实现高速收发器TX通道间相位对齐的方法

文章出处:【微信号:Hack电子,微信公众号:Hack电子】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

实现高速收发器TX通道间相位对齐的方法

实现高速收发器TX通道间相位对齐的方法

评论