之前在Trion上一直强调驱动PLL要走pllin管脚。但是如果在硬件设计之时没有注意而把PLL输入管脚放置在普通GPIO也不是完全没有办法。

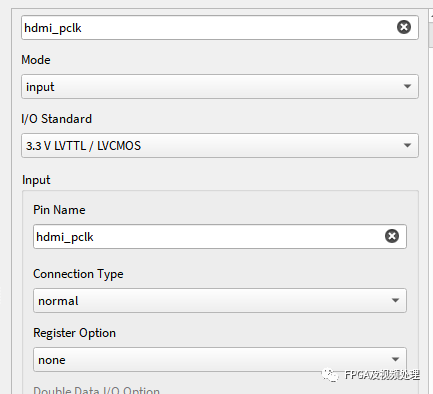

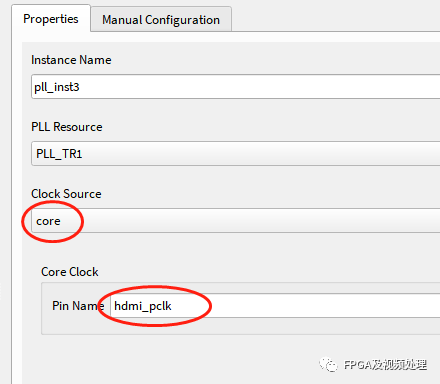

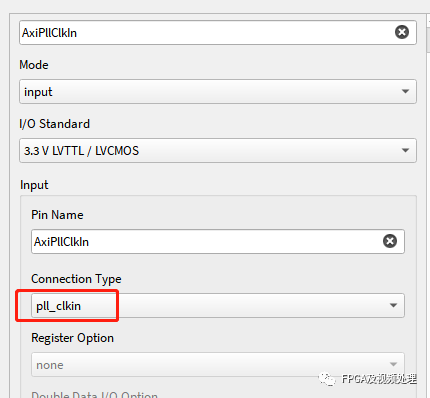

(1)如果放在了GCLK上,Connection Type设置成GCLK,PLL的时钟源设置成Core;

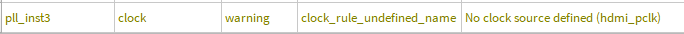

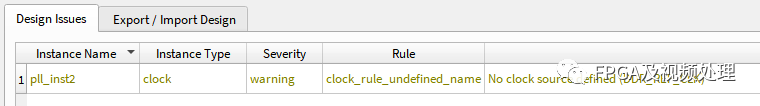

(2)如果放在了普通GPIO上,那Connection Type只能设置成Normal,同样PLL的时钟源设置成Core;不过会有警告信息clock_rule_undefined_name:No clock source defined(xxx)

Trion验证

有警告信息clock_rule_undefined_name:No clock source defined(hdmi_pclk )但是不用管。照用不误。

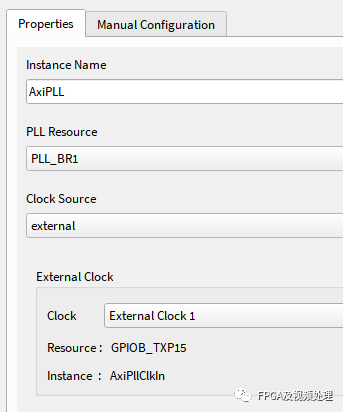

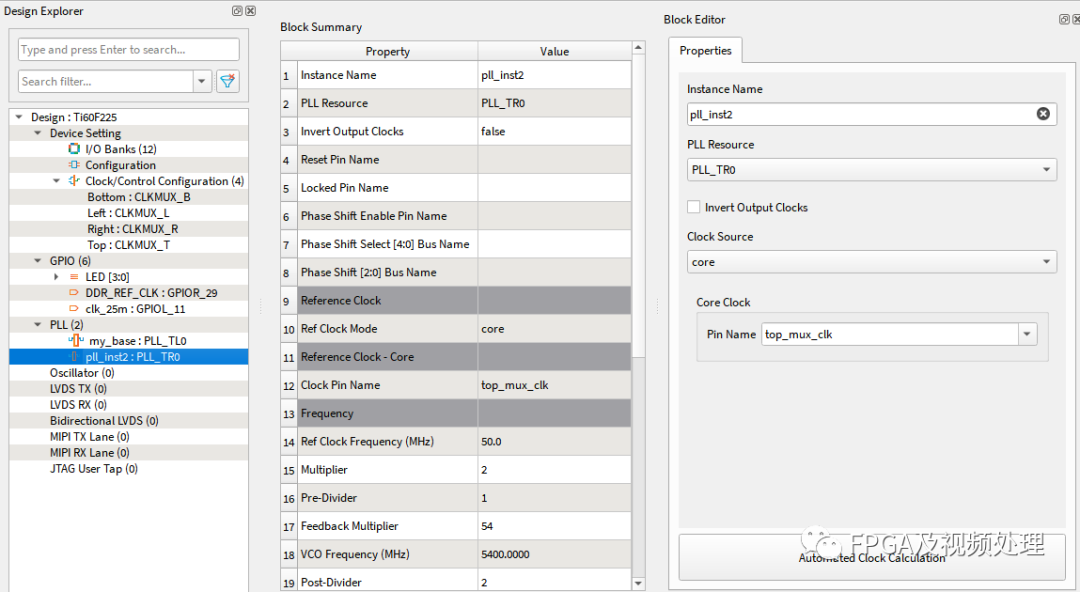

在钛金上同样可以这样设置。

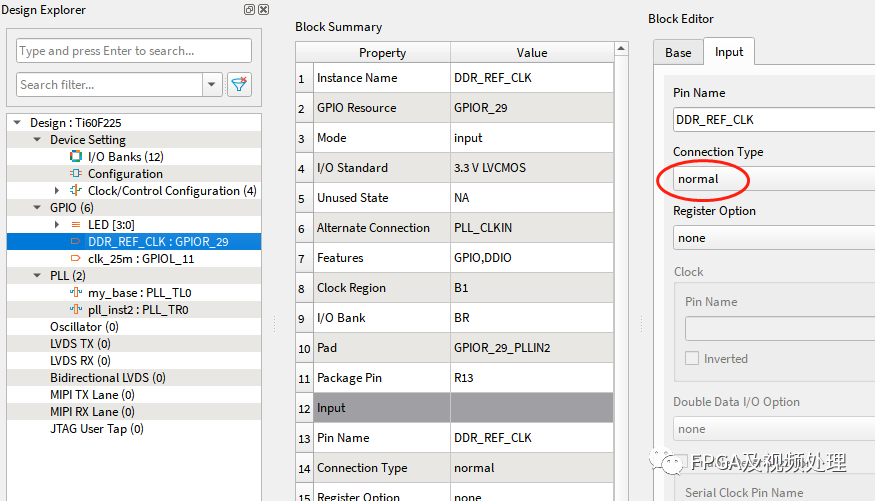

把DDR_REF_CLK设置为normal。

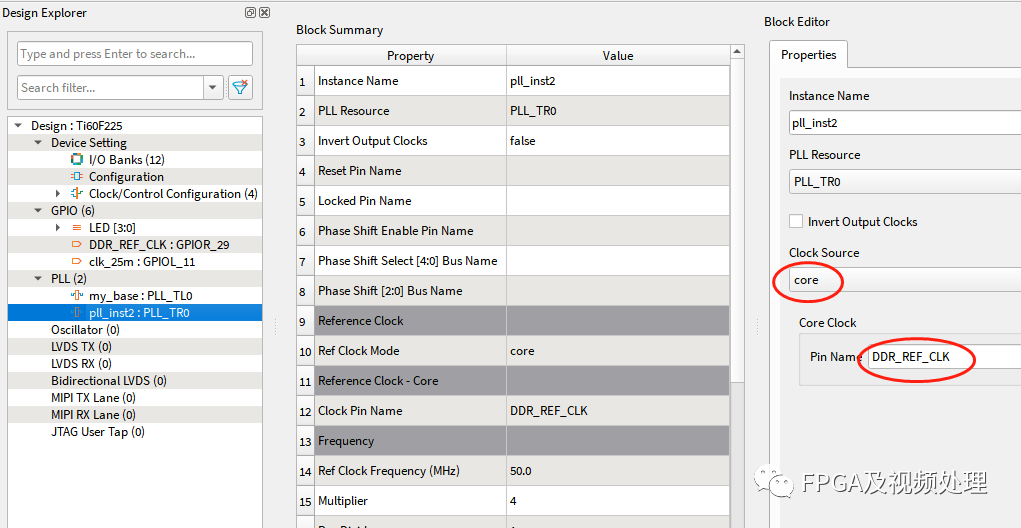

把PLL的参考修改成Core,并输入时钟名DDR_REF_CLK。

有警告信息clock_rule_undefined_name :No clock source defined(DDR_REF_CLK),但是不用管。照用不误。

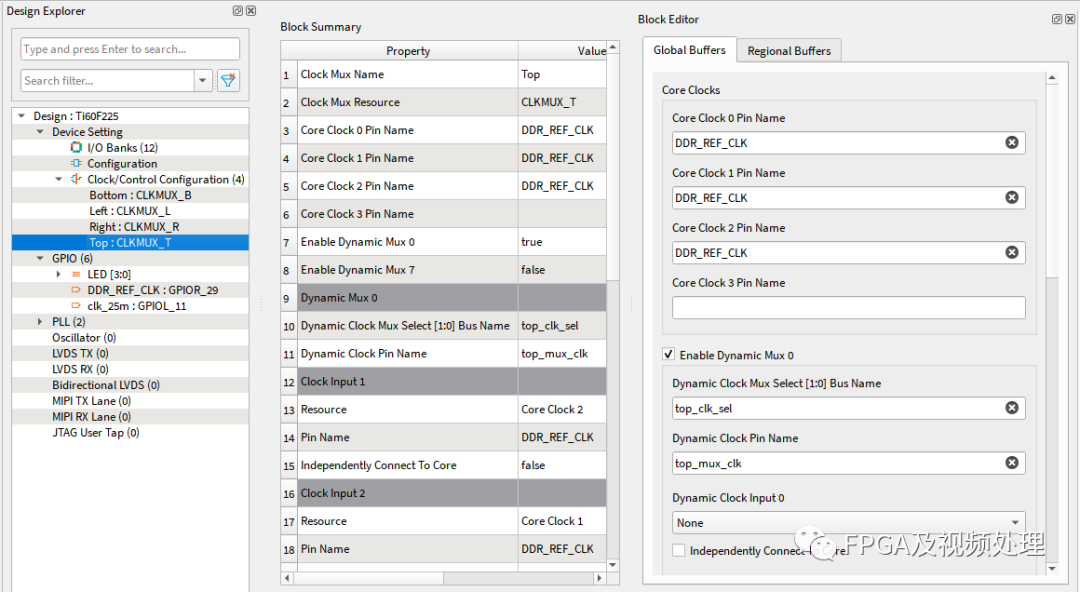

方法二:通过clkmux驱动PLL

审核编辑:刘清

-

HDMI

+关注

关注

32文章

1712浏览量

152031 -

pll

+关注

关注

6文章

777浏览量

135199 -

GPIO

+关注

关注

16文章

1205浏览量

52162

原文标题:GPIO驱动PLL的

文章出处:【微信号:gh_ea2445df5d2a,微信公众号:FPGA及视频处理】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

求助, nidec pll 驱动电机

AD9957在使用内部pll后pdclk无输出

如何将PLL / BUFPLL保留在我的项目中

是否可以通过软件在驱动程序中交换/更改PLL?

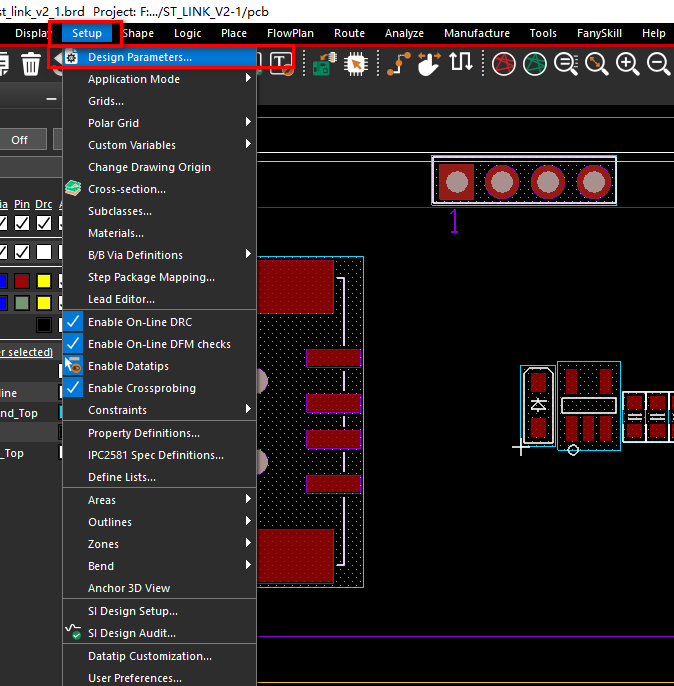

PCB板上多长的走线才是传输线?

在FPGA上编写的通过SPI总线配置外部PLL芯片AD9518和ADC9268的程序

在Trion上驱动PLL走pllin管脚

在Trion上驱动PLL走pllin管脚

评论