有没有同学好奇,作为模拟芯片设计师,几乎都在用CMOS工艺,大部分电路也是用的MOSFET,很少用BJT去设计大规模电路,那么,到底应该对BJT这种device掌握到什么level呢?

其实我也不能下定论,我就说说我的掌握程度吧。

当然BJT基本的工作原理肯定要掌握的。

本文谈一谈BJT这个device、以及模拟IC设计师眼中对BJT的了解程度(只用过CMOS工艺的模拟IC设计师)。

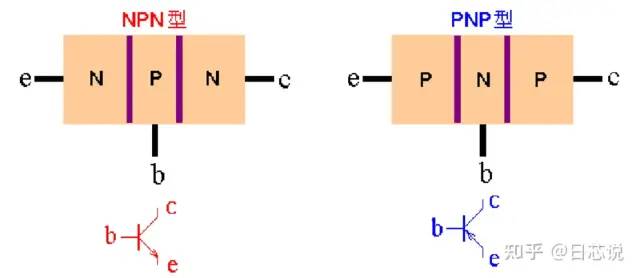

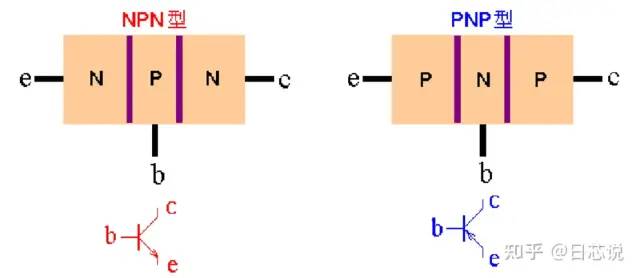

BJT即三极管,分为PNP和NPN型,简单示意图如下图所示。

NPN和PNP

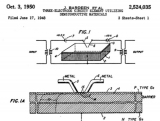

以NPN为例,其剖面图如下图,PNP的剖面图想必你肯定也知道了。

NPN的剖面图

说到这里,大家是不是好奇,具体到某一种工艺中,BJT的剖面图会是什么样子的?

读研三年和工作几个月,我只用过一种工艺,那就是大家都知道的CMOS工艺。

其实,“正宗”的BJT应该是用Bipolar工艺制造的。但是现实用这种工艺不多,很多年前,确实会用这种工艺,由于Bipolar工艺process繁多,价格也比CMOS工艺贵,集成度也远输于CMOS,慢慢大家都不怎么用Bipolar工艺了。

在CMOS工艺中,BJT的制作和Bipolar不同,可以说,CMOS工艺中,不是“正宗”的BJT device,而是一种寄生的BJT。

不知道有没有认真的同学发现,你所用的单纯的CMOS工艺中,只有PNP的BJT而没有NPN的BJT?

在没有DNW的CMOS工艺中,的确如此,且一般是纵向的寄生PNP三极管。why?

因为,没有DNW的工艺中,只有全局P-sub是和P+是P型半导体,这里P-sub充当PNP的一个“P”,即集电极,P+充当PNP的另一个“P”,即发射极,n-well充当PNP的“N”,即基极,而不是Bipolar工艺真正意义上的N和P。

PS:至于为什么是纵向的而不是横向的PNP,原因作者也布吉岛啦。

这里,全局P-sub衬底永远接VSS。

CMOS工艺中的纵向寄生PNP

看到这里,知道为什么普通CMOS工艺没有NPN了吗?

NPN正常工作的时候,基极发射极电压Vbe应大于其开启电压,也就是说基极电位大于0,但是CMOS工艺中p-sub永远是VSS不可能大于0,因此p-sub是不能做NPN的基极的。

有同学会问了,能不能用两个n-well做NPN的两个“N”,用P+做NPN的“P”呢?

答案是不能。why?n-well外面的P+就是衬底接触,也是接VSS的。

这里,建议有兴趣的同学可以仔细画一画这些寄生BJT的剖面图,结合CMOS工艺的特点进行分析,牢记BJT中遵循发射结正偏,集电结反偏的原理,看看在CMOS工艺中能否实现。

那么CMOS工艺中,就不能有PNP device了吗?肯定不是。

在有DNW的CMOS工艺中或者有双P-well的CMOS中,是可以有寄生的NPN的。

在DNW工艺中,DNW本身就是用来制造隔离的NMOS,DNW的存在使得NMOS的P衬底是”本地“的,即可以不接到全局p-sub上,因此就有了NPN中的基极"P"。

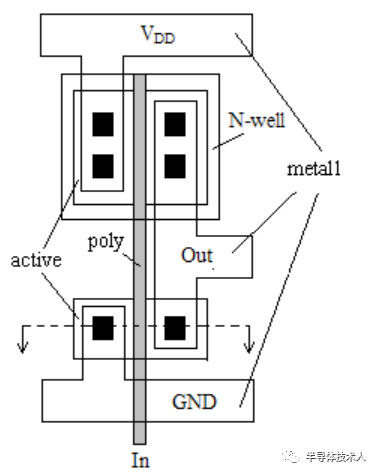

而在拥有双P-well的CMOS的工艺中,多出来的P-well充当NPN的基极"P",如下图:

浅阱NPN的剖面图

但是,双P-well,相比传统CMOS,多了一层浅P阱mask,增加了成本。

在CMOS工艺中,纵向寄生PNP的β值不会很大,一般不会超过10,具体数据可查看PDK中关于Bipolar的拟合数据。为什么β很小,我们知道,基区的厚度越大,β越小。在CMOS工艺中,也就是n-well的厚度,是较大的,因此β会很小,然而这个厚度是我们designer不可控的,是由foundry决定的。

到现在为止,作为模拟IC设计师,我只在bandgap中用过BJT,而且用的也不是其对基极电流的放大作用,而是两个BJT的Vbe差值与温度成正比这个特性,如下图。

PTAT电压产生电路

mentor说,在ESD电路中,基本都是二极管和MOS,BJT几乎不用。

因此,到现在为止,我对BJT的了解可以说很少,不多,但知道BJT的工作原理,足够在CMOS工艺中进行电路设计,毕竟latch up效应或者ESD中的GGNMOS和GGPMOS用到的寄生BJT的特性。

-

MOSFET

+关注

关注

147文章

7158浏览量

213162 -

BJT

+关注

关注

0文章

222浏览量

18156 -

模拟芯片

+关注

关注

8文章

626浏览量

51191

发布评论请先 登录

相关推荐

怎么采用标准CMOS工艺设计RF集成电路?

《炬丰科技-半导体工艺》CMOS 单元工艺

采用CMOS工艺的射频设计研究

基于CMOS下的像素阵列校正系统你了解多少呢?

什么是BCD工艺?BCD工艺与CMOS工艺对比

探索BJT、CMOS、DMOS等半导体工艺技术

CMOS工艺下的BJT你了解多少?

CMOS工艺下的BJT你了解多少?

评论