1、引言

以交换机设计为例。在交换机设计前期,转发表项是固化在交换机内部的(给FPGA片内BRAM初始值),但是在测试过程中,往往需要对表项进行修改,如果直接修改BRAM的coe文件,则需要重新综合、实现、生成bit文件,其中,综合与实现耗时十分严重,设计规模越大,消耗的时间越长,而生成bit文件消耗的时间则相对固定。

针对上述问题,本文探究一种避免综合与实现,直接修改BRAM初始化值的方法,可以避免综合、实现两个步骤,修改BRAM初始值后,直接生成bit文件,可节约大量的时间。

2、 操作方法

(1) 完成初始设计,综合、实现(但是不生成bit文件) ;

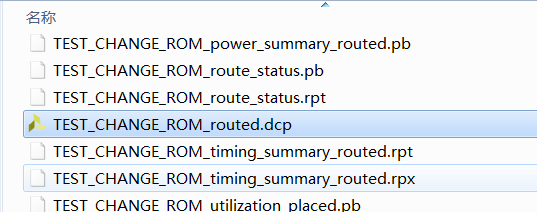

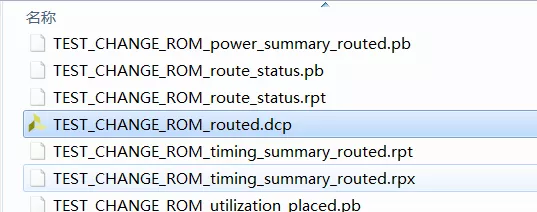

(2) 打开布线后的dcp文件(使用Vivado直接打开),如下图所示:

(3) 找到想修改的目标BRAM:

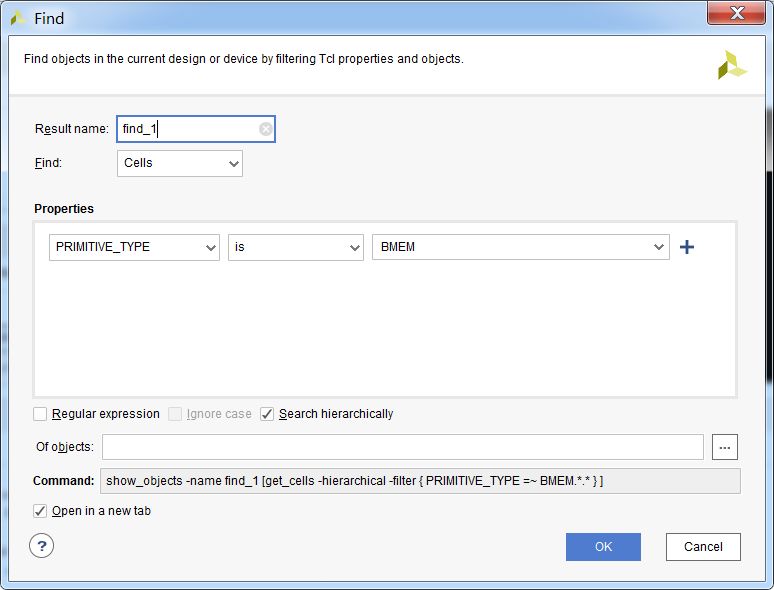

<3.1> ctrl+f ;

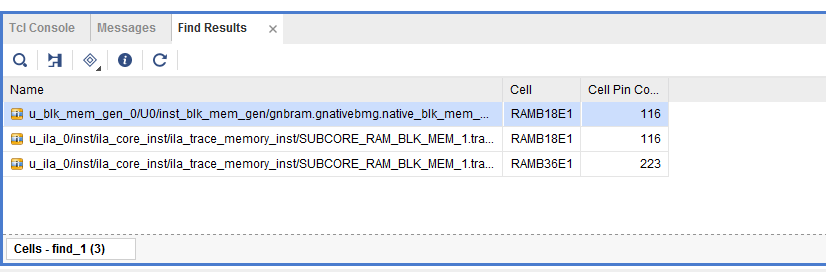

<3.2> 选择需要修改的BRAM ;

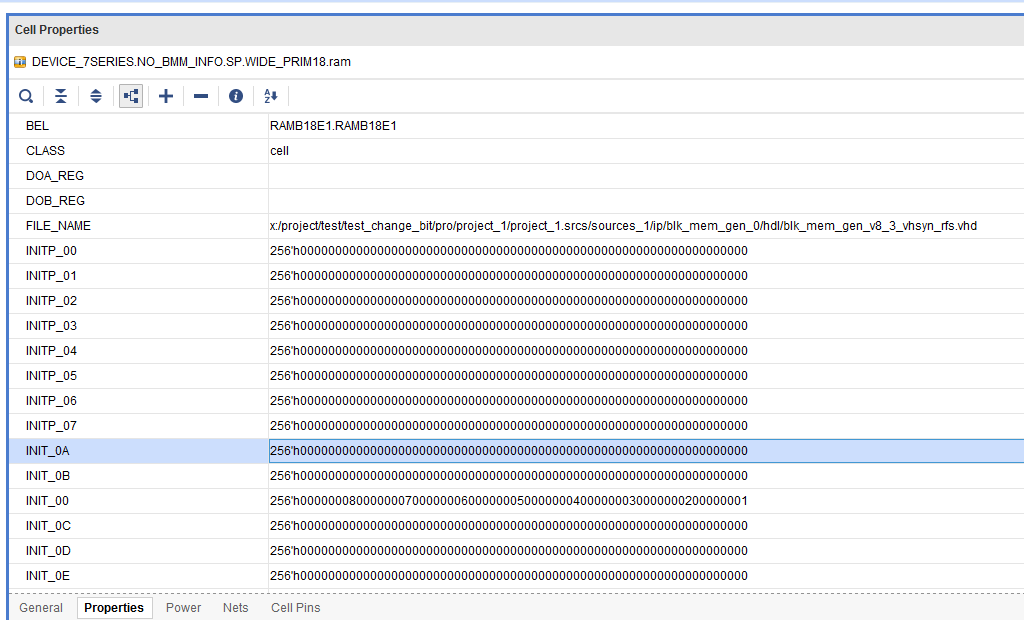

<3.3> 在properties界面,可以直接修改初始化文件(需要熟悉原语,其初始化方式与RAMB18E1相同);

<3.4>保存,退出;

<3.5>在主工程中打开实现设计,按照相同的方式可以找到对应的RAM与初始化值,可以发现初始化值已经改变了 ;

<3.6> 生成bitstream文件。

3、 上板实测

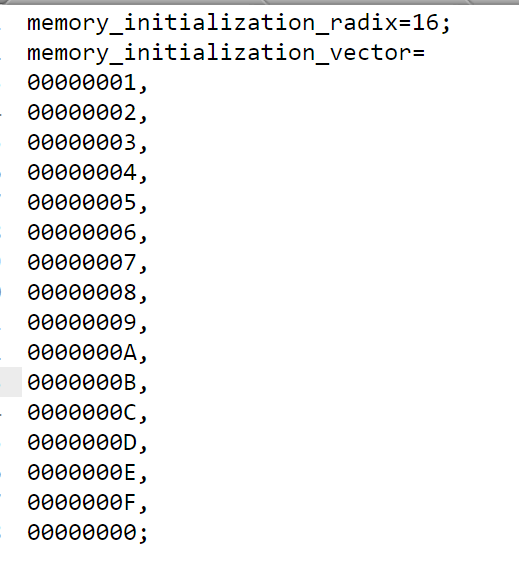

(1) coe文件:

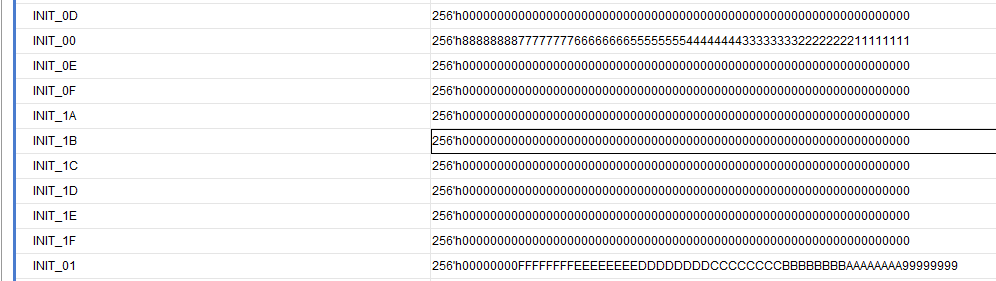

(2) 修改后的RAM初始化值

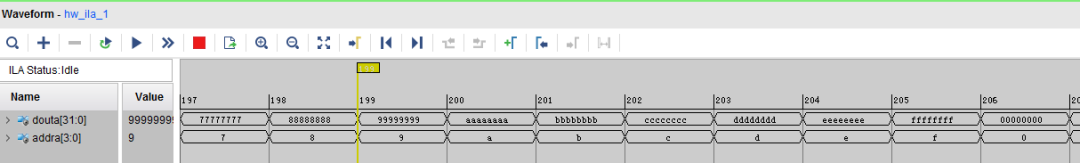

(3) 上板实测结果:

4、 结论

在仅修改BRAM初始化值的场景下,该方法可以大大减小从修改BRAM初始值到重新生成bitstream的时间,在交换机调试过程中,具有一定实用价值。

审核编辑:刘清

-

FPGA

+关注

关注

1631文章

21806浏览量

606701 -

交换机

+关注

关注

21文章

2661浏览量

100251 -

DCP

+关注

关注

0文章

30浏览量

17315 -

BRAM

+关注

关注

0文章

41浏览量

11040

原文标题:Vivado 直接修改RAM初始化文件,避免重新综合、实现的方法

文章出处:【微信号:HXSLH1010101010,微信公众号:FPGA技术江湖】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

有没有一种方法最佳的方法实现初始化I/O引脚

初始化BRAM警告coe文件不存在

请问初始化BRAM后怎么显示BRAM数据?

如何避免Spartan默认初始化BRAM?

初始化BRAM primitaves出现错误和循环漏洞的原因?

基于粒子群算法的同步时序电路初始化

一种多类原型模糊聚类的初始化方法

基于WRED协议的TCP连接初始化的优化方法

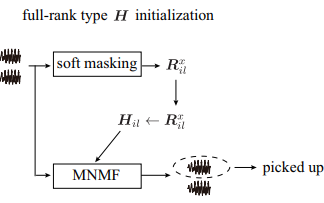

如何使用精确估计满秩空间相关矩阵实现MNMF稳定初始化的方法

探究一种避免综合与实现直接修改BRAM初始化值的方法

探究一种避免综合与实现直接修改BRAM初始化值的方法

评论