Q.什么是锁相环频率合成器?

A.频率合成器允许设计人员以单个参考频率的倍数形式生成各种输出频率。主要应用是生成本振(LO)信号,用于RF信号的上变频和下变频。

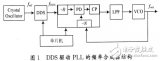

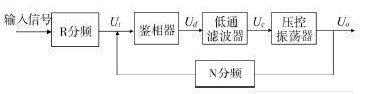

频率合成器在锁相环 (PLL) 中工作,其中相位/频率检测器 (PFD) 将反馈频率与参考频率的分频版本进行比较(图 1)。PFD的输出电流脉冲经过滤波和积分以产生电压。该电压驱动外部压控振荡器 (VCO) 增加或降低输出频率,从而将 PFD 的平均输出驱动至零。

图1.锁相环框图。

频率通过使用计数器来缩放。在本例中,ADF4xxx频率合成器与外部滤波器和VCO配合使用。输入基准电压源(R)计数器将基准输入频率(本例中为13 MHz)降低至PFD频率(F聚苯乙烯 = F裁判/R);反馈 (N) 计数器可降低输出频率,以便与 PFD 处的缩放参考频率进行比较。在平衡时,两个频率相等,输出频率为N×F聚苯乙烯.反馈计数器是双模预分频器类型,具有 A 和 B 计数器(N = BP + A,其中 P 是预分频器值)。

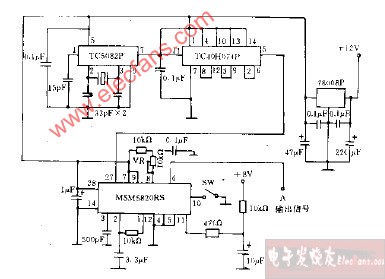

图2显示了超外差接收器的典型应用。基站和手机LO是最常见的应用,但频率合成器也可用于低频时钟发生器(ADF4001)、无线局域网(5.8 GHz)、雷达系统和防撞系统(ADF4106)。

图2.双PLL用于从GSM射频向下混频至基带。

Q.选择PLL频率合成器时要考虑哪些关键性能参数?

A.主要的是:相位噪声、参考杂散和锁定时间。

相位噪声:对于给定功率电平的载波频率,频率合成器的相位噪声是载波功率与在定义的频率偏移(频率合成器通常为1 kHz)下1 Hz带宽中的功率之比。以dBc/Hz表示,带内(或近载)相位噪声由频率合成器主导;VCO噪声贡献在闭环中进行高通滤波。

参考马刺:这些是内部计数器产生的离散失调频率下的伪影,电荷泵在PFD频率下工作。电荷泵的上下电流不匹配、电荷泵泄漏和电源去耦不足会增加这些杂散。杂散音将在所需信号的顶部混合,并降低接收器灵敏度。

锁定时间:PLL的锁定时间是在给定频率容差内从一个指定频率跳到另一个指定频率所需的时间。跳频大小通常由PLL在其分配的频带内工作时必须完成的最大跳转决定。GSM-900的步长为45 MHz,GSM-1800的步长为95 MHz。所需的频率容差分别为 90 Hz 和 180 Hz。PLL必须在小于1.5个时隙内完成所需的频率步进,其中每个时隙为577 μs。

Q.我根据所需的输出频率选择了合成器。如何选择PLL中的其他元件?

A. 频率基准:良好、高质量、低相位噪声基准对于稳定的低相位噪声RF输出至关重要。TCXO晶体提供的方波或削波正弦波具有出色的性能,因为更尖锐的时钟边沿可减少R计数器输出端的相位抖动。ADF4206系列具有板载振荡器电路,允许使用低成本AT切割晶体作为基准电压源。虽然可预测的AT晶体的成本是TCXO的三分之一,但除非实施变容二极管的补偿方案,否则其温度稳定性较差。

VCO:VCO将施加的调谐电压转换为输出频率。在VCO的整个频率范围内,灵敏度可能会有很大差异。这可能会使环路不稳定(请参阅环路过滤器)。通常,VCO的调谐灵敏度(Kv)越低,VCO相位噪声越好。频率合成器相位噪声将在与载波的较小偏移处占主导地位。离载波更远,VCO的高通滤波噪声将开始占主导地位。GSM 带外相位噪声规格在 130MHz 偏移时为 –1 dBc/Hz。

环路滤波器:有许多不同类型的环路滤波器。最常见的是图3所示的三阶积分器。通常,环路滤波器带宽应为PFD频率(通道间距)的1/10。增加环路带宽将减少锁定时间,但滤波器带宽不应超过PFD/5,以避免显著增加不稳定的风险。

图3.三阶环路滤波器。R2C3极点为杂散产物提供额外的衰减。

环路滤波器的带宽可以通过将PFD频率或电荷泵电流加倍来实现倍增。如果VCO的实际Kv明显高于用于设计环路滤波器的标称Kv,则环路带宽将明显宽于预期。环路带宽随Kv的变化在宽带PLL设计中是一个重大的设计挑战,其中Kv的变化可能超过300%。增加或减少可编程电荷泵电流是补偿由Kv变化引起的环路带宽变化的最简单方法。

Q.如何针对相位噪声优化PLL设计?

A. 使用低 N 值:由于相位噪声以 20 log N 的速率从 PFD(参考频率)乘以,因此将N 降低 2 倍将使系统相位噪声降低 3 dB(即,将 PFD 频率加倍可将相位噪声降低 10 log2)。因此,应始终使用最高的可行PFD频率。

选择比所需频率更高的频率合成器:在900 MHz的相同条件下工作,ADF4106的相位噪声比ADF6好4111 dB(见表1)。

使用指定用于工作时的最低 Rset 电阻器:减小Rset会增加电荷泵电流,从而降低相位噪声。

表 1.积分相位抖动在很大程度上取决于频率合成器的带内相位噪声。系统参数:[900 MHz 射频、200 kHz PFD、20 kHz 环路滤波器]

| 合成器模型 | 带内相位噪声 (dB) |

积分范围 (赫兹) |

积分相位误差 (均方根度) |

| ADF4111 | –86 | 100 至 1 M | 0.86 |

| ADF4112 | –89 | 100 至 1 M | 0.62 |

| ADF4113 | –91 | 100 至 1 M | 0.56 |

| ADF4106 | –92.5 | 100 至 1 M | 0.45 |

Q.为什么相位噪声很重要?

答:相位噪声可能是PLL选择中最关键的规格。在发射链中,线性功率放大器(PA)是最难设计的模块。低相位噪声LO通过减小基带信号上变频中的相位误差,为设计人员提供更大的PA非线性裕量。

GSM 接收器/发射器 (Rx/Tx) 的系统最大相位误差规格为 5° rms。如表1所示,当PLL贡献的相位噪声降低时,允许的PA相位误差贡献会明显更大。

在接收端,低相位噪声对于获得良好的接收器选择性(接收器在存在干扰源时解调信号的能力)至关重要。在图4的示例中,左侧的所需低电平信号被附近与LO噪声混合的不需要的信号(封闭虚线区域)淹没。在这种情况下,滤波器将无法阻挡这些不需要的干扰源。为了解调所需的RF信号,发射端需要更高的输出功率,或者需要改善LO相位噪声。

图4.大的无用信号与LO噪声混合会淹没所需信号。增加相位噪声会降低接收器的灵敏度,因为解调器将无法从噪声中分辨信号。

Q.为什么杂散水平很重要?

一个。大多数通信标准对LO可以产生的杂散频率分量(杂散)水平有严格的最大规格。在传输模式下,必须限制杂散电平,以确保它们不会干扰同一或附近系统中的用户。在接收器中,LO杂散会显著降低解调混频降频信号的能力。图4显示了倒易混频的影响,其中由于振荡器上有大量的不需要的信号与噪声混合,目标信号被噪声淹没。杂散噪声分量也会出现同样的效果。

高水平的杂散会迫使设计人员缩小环路带宽(减慢响应速度),从而间接影响锁定时间,以便为这些不需要的元件提供足够的衰减。确保低基准杂散的关键频率合成器规格是低电荷泵泄漏和电荷泵电流匹配。

Q.为什么锁定时间很重要?

一个。许多系统使用跳频作为保护数据安全、避免多路径衰落和避免干扰的手段。PLL在实现频率锁定方面所花费的时间是宝贵的时间,不能用于发送或接收数据;这降低了可实现的有效数据速率。目前没有可用的PLL可以足够快地跳频以满足GSM协议的定时要求。在基站应用中,两个独立的PLL器件并联使用,以减少浪费的插槽数量。当第一个为发射器生成LO时,第二个PLL正在移动到下一个分配的通道。在这种情况下,超快速(<10 μs)建立PLL将显著降低物料清单(BOM)和布局复杂性。

Q.如何最小化锁定时间?

一个。通过增加PFD频率。PFD频率决定了在VCO/N和参考信号之间进行比较的速率。增加PFD频率会增加电荷泵的更新并缩短锁定时间。它还允许扩大环路带宽。

图5.环路带宽对锁定时间有显著影响。环路带宽越宽,锁定时间越快,但杂散元件的水平也越大。对于 1kHz LBW,142 kHz 的锁定时间为 35 μs,对于 248kHz LBW 时为 10 μs。

环路带宽。环路带宽越宽,锁定时间越快。代价是,更宽的环路带宽将减少杂散产物的衰减并增加积分相位噪声。显著增加环路带宽 (>PFD/5) 可能会导致环路变得不稳定并永久失去锁定。45度的相位裕量产生最佳的稳定瞬变。

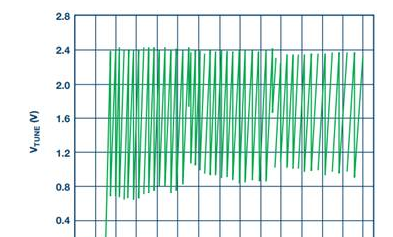

避免调谐接近地电位或 Vp 的电压。当调谐电压在电荷泵电源轨(Vp)的一伏以内时,电荷泵开始在饱和区域工作。在该区域操作将显著缩短稳定时间;它还可能导致频率上升和跳跃之间的不匹配。通过使用可用的最大Vp或使用有源环路滤波器,可以避免在此饱和区域工作。使用具有更高 Kv 的 VCO 将使 Vtune 保持更接近 Vp/2,同时仍可在所需的频率范围内调谐。

选择塑料电容器。一些电容器表现出介电记忆效应,这会阻碍锁定时间。对于快速锁相应用,建议使用“塑料薄膜”松下ECHU电容器。

Q.哪些因素决定了我可以使用的最大PFD频率?

A.为了以PFD频率的步长获得连续的输出频率

其中 P 是预分频器值。

ADF4xxx提供低至8/9的预分频器选择。这允许PFD频率高于许多竞争器件,而不会违反上述规则,从而实现更低的相位噪声PLL设计。即使不满足此条件,如果编程寄存器中的 B > A 和 B > 2,PLL 也会锁定。

问:小数N自1970年以来一直存在。它对PLL设计人员有什么优势?

一个。整数 N 分频 PLL 输出端的分辨率仅限于 PFD 频率的步长。小数N允许PLL输出端的分辨率降低到PFD频率的一小部分。可以生成分辨率为100sHz的输出频率,同时保持高PFD频率。因此,N 值明显小于整数 N。由于电荷泵的噪声以20 logN的速率乘以输出,因此相位噪声可以显著改善。对于GSM900系统,小数N分频ADF4252的相位噪声性能为–103 dBc/Hz,而整数N分频PLL的相位噪声性能为–93 dBc/Hz。

同样具有显著优势的是小数N分频实现的锁定时间改进。PFD频率设置为20 MHz,环路带宽设置为150 kHz,将允许频率合成器在<30 μs内跳跃30 MHz。目前的基站需要2个PLL模块,以确保LO能够满足传输的时序要求。凭借小数N分频的超快锁定时间,未来的频率合成器将具有锁定时间规格,允许将2个“乒乓”PLL替换为单个小数N分频PLL模块。

Q.如果小数N分频具有所有这些优势,为什么整数N分频PLL仍然如此受欢迎?

A. 虚假级别!小数 N 除以 19.1 包括 N 除以 90 10% 的时间和 4252 <>% 的时间。平均除法是正确的,但瞬时除法不正确。因此,PFD和电荷泵不断尝试校正瞬时相位误差。提供平均功能的Σ-Δ调制器的大量数字活动会在输出端产生杂散分量。数字噪声,加上与辛勤工作的电荷泵匹配不准确,导致杂散电平大于大多数通信标准所允许的水平。直到最近,ADF<>等小数N分频器件才对杂散性能进行了必要的改进,使设计人员能够考虑将其用于传统的整数N分频市场。

Q.您最近发布了哪些PLL设备,它们有何不同,我将在哪里使用它们?

答:ADF4001是一款<200 MHz PLL,与常用的ADF4110系列引脚兼容,但去掉了预分频器。应用是稳定的参考时钟发生器,在所有时钟必须与单个参考源同步的情况下。它们通常与VCXO(压控晶体振荡器)一起使用,VCXO具有比VCO更低的增益(Kv)和更好的相位噪声。

ADF4252是一款双通道小数N分频器件,具有<70 dBc杂散特性。它提供 <20 μs 锁定时间,而整数 N 的锁定时间为 250 μs,由于采用高 PFD 频率,相位噪声为 <100 dBc/Hz,这是一种突破性产品,可在相位噪声和杂散之间进行软件编程权衡。

ADF4217L/ADF4218L/ADF4219L 是 LMX2331L/LMX2330L/LMX2370 的低相位噪声升级版。它们的功耗仅为 7.1 mA,相位噪声比竞争器件提高了 4dB。手机设计师的好消息!

ADF4106是一款6 GHz PLL频率合成器。它是 5.4 至 5.8GHz 频段 WLAN 设备的理想选择,是市场上噪声最低的整数 N 分频 PLL。

Q.哪些工具可用于模拟循环行为?

答:ADIsimPLL是应用无线电实验室开发的仿真工具。它包括ADI频率合成器以及常用VCO和TCXO的广泛模型。它允许用户设计多种配置中的无源和有源环路滤波器,仿真VCO、PLL和基准噪声,并对杂散和建立行为进行建模。设计完成后,可以使用安富利的内部网络链接根据设计订购定制评估板。

图6.锁定时间和相位噪声只是ADIsimPLL可以建模的两个参数。虽然相位噪声降低了>8 dB,但小数N分频允许的更宽环路带宽和高PFD频率将30 MHz跳跃的锁定时间缩短至<30 μs(如图所示)。

Q.与同类竞争器件相比,ADI专有器件是否具有特定优势?

答:相位噪声是许多系统设计人员的关键规格。ADF4113系列的相位噪声性能通常比国家级同类产品高6 dB,比富士通或飞利浦同类产品高>10 dB。预分频器设置的扩展选择可保护设计人员在选择更高PFD频率时不会受到'P2– P' 规则。另一个主要优点是可选择8个可编程电荷泵电流;在VCO增益发生巨大变化的宽带设计中,可以调整可编程电流,以确保整个频段的环路稳定性和带宽一致性。

Q.PLL行业未来的发展方向是什么?

一个。虽然芯片组解决方案在头条新闻中占据突出地位,特别是对于GSM,但新一代蜂窝电话和基站最初仍可能偏爱分立解决方案。分立式PLL和VCO模块提供改进的噪声性能和隔离,并且在设计周期开始时已经大批量生产。

对减小手机尺寸和电流消耗的需求推动了采用微型CSP封装的0.35μm Bi-CMOS双通道频率合成器的ADI L系列双通道频率合成器的发展。集成VCO和PLL模块将是较新系统设计的主要增长,其中初始设计的电路板面积和成本降低至关重要。

然而,最令人兴奋的发展可能是小数N分频技术。最近在杂散性能方面的改进使ADF4252得以发布,并引起了前所未有的兴趣。该架构固有的相位噪声改善、超快锁定时间和多功能性很可能主导未来多标准高数据速率无线系统的LO模块。

审核编辑:郭婷

-

频率合成器

+关注

关注

5文章

224浏览量

32556 -

pll

+关注

关注

6文章

788浏览量

135703 -

VCO

+关注

关注

13文章

194浏览量

69638

发布评论请先 登录

相关推荐

合成器

如何利用FPGA设计PLL频率合成器?

DDS PLL短波频率合成器设计

基于DDS驱动PLL结构的宽带频率合成器的设计与实现

基于FPGA与PLL频率合成技术设计的整数/半整数频率合成器

咨询应用工程师:PLL频率合成器

咨询应用工程师:PLL频率合成器

评论