本应用笔记描述了意法半导体开发的首款指令缓存(ICACHE)和数据缓存(DCACHE)。

在 Arm Cortex-M33 处理器的 AHB 总线中引入的 ICACHE 和 DCACHE 嵌入到下表中列出的 STM32 微控制器(MCU)中。

这些缓存使用户从内部和外部存储器提取指令和数据时或在用于外部存储器的数据流量时提高应用性能并降低功耗。本文档提供了典型示例,以强调 ICACHE 和 DCACHE 功能,并便于配置

1ICACHE 和 DCACHE 概述

2ICACHE 和 DCACHE 主要特性

3 ICACHE 和 DCACHE 的性能与功耗

4 结论

本节概述了嵌入在基于 STM32 Arm Cortex内核的微控制器中的 ICACHE 和 DCACHE 接口。详细介绍了 ICACHE 和 DCACHE 框图架构以及在系统架构中的集成。

此架构基于总线矩阵,允许多个主设备(Cortex-M33、DMA1/2 和 SDMMC1)访问多个从设备(如Flash 存储器、SRAM1/2、OCTOSPI1 或 FSMC)。

下图描述了 STM32L5 系列智能架构。

由于将 8-Kb 的 ICACHE 接口引入其 C-AHB 总线,通过快速总线从内部存储器(Flash 存储器、SRAM1 或SRAM2)或通过慢速总线从外部存储器(OCTOSPI1 或 FSMC)提取代码或数据时,Cortex-M33 的性能有所提升。

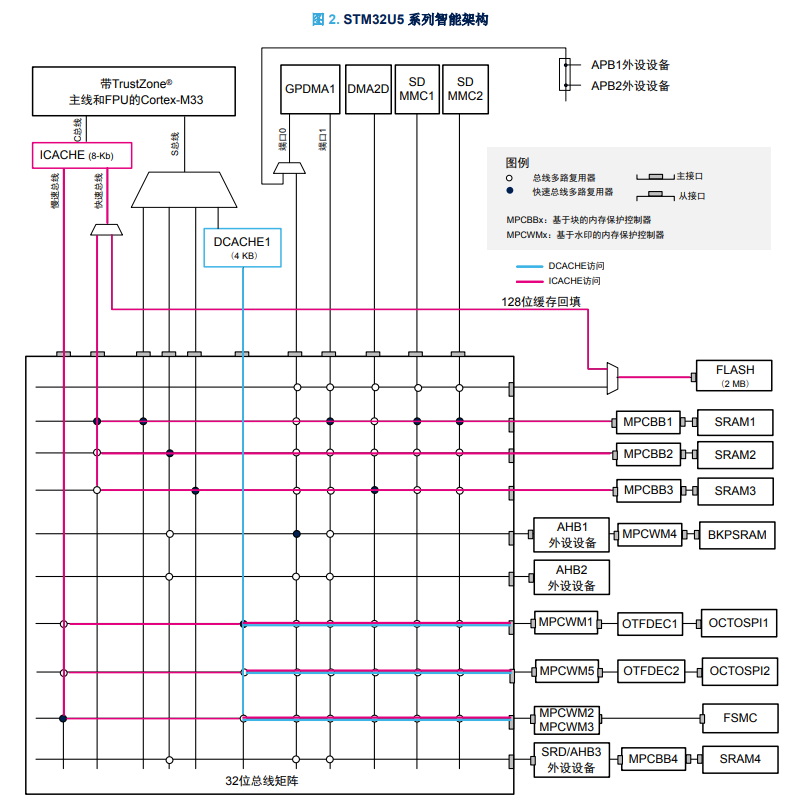

此架构基于总线矩阵,允许多个主设备(Cortex-M33、GPDMA1、DMA2D 和SDMMC1/2)访问多个从设备(如 Flash 存储器、SRAM1/2/3/4、BKPSRAM、OCTOSPI1/2 或 FSMC)。

下图描述了 STM32U5 系列智能架构。

其 C-AHB 总线引入了 8-Kb 的 ICACHE 接口,通过快速总线从内部存储器(Flash 存储器、SRAM1、SRAM2 或SRAM3)或通过慢速总线从外部存储器(OCTOSPI1、OCTOSPI2 或 FSMC)提取代码或数据时,Cortex-M33 的性能有所提升。其 S-AHB 总线引入了 4-Kb 的 DCACHE 接口,提高了外部存储器(OCTOSPI1、OCTOSPI2 或 FSMC)的数据流量。

ICACHE 存储器包括:

• 具有以下元素的 TAG 存储器:

– 指示将哪些数据包含在缓存数据存储器中的地址标签

– 有效位

• 数据存储器,包含缓存的数据

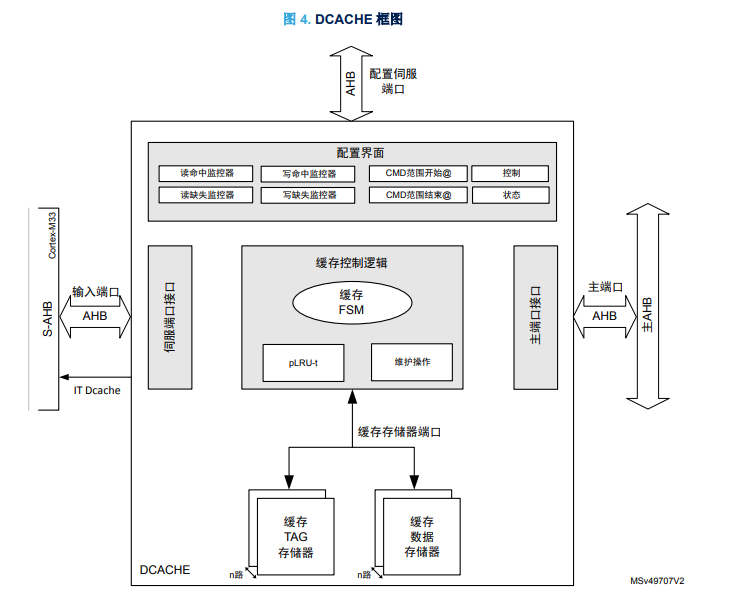

DCACHE 存储器包括:

• 具有以下元素的 TAG 存储器:

– 指示将哪些数据包含在缓存数据存储器中的地址标签

– 有效位 特权位

– dirty 位

• 数据存储器,包含缓存的数据

本文档详细介绍了意法半导体开发的首款指令缓存(ICACHE)和数据缓存(DCACHE)的基本特性,并在文中提供示例介绍其性能,为大家带来关于这款指令的全面解读。由于文章篇幅有限仅展示部分,完整内容请点击“阅读原文”下载原文档。

▽点击“阅读原文”,可下载原文档

原文标题:应用笔记|使用 STM32 缓存来优化性能与功率效率

文章出处:【微信公众号:STM32单片机】欢迎添加关注!文章转载请注明出处。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

原文标题:应用笔记|使用 STM32 缓存来优化性能与功率效率

文章出处:【微信号:STM32_STM8_MCU,微信公众号:STM32单片机】欢迎添加关注!文章转载请注明出处。

相关推荐

S32K3xxICU应用笔记

发表于 12-30 15:38

•0次下载

SSM框架的性能优化技巧 SSM(Spring + Spring MVC + MyBatis)框架的性能优化是提升Java Web应用性能的

![的头像]() 发表于

发表于 12-17 09:10

•191次阅读

服务器端渲染(SSR)是一种将前端页面在服务器端生成的技术,它可以提高首屏加载速度,改善SEO,并提供更好的用户体验。然而,SSR也可能带来性能挑战,尤其是在处理大量请求时。以下是一些优化SSR渲染

![的头像]() 发表于

发表于 11-18 11:31

•338次阅读

MCU(微控制单元)是现代电子产品中不可或缺的核心组件,广泛应用于家电、汽车、工业控制、医疗设备及消费电子等领域。随着科技的不断发展,MCU的性能与功能得到了前所未有的提升,而优化设计成为推动这一变化的关键所在。

![的头像]() 发表于

发表于 11-01 13:26

•281次阅读

电子发烧友网站提供《变频器的功率计基本计算应用笔记.pdf》资料免费下载

发表于 09-09 14:38

•0次下载

本应用笔记旨在展示使用CS32FOxx微控器,针对定时器外设的应用。帮助用户了解CS32FOxx定时器的基本特性、操作模式及相关应用的示例代码。提供的一些高级应用以便缩短用户开发周期。对所介绍的特定

发表于 05-16 15:02

本应用笔记旨在展示使用CS32FOxx微控器,提高A/D转化精度的应用。帮助ADC模块用户了解 CS32微控器提供的一些高级应用并加快开发周期。所介绍的每种模式都提供一个应用示例,以方便用户快速移植

发表于 05-16 14:58

本应用笔记旨在帮助指导用户针对芯海通用 MCU 基于 IAR 环境的快速开发,帮助用户快速建立应用工程。芯海科技通用 MCU 提供的 pack 开发包都是仅支持芯海 CSU、MDK 或 IAR 通用

发表于 05-16 11:50

本应用笔记旨在帮助指导用户针对芯海通用 MCU 基于 GCC 环境的快速开发。芯海科技通用 MCU 提供的 pack 开发包都是仅支持芯海 CSU、MDK 或 IAR 通用集成的 IDE 工具,如果

发表于 05-16 11:47

本应用笔记旨在帮助指导用户针对芯海 CORTEX-M3 MCU CS32F103 系列单片机 IAP 应用的快速开发。本应用笔记实现了 CAN 和 USART 两种接口方式来开发 IAP 应用,协议

发表于 05-16 11:40

本文档描述了基于芯海 CS32F103 系列芯片的矢量控制电机开发板 V1.00 的设计理念、结构和使用说明,以帮助用户快速使用此开发板,评估 CS32F103 芯片在电机控制应用上的性能表现。*附件:应用笔记:CS32F103FOC电机评估板使用指南.pdf

发表于 05-16 11:35

本应用笔记旨在为用户提供关于CSU18P88的详细信息和使用指南,帮助用户快速开发基于CSU18P88的应用。*附件:CSU18P88应用笔记V1.5.pdf

发表于 05-16 10:24

本应用笔记旨在为用户提供关于CSU18MX86的详细信息和使用指南,帮助用户快速开发基于CSU18MX86的应用。*附件:CSU18MX86应用笔记_V1.0.pdf

发表于 05-16 10:21

电子发烧友网站提供《Microchip TCP/IP 协议栈应用笔记.pdf》资料免费下载

发表于 04-17 14:16

•1次下载

小编最近在使用系统的时候,发现尽管应用已经使用了 redis 缓存提高查询效率,但是仍然有进一步优化的空间,于是想到了比分布式缓存性能更好的

![的头像]() 发表于

发表于 01-18 11:19

•859次阅读

应用笔记|使用 STM32 缓存来优化性能与功率效率

应用笔记|使用 STM32 缓存来优化性能与功率效率

评论