大家知道,为实现低相位噪声性能,尤其是超低相位噪声性能,必须使用低噪声电源才能达到最佳性能。但文献上没有详细说明如何通过一种系统化方法来量化电源噪声电压电平对相位噪声的影响。本文旨在改变这种状况。

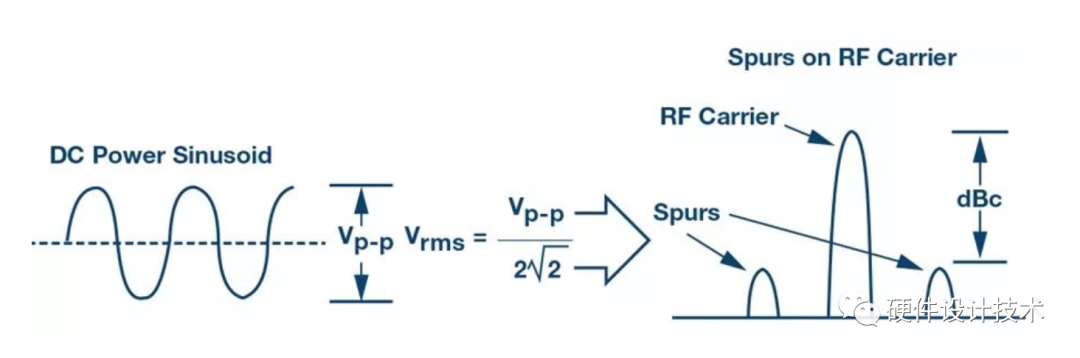

本文提出了电源调制比(PSMR)理论,用来衡量电源缺陷如何被调制到RF载波上。通过电源噪声对RF放大器相位噪声的贡献来验证这一理论;测量结果表明,可以计算并且相当准确地预测该贡献。基于此结果,本文还讨论了描述电源特性的系统化方法。

审核编辑:刘清

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

电压电平

+关注

关注

0文章

25浏览量

7499 -

PSRR

+关注

关注

0文章

153浏览量

39296 -

电源噪声

+关注

关注

3文章

149浏览量

17462 -

RF放大器

+关注

关注

0文章

29浏览量

3492

原文标题:PSMR与PSRR不同之处

文章出处:【微信号:硬件设计技术,微信公众号:硬件设计技术】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

DAC相位噪声性能改进包含残余相位噪声测量方法和最佳稳压器选择

在于,在测试设置中需要额外的DAC。但是,优点是可以应用于系统级分析预算,作为DAC相位噪声贡献的一种非常好的指标。 图4a. 使用鉴相器方法

发表于 03-19 22:09

一种更通用的方法来监测处理器中的电压噪声

的是,这种专门的电路还不是大多数高端Arm系统的标准功能。在我们最近与塞浦路斯大学的合作研究中,我们成功地开发了一种更通用的方法来监测处理器中的电压

发表于 11-01 14:48

一种改进的相位噪声抑制方法

随着卫星数传容量急剧增加,高阶调制解调方式在实际中被广泛采用,卫星通信系统的性能有了更高的要求。针对这一现状,给出一种基于最小均方根的相位噪声

发表于 01-04 17:13

•14次下载

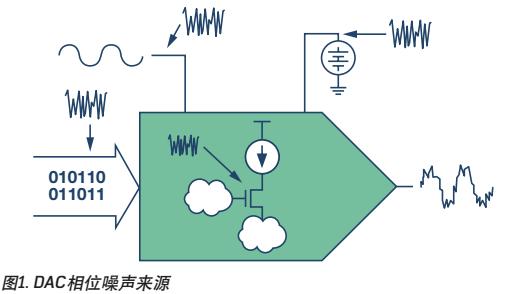

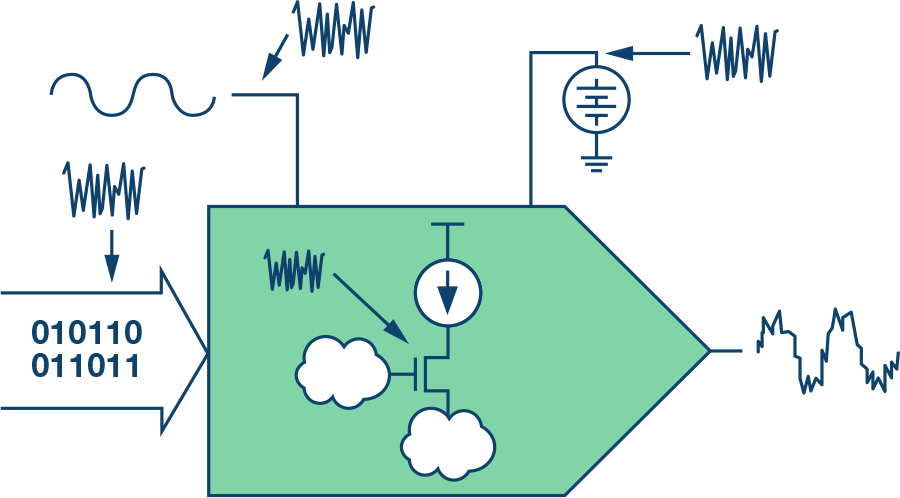

电源噪声和时钟抖动对高速DAC相位噪声的影响

在所有器件特性中,噪声可能是一个特别具有挑战性、难以掌握的设计课题。这些挑战常常导致一些道听途说的设计规则,并且开发中要反复试错。本文将解决相位噪声

发表于 03-08 11:37

•10次下载

如何通过一种系统化方法来量化电源噪声电压电平对相位噪声的影响?

许多雷达系统要求低相位噪声以最大限度抑制杂波。高性能雷达需要特别关注相位噪声,导致在降低频率合成器的相位

电源噪声和时钟抖动对高速DAC相位噪声的影响的分析及管理

在所有器件特性中,噪声可能是一个特别具有挑战性、难以掌握的设计课题。这些挑战常常导致一些道听途说的设计规则,并且开发中要反复试错。本文将解决相位噪声

如何通过一种系统化方法来量化电源噪声电压电平对相位噪声的影响

如何通过一种系统化方法来量化电源噪声电压电平对相位噪声的影响

评论