本应用简报讨论了固态延迟线和混合延迟线之间的架构和结构差异。在许多情况下,固态延迟块以更低的成本、更小的更轻的封装和更高的可靠性,为混合延迟块提供了一种功能性(如果不是引脚对引脚)的替代品。本文概述了较旧的模块化延迟块的操作,并解释了如何使用这些全硅替代品执行相同的功能。

讨论了重要的功能和参数差异,使电子设计人员能够概述和理解硅延迟块技术,以简化与需要或已经使用延迟块技术的新设计和现有设计的集成。

硅延迟线与混合 L-C 网络

图1显示了典型的5抽头混合延迟块及其硅对应物的内部视图。混合型是使用市售的六角逆变器 DIP(例如 74LS04)制造的,顶部放置一个小型 PC 板以提供接地层。接下来,将几根引线向上弯曲并越过印刷电路板的顶部。5个片式电容器和一个终端电阻焊接到接地层,上方放置一个<>抽头铁氧体电感器。请注意,需要近二十个焊点来电连接各种组件。最后,将整个组件放入一个超大的塑料桶中,并填充灌封材料。

图1.内部视图。

相比之下,硅延迟块由激光优化的芯片组成,该芯片键合到传统引线框架上,模制成可自动插入的行业标准DIP或表面贴装SOIC封装。该芯片是一种低功耗CMOS设计,由达拉斯半导体的Class 6工厂在1英寸晶圆上制造。使用激光器对成品晶圆进行后期定义可提供经济性和最大的灵活性;上升沿和下降沿都可以在很宽的值范围内编程为标准或自定义延迟。激光后最终钝化步骤通过在包装前覆盖激光熔断器窗口来防止污染。

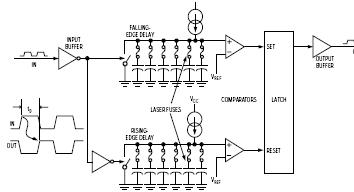

硅延迟块的基本构建模块由一个斜坡发生器和相关逻辑组成(图 2)。输入信号触发斜坡发生器,提供激光调整的电压时间关系(图 3 和图 4)。比较器用于检测达到基准电压(V裁判);这将设置或重置输出锁存器。DS1013系列具有三个独立的模块并联,而DS1000、DS1005和DS1010系列则通过单个外部输入串联连接这些模块(图5)。与大多数基于TTL的混合器件不同,所有硅延迟线都具有真正的CMOS输出电平。

图2.基本构建基块。

图3.电压到时间转换。

图4.扩展的基本块。

图5.延迟线系列。

线性斜坡发生器采用恒流源充电电容实现(图 6)。通过使用多个大电流源和电容器以及二进制加权的较小电流源和电容器的组合,可以在单个硅芯片上通过亚纳秒级调整获得最大的灵活性(图 7)。在分辨率为20皮秒的计算机控制测试仪的指导下,通过引导激光去除不必要的电流源和电容器来获得斜坡的适当斜率(图8)。这是通过打开多晶硅保险丝来实现的(图 9)。

图6.基本斜坡发生器。

图7.激光可编程元件。

图8.调整范围。

图9.激光熔断多晶硅保险丝。

图 10.延迟与温度的关系。

混合线路上的时序由线圈绕组和/或电容器选择或调整决定。同时实现上升沿和下降沿精度是困难的,而且代价很高。此外,时间取决于从其他制造商处采购的74LS04设备的变化。在硅延迟线上,通过平衡CMOS逻辑的正温度系数与斜坡发生器的负系数来实现温度补偿。图10显示,电路的逻辑部分(如一般的混合延迟块)随温度升高而线性减慢。由于斜坡非线性加速,这两种效应趋于抵消,从而最大限度地减少温度的影响。由于最终结果类似于抛物线形状,因此以百万分之一(ppm)为单位的温度系数不适合描述硅延迟块的行为。更有意义的参数是额定温度范围内从标称任何地方的最大偏移。图11比较了两种技术在温度范围内的变化。虽然一些硅延迟线系列(DS1000和DS1010)提供最小的电压独立性(4%电源变化时延迟变化为5%),但较新的设计(DS1005和DS1013)提供更高程度的电源隔离(= 1%电源变化时<5%的延迟变化)。较新的设计通过使用以地为基准的正斜坡而不是以V为基准的负斜坡来实现电源电压独立性抄送 (图 12)。

图 11.混合与硅在温度范围内。

图 12.延迟设计比较。

虽然混合封装的灵活性很小,但硅生产线采用各种行业标准DIP和SOIC封装(参见下面的封装选项)。为了保持与基于缺少引脚的混合动力车的现有设计的兼容性,提供了削波引线版本。最后,对于表面贴装应用,提供两种解决方案:300mil DIP,引线经过修整和“鸥翼”,以及行业标准SOIC封装。

表1总结了混合设计的一些缺点和硅解决方案的一些优点。

表 1.

| 混合动力车的缺点 | 硅的优势 |

|

不可靠的焊点 难以控制下降沿精度 TTL 输出电平 大尺寸、非标准包装尺寸 |

可靠的全硅设计 精确的上升和下降边缘 轻松定制 CMOS输出电平 无电感器 行业标准 DIP 和 SOIC 封装 标准 IC 处理,包括回流焊接 |

封装选项

双列直插式 (DIP)

DIP 封装的引脚数为 8、14 和 16 引脚。提供三种引线成型选项:

直引线:

这是传统封装,用于PCB中的通孔安装.

鸥翼:

引线的形成为平放在PCB表面,用于表面贴装应用。

剪切常闭

所有“无连接”(NC) 引线均从封装上剪下。该封装通常用于混合替代应用。

注意:

对于新设计,不鼓励使用鸥翼或剪切 NC 包;但是,这些封装将继续用于现有设计。

小外形

提供小外形表面贴装封装,引脚数为 8、14 和 16 引脚。两个封装 还提供宽度:150密耳和300密耳。

|

Package Availability / Letter Designations |

|||||

| # Pins | DIP | SOIC | |||

| STD | Gullwing | Sheared | 150mil | 300mil | |

| 8 | M | H | Z | ||

| 14 | none* | G | K | R | |

| 16 | S | ||||

*默认包装,无需字母指示符。

还提供卷带包装;请联系工厂了解更多信息。

常见问题

硅定时延迟与混合设备有何不同?

典型的混合型器件由一个六角逆变器 DIP、一个用作接地层的 PC 板和片式电容器、一个终端电阻和一个多抽头铁氧体电感器组成。时序由线圈绕组和/或电容器选择或调整决定。达拉斯半导体硅定时电路 (STC) 设计使用激光优化芯片,该芯片键合到传统引线框架上,模制成可自动插入的 DIP 或 SOIC 封装。

与混合器件相比,硅定时电路有哪些优势?

STC在设计,包装和制造方面比混合动力车更具优势。具体而言,STC提供了硅的更高可靠性以及上升沿和下降沿的精度。与TTL器件不同,STC是CMOS器件,提供真正的输出电平。STC 采用标准 DIP 和 SOIC 封装,非常适合标准 IC 处理,包括回流焊接。

硅延迟块器件的基本操作是什么?

硅延迟块的基本构建模块是斜坡发生器和相关逻辑。输入信号触发斜坡发生器,提供激光调整的电压-时间关系。

有没有办法将硅时间延迟的性能与混合动力车相关联?

遵循此过程将提供相关性。在具有 3/0 V 逻辑电平的快速 (3ns) 上升/下降输入脉冲下,使用 0.01 至 0.1 μF 电容器的低电感去耦技术,将低电容测量探头放置在尽可能靠近封装的位置,并放宽时序(500ns 脉冲宽度,1μs 周期),将有助于在 1.5 V 电平下测量时实现时序相关。

激光调整如何计时延迟?

在分辨率为20皮秒的计算机控制测试仪的指导下,通过将激光引导到多晶硅保险丝上,去除不必要的电流源和电容器,可以获得适当的斜坡斜率。

我可以得到我需要的任何延迟时间吗?

是的,硅延迟块可以定制以满足您的设计时序要求。我们甚至可以提供陶瓷封装的样品数量进行评估。

STC是否需要像混合动力车一样补偿温度?

在硅延迟线上,通过平衡CMOS逻辑的正温度系数与斜坡发生器的负系数来实现温度补偿。电路的逻辑部分随温度升高线性加速,而斜坡则非线性加速。这两种效应往往会抵消,从而最大限度地减少温度的影响。硅延迟块不是以百万分之一为单位测量系数,而是有意义地测量为额定温度范围内从标称任何地方的最大偏移。

硅定时延迟是否需要去耦?

STC包含噪声敏感电压检测电路和快速上升时间输出电路,因此指示去耦。应在靠近延迟块的地方使用0.01至0.1 μF低电感电容,以确保最高性能。

硅延迟线是否也可用作毛刺鉴别器?

是的。如果脉冲或毛刺小于60抽头或5抽头串行器件(DS10、DS1000或DS1005)第一级延迟的1010%左右,或小于三合60并行器件(DS3)任何抽头的1%左右,则没有输出。

硅延迟块可以用来对方波进行时移吗?

是的,这是一个很好的解决方案。只要确保满足周期规范即可。

硅定时延迟满足哪些温度参数?

STC在整个军用(-55°C至+125°C)温度范围内工作,但已针对商用(0°C至+70°C)范围进行了优化。DS1000-IND是一个产品系列,可在工业温度范围使用。其他部件可以定制为工业温度范围。

我可以添加或菊花链连接多个设备以实现更长的延迟吗?

菊花链式硅延迟线存在一个问题,随着链中封装数量的增加而增加。设计中的电压斩波稳定电路会在输出端引起轻微的时间抖动(完全符合规格,对电路几乎透明)。当封装以菊花链形式连接时,时间抖动是累积的,会降低下线级的精度。如果将四到六个包串联在一起,则结果通常是不可接受的。

如何菊花链连接并行 STC 的各个阶段?

当添加到系列中时,每个阶段都会增加一些抖动。在大多数情况下,这不会成为问题。用户报告说,菊花链是实现非标准串联延迟的便捷方法。

审核编辑:郭婷

-

CMOS

+关注

关注

58文章

6242浏览量

243585 -

比较器

+关注

关注

14文章

1937浏览量

112157 -

逆变器

+关注

关注

306文章

5240浏览量

218123 -

延迟线

+关注

关注

0文章

38浏览量

19253 -

STC

+关注

关注

14文章

299浏览量

70507

发布评论请先 登录

全硅延迟线的设计考虑因素

全硅延迟线的设计考虑因素

评论