为了利用USB4™(或Thunderbolt™ 4)的完整数据速率,通常在超高速数据线上使用重定时器或转接驱动器设备。这对ESD保护方法有影响,这可能并不完全明显。典型的USB3.2系统的走线长度可能超过100 mm。重定时器或转接驱动器器件的放置将导致走线长度显著缩短,从而对信号走线电感产生积极影响。根据经验,10 mm走线长度大约相当于3-3.5 nH的电感。虽然从信号完整性的角度来看,降低走线电感肯定是可取的,但降低ESD保护和受保护系统之间的电感也会增加受保护系统看到的峰值电压。

ESD失效机制和走线长度

受保护IC有两种主要的ESD故障机制。一种是由流入IC的剩余电流引起的热故障。在准静态情况下,该电流取决于进入IC的路径的导通电阻比与通过ESD保护的接地路径的导通电阻比。

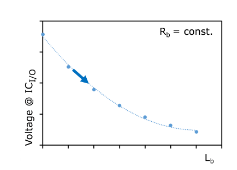

第二种ESD故障机制超过了受保护系统收发器中栅极氧化物上的最大电场强度。为了降低电场强度,应将受保护芯片看到的峰值钳位电压降至最低。这种动态效应不能通过准静态考虑来捕捉。减小信号走线长度可减小电路板电感Lb在外部ESD保护和受保护芯片之间。对于其他不变的系统,这将增加危险的ESD峰值电压。

确定峰值抑制性能

为了应对这种影响,Nexperia刚刚发布了首款采用最新TrEOS技术的产品,这些产品针对峰值电压降低进行了优化。但是,如何发现哪种保护设备适合保护哪种系统呢?为支持设计工程师为其系统选择合适的保护器件,Nexperia为其高速ESD器件提供了全动态系统高效ESD设计(SEED)仿真模型。与准静态模型相反,全动态 SEED 模型还允许对峰值电压抑制进行系统级仿真。

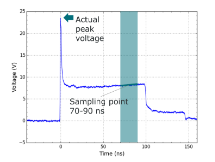

确定ESD保护器件的峰值抑制性能并不像人们想象的那么简单。ESD枪设计用于测试完整系统的鲁棒性,但缺乏显示敏感收发器系统中峰值电压的精度。即使在未更改的系统中的两次测量之间,差异也可能很大。与ESD喷枪测量相比,传输线脉冲(TLP)测量可以显示出显着更高的再现性。但是,数据手册通常仅显示保护器件导通时采样的标准TLP I(V)曲线。选择100 ns脉冲长度来评估IEC61000-4-2 ESD脉冲的热故障模式。

为了评估峰值电压,需要进行非常快速的TLP(vfTLP)测量。这是对脉冲开始时发生的短过电压的最准确测量,可以在第一个纳秒内研究超过瞬态触发效应。

重新定时器在运行

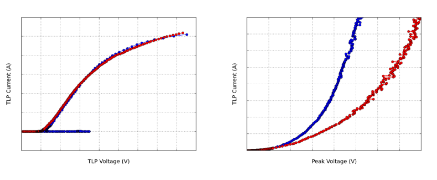

为了举一个实际的例子,我们比较了两个具有相当电容的ESD保护器件的钳位。虽然两个器件的标准TLP钳位电压相当,因此ESD脉冲的第二个峰值的能量抑制,但我们直观地假设红色器件比蓝色器件具有更好的峰值电压抑制。上升时间选择为600 ps,以表示IEC61000-4-2脉冲的第一个快速峰值。

a) 100 ms TLP I(V) 测量和 b) 0.6 / 5 ns VFTLP I(V) 测量

在第一种情况下,尽管TLP触发电压更高VT1蓝色曲线表示,同一器件在保护范围内提供较低的vfTLP峰值电压,从而导致IC上的峰值电压较低。另一个好处是,蓝色器件的反向关断电压更高 VRWM允许在 USB 类型 C® 环境中直接放置在连接器后面。这样做的好处是在保护和IC之间增加了更多的电感,从而进一步降低了峰值电压。在白皮书《为 USB4 选择 ESD 保护器件》中,我们讨论了 USB Type-C 可以将具有更高电压规格限制的 USB3.2 系统连接到 USB4 系统。因此,USB4 的保护器件应该向后兼容 USB3.2 关于 VRWM当放置在连接器的正后方时。在此位置,它还为交流耦合电容提供保护。

提供实用的解决方案

在USB4环境中使用重定时器或转接驱动器器件将缩短ESD保护和受保护IC之间的信号走线,从而降低电路板走线电感Lb.虽然较短的走线肯定有利于信号完整性,但在比较其他不变的系统时,其较低的电感会增加峰值ESD电压。为了应对这种影响,Nexperia可以提供采用最新TrEOS技术的器件,这些器件针对峰值电压抑制进行了优化。

审核编辑:郭婷

-

ESD

+关注

关注

49文章

2221浏览量

174321 -

驱动器

+关注

关注

54文章

8438浏览量

148091 -

定时器

+关注

关注

23文章

3261浏览量

116210

发布评论请先 登录

相关推荐

基于FPGA的超高速FFT硬件实现

安捷伦科技宣布发布USB 3.0超高速物理层一致性测试解决方

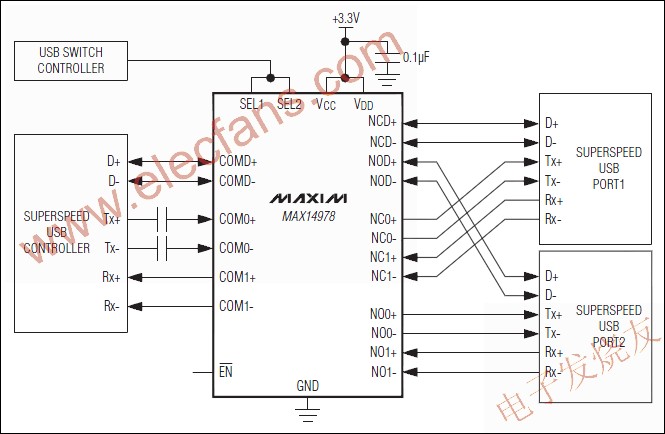

MAX14978 超高速USB模拟开关

安捷伦与NTS携手推进超高速USB 3.0测试

Mouser带来最新USB 3.0技术: 赛普拉斯FX3和恩智浦USB 3.0超高速转接驱动器

超高速USB3.0主机和设备控制器接口应用方案

如何检测复杂的超高速调制光信号?

TPDxEUSB30用于超高速USB 3.0接口的2、4通道ESD保护数据表

将USB4重新驱动到超高速

将USB4重新驱动到超高速

评论