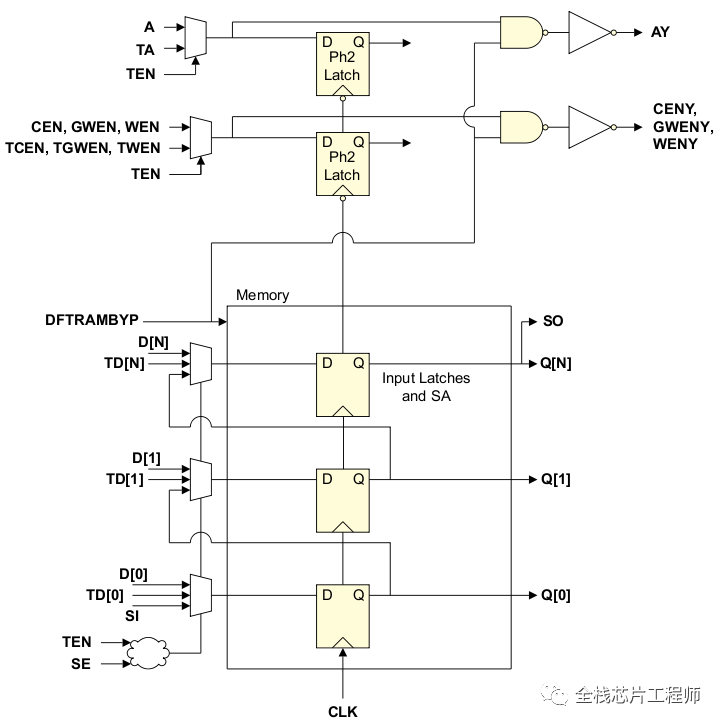

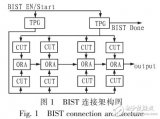

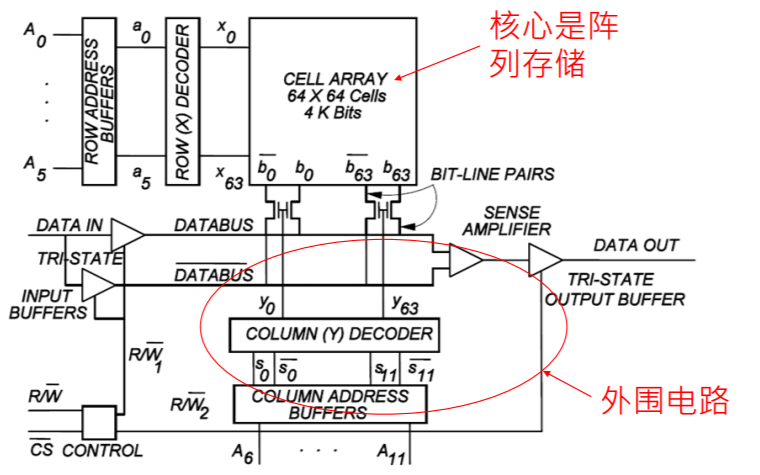

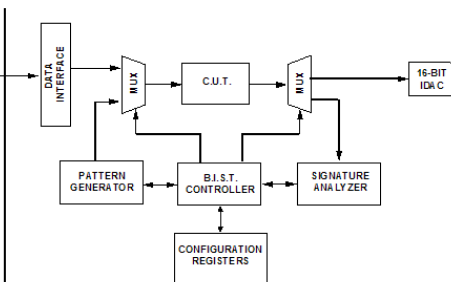

SRAM的MBIST测试结构如下:

SRAM的MBIST测试波形:

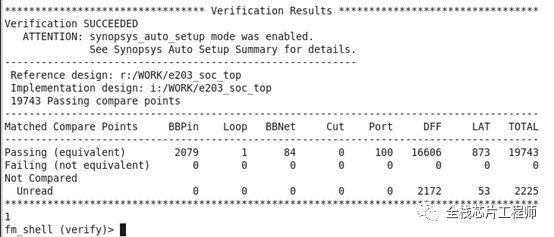

SRAM BIST电路完成插入后,需要做一个formal check,保证Mbist插入后,logic function不发生错误改变。Formal check需要注意常量设置,具体参见知识星球的详细解释。

此处分享2个经典问题:

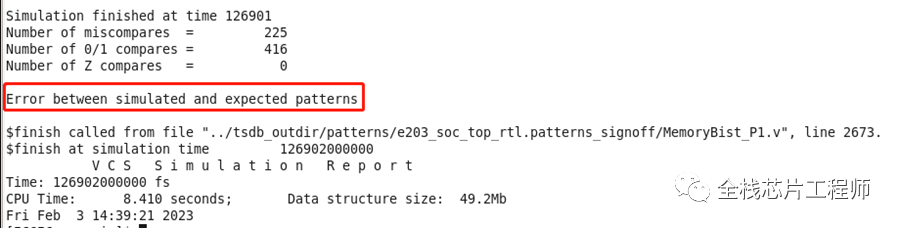

定位1:

通过trace TDO信号,一直追踪到SRAM的Q端,发现Q端数据输出是X态,通过分析发现本质上还是时钟问题,什么问题呢?

就是SRAM MBIST_CLK延时下来刚好和SRAM测试地址TADDR的跳变完全对齐了,造成了SRAM的memory model的建立/保持时间违例,SRAM model在timing违例情况下Q端输出为X态。下文具体内容请移步知识星球查看。

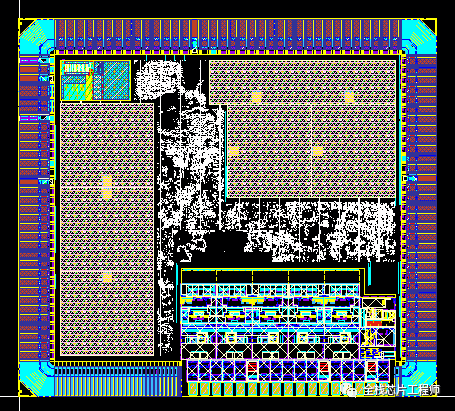

欢迎加入【全栈芯片工程师】知识星球,手把手教你设计MCU、图像传感器、ISP图像处理,从算法、前端、DFT到后端全流程设计。

实战MCU+ISP图像处理芯片版图

实战ISP图像算法效果

审核编辑 :李倩

-

芯片

+关注

关注

456文章

50886浏览量

424202 -

mcu

+关注

关注

146文章

17171浏览量

351445 -

图像传感器

+关注

关注

68文章

1903浏览量

129577

原文标题:MCU芯片的Memory Bist设计实战(一)

文章出处:【微信号:全栈芯片工程师,微信公众号:全栈芯片工程师】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

基于BIST利用ORCA结构测试FPGA逻辑单元的方法

DFT和BIST在SoC设计中的应用

数字BIST的基本原则

ZC706 BIST编译在Linux上失败

S32K BIST当sw调用api Bist_Run() 以启动bist时,mcu重置了怎么处理?

基于LFSR优化的BIST低功耗设计

针对FPGA可编程逻辑模块的离线BIST测试方法

Memory芯片的测试资料详细说明

RISC-V MCU开发实战 (二):SD初应用

MCU芯片的Memory Bist设计实战(一)

MCU芯片的Memory Bist设计实战(一)

评论