2022年,集成电路半导体行业最热的头条是“EDA被全面封锁”。如何突破EDA封锁,成为行业发展的关键词,也是群体焦虑。在全球市场,有人比喻EDA是“芯片之母”,如果没有了芯片,工业发展和社会进步将处处受制,EDA的重要性也上升到了战略性高度。尽管国际封锁形势严峻,但睿智的中国科技人擅于把危机化为机会,从《加快自动研发应用,让工业软件不再卡脖子》,到《破解科技卡脖子要打好三张牌》,即一要打好“基础牌”,提升基础创新能力;二要打好“应用牌”,加强对高精尖国货的应用;三是要打好“人才牌”,让人才留得住、用得上、有发展……,各种政策、举措和实际行动,处处彰显了我们中国科技的发展韧性。

我们EDA探索频道,今天迎来了第9期的精彩内容——控制阈值电压,下面就跟着小编一起来开启今天的探索之旅吧~

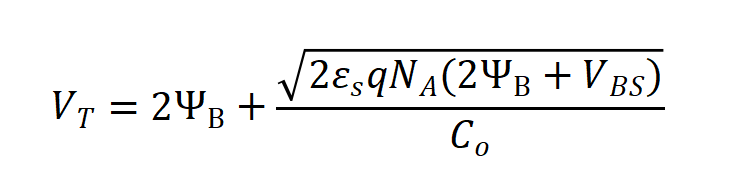

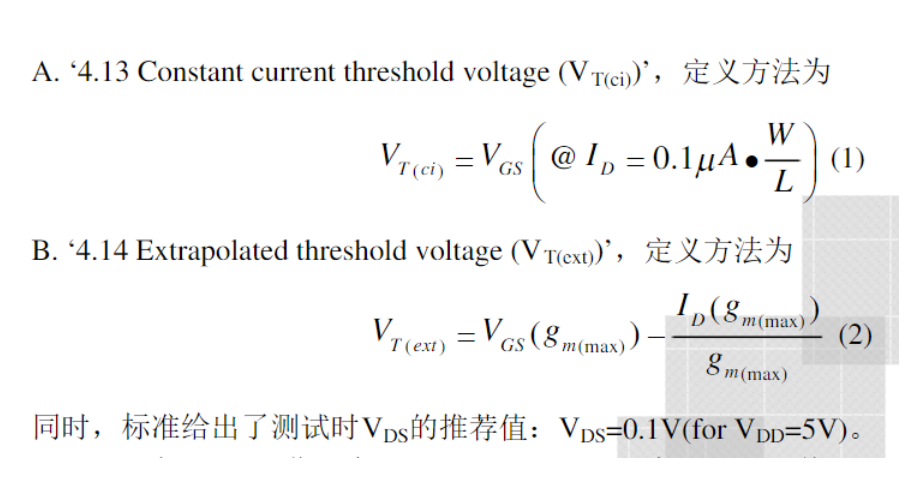

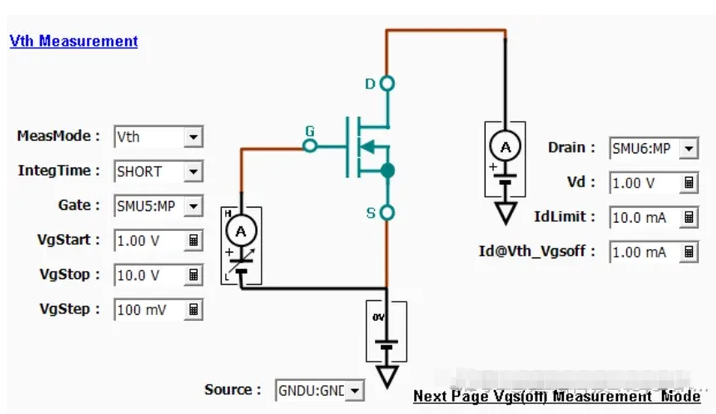

MOSFET的最重要参数之一便是阈值电压,理想的阈值电压由以下公式给出。

然而,当我们考虑到固定氧化物电荷的影响和功函数的差异时,就会出现一个平带电压移动。

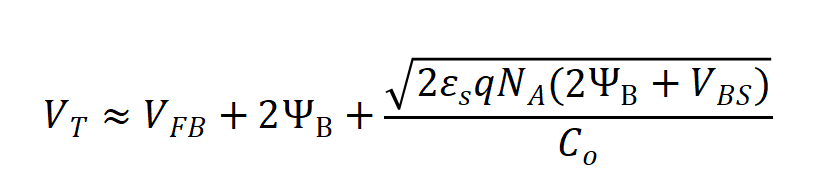

此外,衬底偏压也能影响阈值电压。当在衬底和源极之间施加反向偏压时,耗尽区被加宽,实现反转所需的阈值电压也必须增加,以适应更大的Qsc。

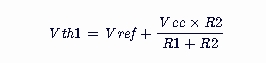

考虑到这些因素,得到的阈值电压表达式为:

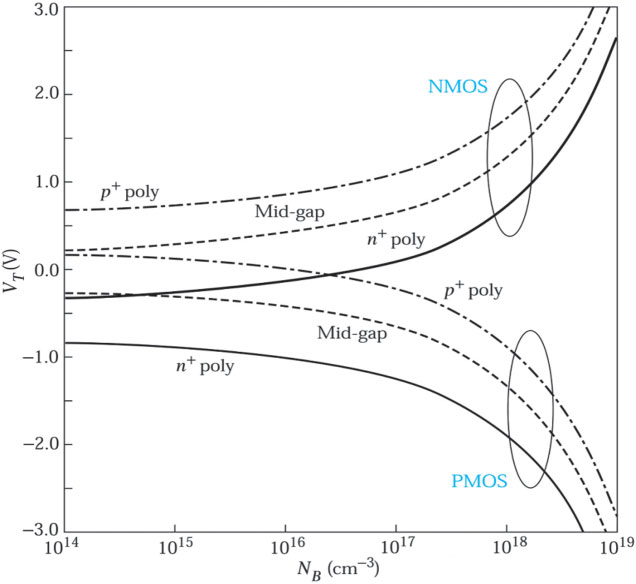

图:NMOS与PMOS管在不同栅极条件下的计算结果。栅氧化层为5nm, VBS=0, Qf=0

引自S.M.Sze“SemiconductorDevicesPhysicsandTechnology”

上图是一个计算结果,对应的是不同栅极的NMOS和PMOS的阈值电压与衬底掺杂的关系。本征的多晶硅栅极相当于4.61eV的功函数。

精确控制集成电路中MOSFET的阈值电压对电路的可靠性至关重要。通常情况下,阈值电压是通过向沟道区的离子注入来调整的。例如,经过表面氧化层的硼注入通常被用来调整n沟道MOSFET的阈值电压(带p型衬底)。通过增大沟道的掺杂浓度来提升阈值电压。由于离子注入的能量和剂量是可以精确控制的,可以由此实现对阈值电压的精确控制。同理,向p型沟道注入少量的硼可以减少VT。

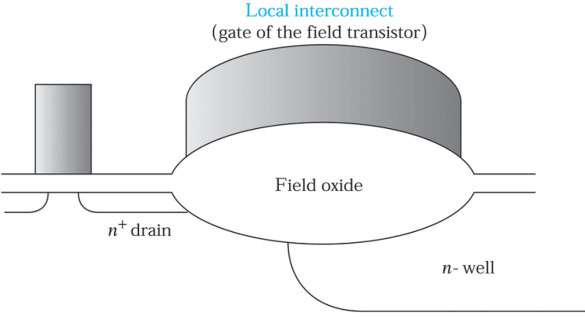

我们还可以通过改变氧化物的厚度来控制VT。随着氧化层厚度的增加,n沟道MOSFET的阈值电压变得更正,p沟道MOSFET的阈值电压变得更负。这是由于在一定的栅极电压下,氧化物越厚,相应的场强越小。这种方法被广泛用于隔离在芯片上的晶体管。下图显示了隔离氧化层(也称为场氧化层)在n+扩散区和n阱之间的横截面。

图:寄生的场区晶体管横截面示意图

引自S.M.Sze“SemiconductorDevicesPhysicsandTechnology”

n+扩散区是n型沟道区或者MOSFET的源区或漏区。MOSFET的栅极氧化物要比场氧化物薄得多。当电力线在场氧化层上形成时,就会产生一个寄生的MOSFET,也称为“场区晶体管”,其n+扩散区和n阱区分别作为源极和漏极。

场区晶体管的VT通常比正常的薄栅氧化物的VT大一个数量级。在电路正常运行时,场效应晶体管不会被打开。因此,场氧化层在n+扩散区和n孔区之间提供了良好的隔离。

衬底偏压也可以用来调整阈值电压。源极和衬底可能不在同一电位上。在器件正常工作时,源和衬底之间的p-n结必须是零或反向偏压。如果VBS为零,衬底的表面电位为2ψB。当施加反向衬底-源极偏压(VBS>0)时,沟道中的电子电势则会拉高到高于源极的电势的水平。沟道中的电子将被横向推到源极。如果要保持在强反型条件下沟道中的电子密度保持不变,栅极电压必须提高到2ψB+VBS。

审核编辑 :李倩

-

MOSFET

+关注

关注

147文章

7156浏览量

213147 -

电压

+关注

关注

45文章

5598浏览量

115702 -

阈值

+关注

关注

0文章

123浏览量

18490

原文标题:EDA探索丨第9期:控制阈值电压

文章出处:【微信号:hzwtech,微信公众号:鸿之微】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

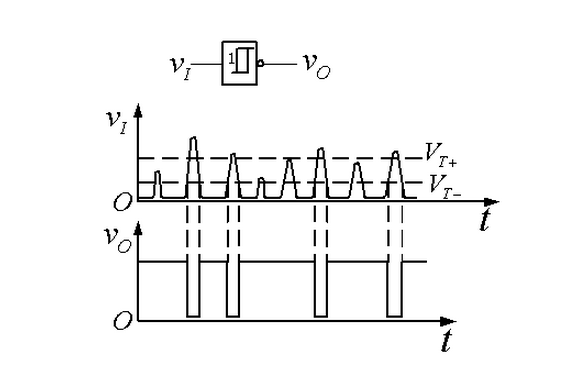

解答74HC14中正向阈值电压和负向阈值电压是什么/电压为多少

MOS管阈值电压的问题

如何解释阈值电压与温度成反比这个现象?

阈值电压的计算

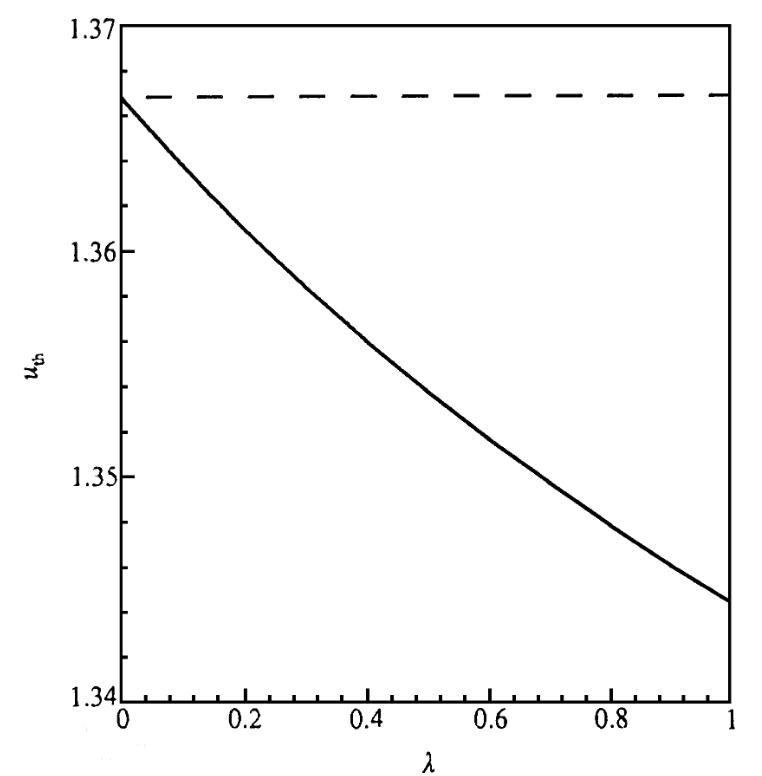

MOS管阈值电压与沟长和沟宽的关系

如何突破EDA封锁 卷起来的阈值电压

NMOS晶体管的阈值电压公式 nmos晶体管的阈值电压与哪些因素有关

影响MOSFET阈值电压的因素

什么是MOS管亚阈值电压?MOSFET中的阈值电压是如何产生的?

浅谈影响MOSFET阈值电压的因素

MOSFET阈值电压是什么?影响MOSFET阈值电压的因素有哪些?

滞回比较器的阈值电压如何确定?

控制阈值电压

控制阈值电压

评论