数字硬件建模SystemVerilog-结构体(二)

结构体

结构体用于将多个变量组合在一个通用名称下。设计通常具有逻辑信号组,例如总线协议的控制信号,或状态控制器内使用的信号。结构体提供了将这些相关变量捆绑在一起的方法。结构体中的所有变量都可以单个赋值,或者每个变量都可以单独赋值。结构体包可以复制到具有相同定义的另一个结构体,并通过模块端口、任务或函数进出。

结构体复制

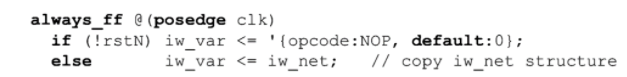

一个自定义结构体可以复制到另一个自定义结构体,只要这两个结构体是从同一个自定义结构体定义声明的。以下示例使用了上节中所示的结构体定义和声明。

匿名结构体不能作为一个整体复制,但可以一次复制一个成员:

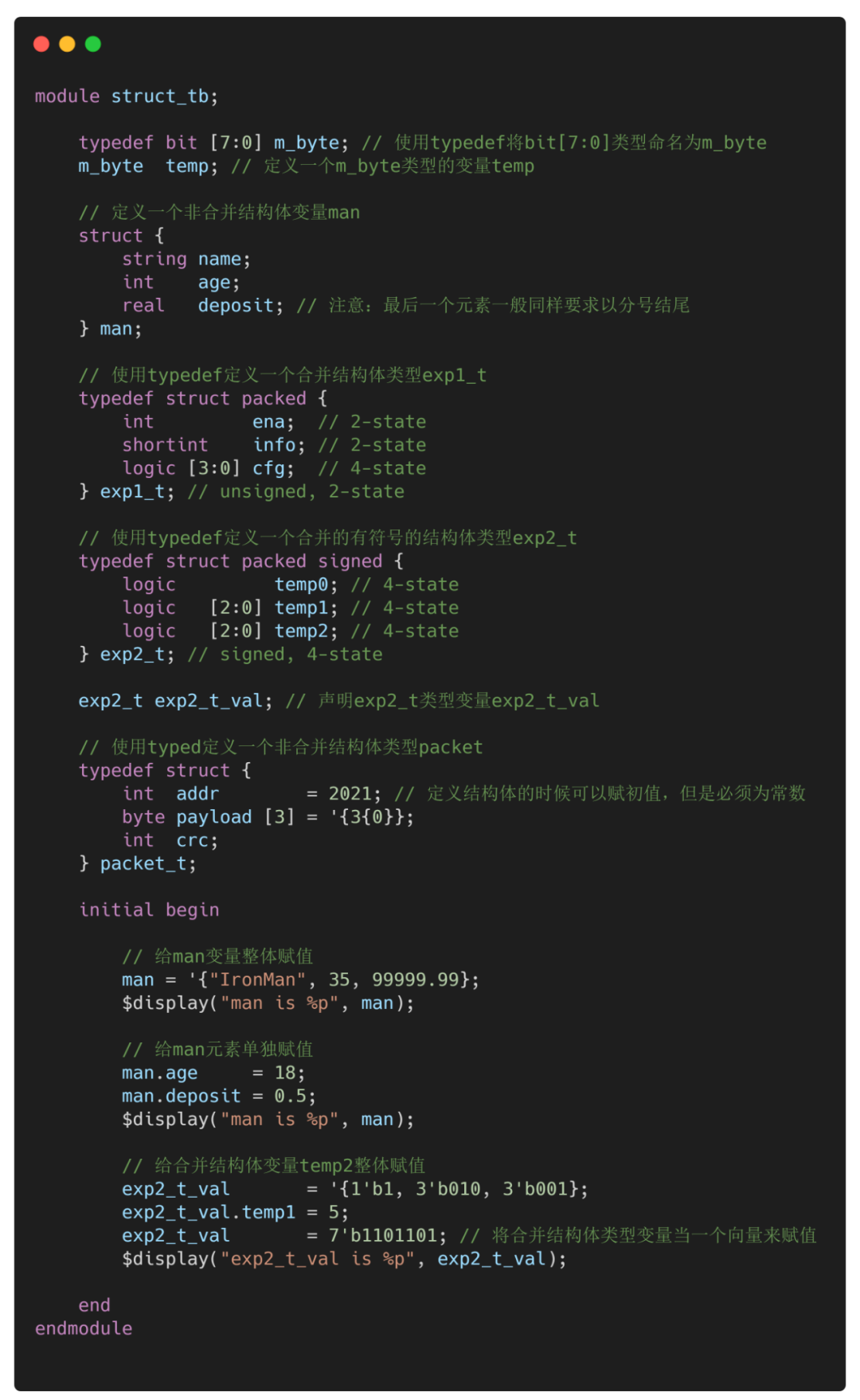

压缩和非压缩结构体

默认情况下,结构体会被非压缩的。这意味着结构体的成员被视为独立变量或常量,并以一个共同的名称分组在一起。SystemVerilog没有指定软件工具应该如何存储非压缩结构体的成员。不同的软件工具具对于结构体的存储分布也是不同的。

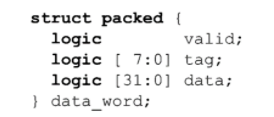

通过使用关键字packed,将结构体显式声明为压缩结构体。

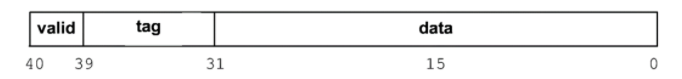

压缩结构体以与向量相同的形式将结构体的所有成员存储为连续位。结构体的第一个成员是向量最左边的字段。结构体中最后一个成员的最右边的位是向量的最低有效位,编号为位0。如图4-2所示。

图4-2:压缩结构体存储为向量

压缩结构体的所有成员都必须是整数值。整数值是可以表示为向量的值,例如byte、int和使用bit或logic类型创建的向量。如果结构体的任何成员不能表示为向量,则该结构体不能被压缩。这意味着压缩结构体不能包含实数或短实数变量、非压缩结构体、非压缩联合体体或非压缩的数组。

引用压缩结构体和结构体成员。压缩结构体可以复制,或分配一个结构体表达式值列表,方法与非压缩结构体相同。压缩结构体的成员可以通过成员名称引用,方式与非压缩结构体相同。

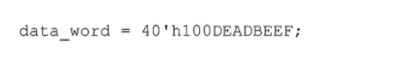

压缩结构体也可以被视为一个向量。因此,除了结构体分配,向量值还可以分配给压缩结构体

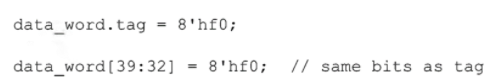

向量赋值是合法的,因为赋值左边的结构体成员已压缩在一起,形成一组连续的位,方式与向量相同。因为压缩结构体存储为一组连续的位,所以对压缩结构体执行向量操作也是合法的,包括位选择和部分选择。以下两个赋值都将分配给data_word的tag成员:

可以在向量上执行的数学运算、逻辑运算和任何其他运算也可以在压缩结构体上执行。

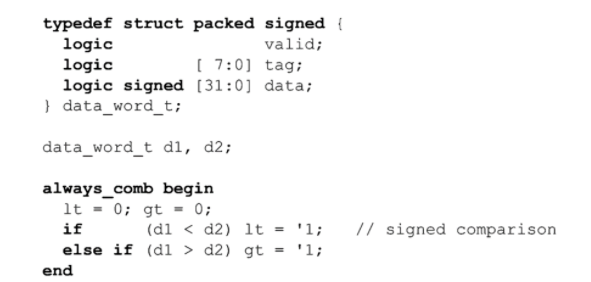

有符号压缩结构体。压缩结构体可以用signed和unsigned关键字声明。当在运算或关系运算中用作向量时,这些修饰符会影响整个结构体的识别方式。它们不会影响结构体成员的识别方式。结构体的每个成员都被视为有符号或无符号,这取决于该成员的类型声明。压缩结构体的部分选择是无符号的,与向量的部分选择相同。

通过端口传递结构体

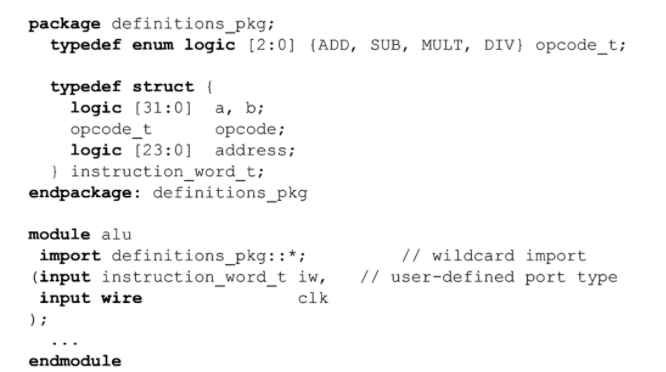

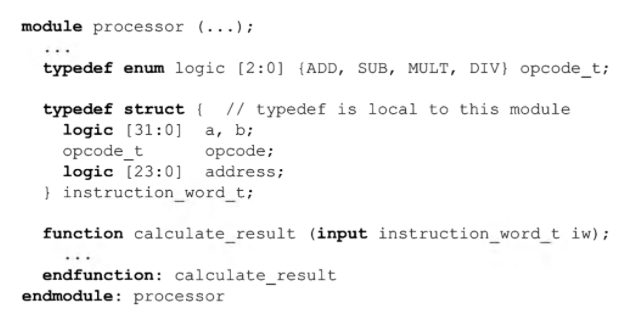

自定义结构体可以通过模块和接口的端口传递,结构体必须首先使用 typedef 定义为用户自定义数据类型,然后才允许将模块或接口的端口声明为结构体类型。

非压缩的结构体必须是自定义结构体,才能通过端口传递该结构体。与端口的连接必须是与端口类型完全相同的结构体。也就是说,端口和端口两侧的连接都必须从相同的typedef定义声明。此限制仅适用于非压缩结构体。通过模块端口的压缩结构体被视为向量。端口的外部连接可以是相同类型的压缩结构体,也可以是任何类型的向量。

通过将任务或函数参数声明为结构体类型,自定义结构体也可以作为参数传递给任务或函数。

当调用一个任务或函数时,如果该任务或函数有一个非压缩的结构体作为正式参数菜单,则必须将一个完全相同类型的结构体传递给该任务或函数。压缩结构体形式参数被视为向量,可以传递给任何类型的向量。

传统的Verilog与结构体

最初的Verilog语言没有一种方便的机制来将常见信号收集到一个组中。在传统的Verilog样式的模型中,工程师必须使用特殊的分组方法,例如命名约定,其中一组中的每个信号都以一组公共字符开始或结束。最初的Verilog语言也无法通过模块端口或任务和函数传递信号集合,每个信号都必须通过单独的端口或参数传递。

在原始Verilog语言中添加结构体是一种强大的RTL建模构造,反之亦然。它提供了一种更简洁、更直观、更可重用的复杂模型功能建模方法。包中定义的自定义结构体可以在多个模块中重复使用,也可以在用于验证RTL模型的验证测试台中重复使用。

综合指导

非压缩结构体和压缩结构体都是可综合的。综合工具支持结构体通过模块端口传递 , 也支持作为输入或输出传递给任务和函数 , 也支持使用成员名和值的列表对结构体进行赋值。

综合编译器可能比压缩结构体更好地优化非压缩结构体。非压缩结构体允许软件工具确定存储或实现每个结构体成员的最佳方式,而压缩结构体则决定如何组织每个成员。

-

控制器

+关注

关注

112文章

16487浏览量

179804 -

控制信号

+关注

关注

0文章

169浏览量

12053 -

结构体

+关注

关注

1文章

130浏览量

10888

发布评论请先 登录

相关推荐

round robin 的 systemverilog 代码

(2)打两拍systemverilog与VHDL编码 精选资料分享

使用结构体的主要作用

SystemVerilog Assertion Handbo

SystemVerilog的断言手册

基于事件结构的SystemVerilog指称语义

基于SystemVerilog的I2C总线模块验证

共用体和结构体的区别

数字硬件建模SystemVerilog-结构体

SystemVerilog中至关重要的结构体和自定义类型

SystemVerilog的结构体-1

SystemVerilog的结构体-2

SystemVerilog的结构体-2

评论