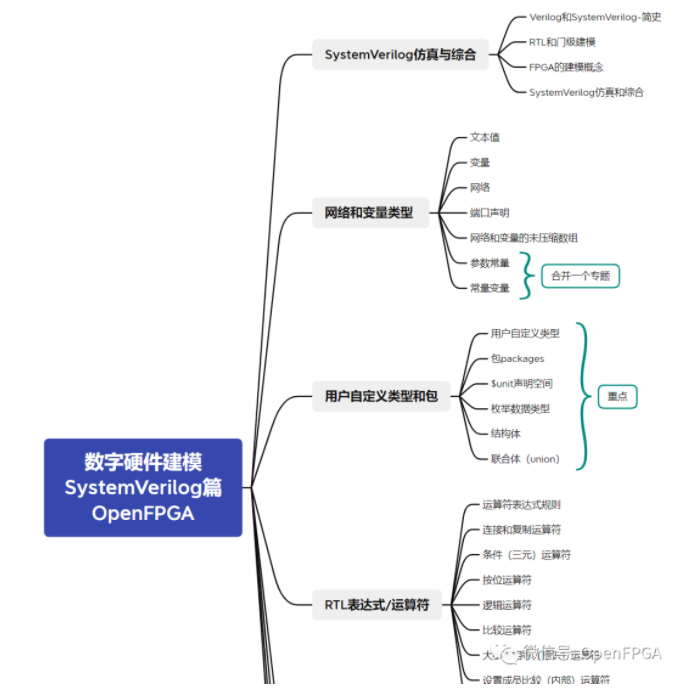

数字硬件建模SystemVerilog-逻辑运算符

经过几周的更新,SV核心部分用户自定义类型和包内容已更新完毕,接下来就是RTL表达式和运算符。

逻辑运算符

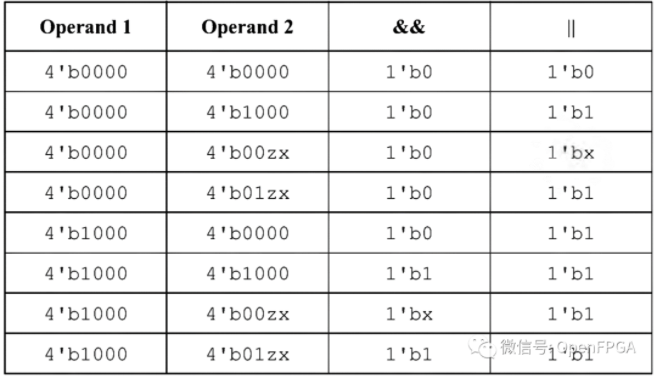

逻辑运算符对其操作数求值,并返回一个值,该值指示求值结果是真还是假(true or false)。例如,运算a && b测试a和b是否都为真,如果两个操作数都为真,则运算符返回真。否则,运算符返回false。

逻辑运算符返回值。SystemVerilog没有内置的true或false布尔值。相反,逻辑运算符的返回使用逻辑值1’b1(一个一位宽的逻辑l)表示真,1’b0表示假。逻辑运算符还可以返回1’bx,指示仿真无法确定实际逻辑门的评估结果是否为真或假的模糊条件。

判断一个表达式是真是假。要确定操作数是真是假,SystemVerilog使用以下规则:

- 如果所有位均为0,则操作数为假

- 如果所有位均为1,则操作数为真

- 如果所有位均为X或Z,且没有位为1,则操作数未知X

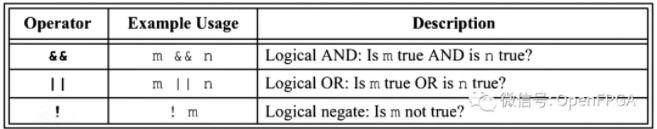

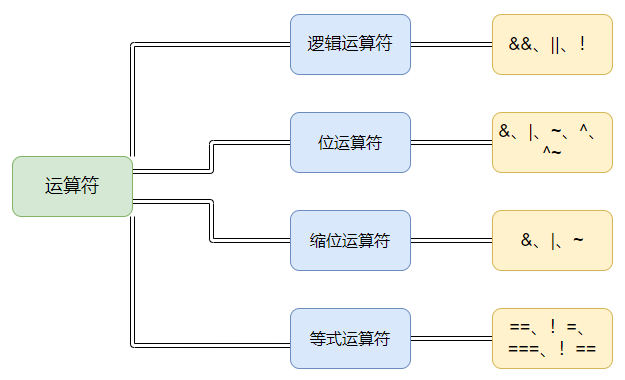

表5-1列出了RTL综合编译器普遍支持的逻辑运算符。

表5-11:RTL建模的逻辑运算符

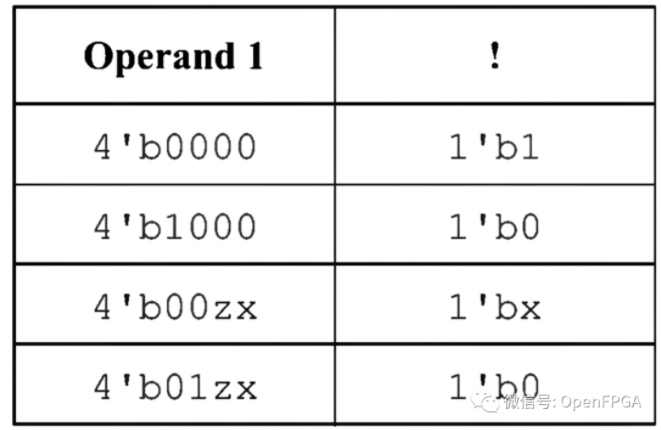

逻辑求反运算符通常被称为“not运算符”,它是“not true”的缩写。

逻辑运算符通过对每个操作数进行归约OR来执行其运算,从而产生一个1位结果。然后对该结果进行求值,以确定其为真还是假。对于not运算符,1位的结果首先被反转,然后求值为真或假。

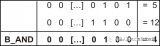

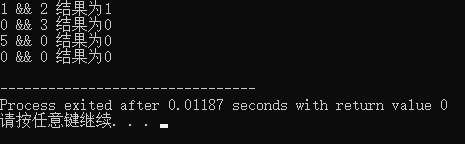

表5-12和5-13显示了这些逻辑运算符对几个示例值的结果。

表5-12:逻辑AND and OR运算的示例结果

表5-13:逻辑求反运算的示例结果

逻辑求反运算符(!)和按位反转运算符(~)之间的区别

练习题目《HDLBits: 在线学习 SystemVerilog(一)-Problem 2-6》Problem 4

应注意不要混淆逻辑求反运算符(!)以及按位反转运算符(~)。求反运算符对其操作数执行真/假求值,并返回表示真、假或未知结果的1位值。按位反转运算符对操作数的每一位(补码)执行逻辑反转,并返回与操作数相同位宽的值。

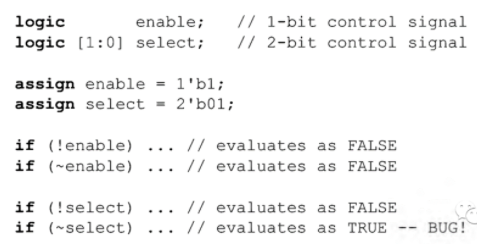

在某些操作中,这些操作的结果恰好相同,但在其他操作中,它们返回的值非常不同。当运算符与决策语句一起被错误使用时,这种差异可能导致错误代码。考虑下面的例子:

前面代码片段的最后两行之所以不同,是因为这两个运算符的工作方式不同——逻辑求反运算符(!)通过将两位相加或相减,对2位选择执行真/假计算,然后反转1位结果,按位反转运算符(~)只反转2位选择向量的每一位的值,并返回2位结果。if语句然后对2位向量进行真/假测试,该向量的计算结果为真,因为反转后的值仍有一位设置为1。

| 最佳实践指南5-1 |

|---|

| 使用按位反转运算符反转值的位,不要使用按位反转运算符对逻辑求反运算符求反。相反,使用逻辑求反运算符来否定真/假测试的结果。不要使用逻辑求反运算符反转值。 |

| 最佳实践指南5-2 |

|---|

| 仅使用逻辑求反运算符求反来测试标量(1位)值,而不是 对向量执行真/假测试。 |

如果向量的任何位为1,逻辑运算将返回true,这可能会导致在测试特定位时出现设计错误。计算向量值时,使用等式或关系运算符测试可接受的值。

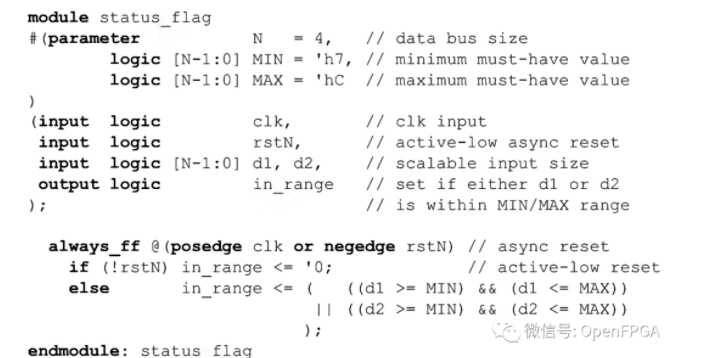

示例5-7说明了一个小型RTL模型,该模型使用逻辑NOT、逻辑AND和逻辑OR运算符。该设计是一个逻辑比较器,如果两个数据值中的任何一个在可配置的值范围内,则设置一个flag。

示例5-7:使用逻辑运算符:当值在某个范围内时设置flag

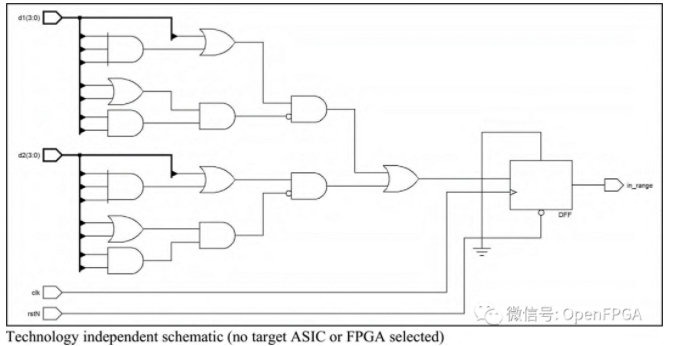

图5-7显示了示例5-7中的RTL模型综合结果

图5-7:示例5-7的综合结果:逻辑运算符(范围内比较)

不可综合的逻辑运算符

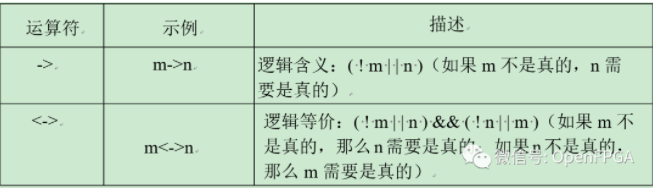

SV-2009增加了两个额外的逻辑运算符,它们是蕴涵和等价运算符,在本文编写时RTL综合编译器通常不支持这些运算符。表5-14列出了这两个运算符的标记和描述。

表5-14:不可综合逻辑运算符

-

操作

+关注

关注

0文章

43浏览量

18870 -

逻辑

+关注

关注

2文章

833浏览量

29462 -

运算符

+关注

关注

0文章

172浏览量

11078

发布评论请先 登录

相关推荐

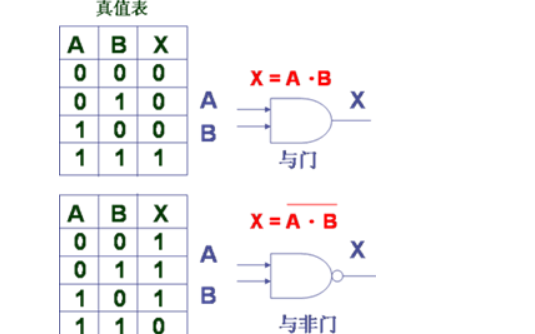

单片机的逻辑运算符和位运算符是什么?数字电路中的常用符号

Bug之逻辑运算符优先级分享!

【通信专栏】附录一:STM32单片机C语言基础/逻辑运算/按位运算/结构体/宏定义 精选资料分享

Bitwise 逻辑运算符进行设计

C语言逻辑运算符优先次序

verilog的逻辑运算符

什么是逻辑运算符

什么是逻辑运算符

评论