为高效的低损耗功率开关应用选择低导通电阻 MOSFET?不要忘记检查是否有隐藏的妥协。

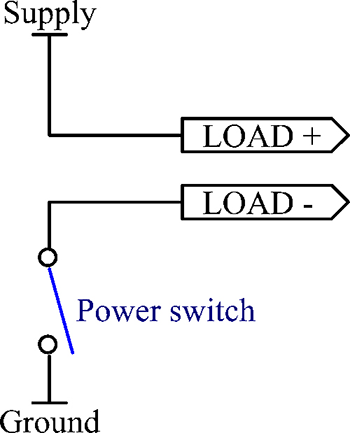

耗电应用要求提高系统效率,以满足消费者和监管部门对更清洁空气和减少碳足迹的要求。这推动了对理想的“无损耗”电源开关的需求,在大多数现代电子系统中,这种开关是通过功率MOSFET实现的。

完美的电源开关在关闭时具有无限电阻,打开时具有零电阻,并且关闭和打开之间的转换将是瞬时的,而不会引起尖峰或其他瞬态噪声。然而,在MOSFET的现实世界中,关断时的电阻是有限的,总会有一些漏电流(IDSS),并且半导体制造商尝试时,打开时的电阻(RDS(开启)) 永远不会为零。但这并不能阻止他们试图尽可能低。

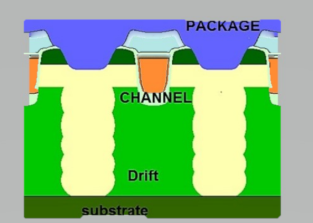

降低R的各种方法DS(开启)可以使用沟槽MOSFET,每种MOSFET都可能产生不必要的副作用,从而影响各种应用的性能。

对于典型的功率MOSFET,沟槽结构的“有源”部分包含在硅的顶部几μm内,大部分损耗发生在该区域内。剩余的硅,称为基板,在制造过程中提供机械稳定性。减小基板厚度可以显著降低MOSFET的电阻和热阻,但背面研磨会产生额外的成本。

细胞间距

较低的RDS(开启)大多数供应商通常通过添加更多并行通道来实现,这通常会降低电池间距,这会导致热不稳定,因为相邻电池会导致温升影响通道的阈值电压。它还会增加MOSFET的电容,从而影响开关性能。相反,SOA可能会因窄细胞间距而受到严重影响。超结技术使用带有P型支柱的更深沟槽可以在不降低电池间距的情况下降低通道电阻,并且不会影响SOA性能。

漂移电阻,通过改变漂移区域的掺杂 RDS(开启)可以减少,但 IDSS漏电流和VDS关断条件下的额定电压可能会受到负面影响。我DSS通常用于制造最终测试以筛选出有缺陷的设备,接受更高的泄漏电流可能意味着在最终测试期间可能未检测到更多有缺陷的产品

沟槽阻力

封装电阻

通过使用铜夹和漏极焊盘代替键合线,可以降低封装电阻,结合使用多个源极引脚,在产品的整个生命周期内,还将对电感、额定电流、热性能和鲁棒性产生积极影响。

不言而喻,降低 RDS(开启)有时会导致不必要的权衡,要求苛刻的应用(如电源ORing,热插拔,电机驱动和负载切换)可能无法接受这些权衡 - 也不应该接受。

下一页 PowerS3 MOSFET – 具有软恢复功能的超快速开关

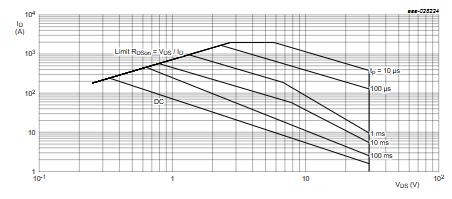

Nexperia最新加入NextPowerS3产品组合,将超结技术与铜夹式LFPAK封装相结合,提供具有竞争力的RDS(开启)走向市场。最新器件提供 0.5 mΩ(典型值)、高达 380 A 的直流额定电流,此外还有 6 倍的线性模式 (SOA) 性能(见下图)和极具竞争力的 Q 值g, 1DS(开启)品质因数。

新部件在不影响其他重要参数的情况下提高了性能。

PSMNR58-30YLH安全操作区域;连续和峰值漏极电流与漏源电压的关系

审核编辑:郭婷

-

电源

+关注

关注

184文章

17724浏览量

250261 -

MOSFET

+关注

关注

147文章

7171浏览量

213375 -

SOA

+关注

关注

1文章

289浏览量

27488

发布评论请先 登录

相关推荐

什么是电源开关,它们在哪里使用?

寻找完美的电源开关

寻找完美的电源开关

评论