2022年11月17日,江苏中科智芯先进封装研究院(API)正式揭牌成立,研究院将聚焦在半导体高端封装互连技术、晶圆级扇出型封装(Fanout WLP)和扇出系统集成(FO SiP)、高端测试技术等领域的技术研发。突破当前晶圆级先进封装及其相关芯片的技术瓶颈,特别是解决从独立自主技术到规模化量产的关键问题,形成具有自主知识产权的可产业化特色的晶圆级封装测试技术。并对封装工艺、可靠性、产品失效分析等问题进行攻关,全面掌握关键性技术,并进行成果转化;同时在人才培养、产学研结合等方面积攒经验,推动中科智芯立足集成电路封测行业创新研发新动力,保持在国内先进封装的科技创新这一赛道处于第一方阵,提高我国IC封测产业在国际半导体产业格局中的话语权和地位。

晶圆级扇出型封装研发工作主要聚焦在Chip First & Face Up or Down封装,包括封装结构验证、高温工艺导致晶圆翘曲、晶圆形貌与重布线结构的内在关系等,并充分利用模拟仿真与实验数据进行对比验证。通过扇出包封芯片的几何尺寸与塑封料的物理特性等因素的影响,优化重布线工艺与薄膜应力分布。

我们的研究成果表明晶圆级扇出封装结构中,固态颗粒状环氧塑封树脂比液体状态更适合做扇出塑封材料。塑封料的热膨胀系数对晶圆翘曲行为有显着影响,主要原因是封装结构中不同材料之间的热膨胀系数不匹配,杨氏模量决定材料的刚性;封装结构的几何形态是重要的影响因子,比如芯片厚度与晶圆翘曲程度成反比、环氧树脂层的厚度与芯片封装之面积则与晶圆翘曲成正比、在z轴方向芯片之上的额外塑封层厚度(Mold Cap)对于晶圆翘曲影响最为明显;此外,晶圆内在芯片外围与晶圆边缘处是主要应力集中区域、在重布线密集和上下层互连等区域的应力集中也比较大。

封装芯片厚度对于晶圆翘曲的影响程度大致可以总结为:

(1)薄芯片封装:芯片厚度>塑封树脂厚度>芯片在扇出封装体内面积比;

(2)厚芯片封装:塑封树脂厚度>芯片厚度>芯片在扇出封装体内面积比。

封装的几何结构也对封装质量有重要影响,额外的塑封层厚度随着其厚度变小与芯片相比的占比降低,如此工艺也可以用来改善晶圆翘曲程度。

展望未来,中科智芯在先进封装FOWLP、Bumping、WLCSP、FCCSP/FCBGA、HD(High Density)FO, 2.5D/3D IC、FO SiP、Chiplet PKG等高端封测领域,不断进行技术研发,突破现有技术瓶颈,并及时推出量产规模的产品方案,打造国际一流的封测企业。

审核编辑黄宇

-

芯片

+关注

关注

456文章

50910浏览量

424514 -

封装

+关注

关注

126文章

7936浏览量

143077 -

封测

+关注

关注

4文章

347浏览量

35193 -

先进封装

+关注

关注

2文章

414浏览量

257

发布评论请先 登录

相关推荐

安谋科技与智源研究院达成战略合作,共建开源AI“芯”生态

仁懋电子&amp;深圳先进材料研究院孙院长就芯片封装行业友好交流

深圳云芯晨半导体科技有限公司荣幸地宣布与深圳清华大学研究院携手合作

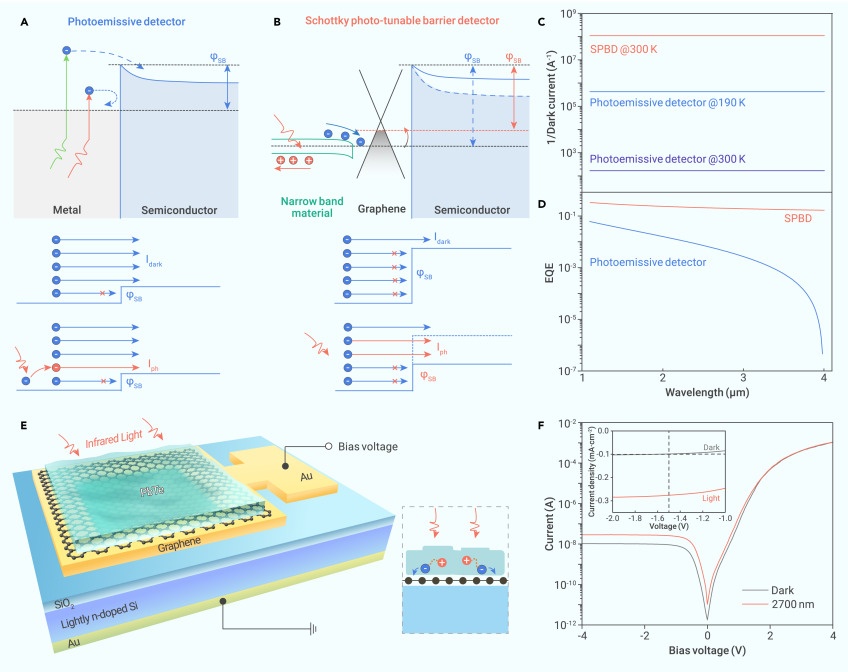

中科院重庆研究院在势垒可光调谐新型肖特基红外探测器研究获进展

长沙北斗研究院总部基地正式奠基

中山联合光电:精密光学实验室签约落地长春理工大学中山研究院

香港应用科技研究院行政总裁叶成辉先生一行来访国芯科技

浙江图灵算力研究院向知存科技颁发“年度最具影响力企业奖”

华阳精机子公司江苏中翼荣获荣获“2023年度优秀专精特新企业”

芯盾时代中标甘肃省水利水电勘测设计研究院有限责任公司

江苏中科智芯先进封装研究院与时代同行

江苏中科智芯先进封装研究院与时代同行

评论