针对特定的设计,就编译时间而言,我们要分析时间都消耗在哪些环节从而有针对性的缩短编译时间。通常,时间可能花费在加载约束上,也可能花费在某个子步骤如布局。有时面对的情况是同一设计在不同Vivado版本上运行时间出现较大差异。

report_constraints

我们先来介绍第一个命令:report_constraints。运行该命令之前需要先在Vivado Tcl Console中执行如下命令:

source report_constraints.tcl

同时最好将该脚本与待分析的dcp放置在同一目录下,这样在读取dcp时就只用提供当前工作目录即可。另外,需要注意的是report_constraints只能在Linux系统下运行。report_constraints可报告出设计中所用到的约束的种类(包括时序约束也包括非时序约束)、数量以及有效性。

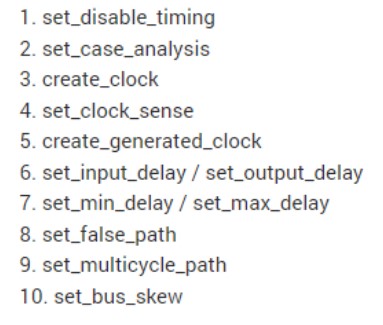

通常情况下,Xilinx建议采用如下顺序描述时序约束。除第10条set_bus_skew之外,约束的优先级也是依此顺序的,即1号优先级最低,9号优先级最高。因此,不合理的顺序以及不合理的描述方式会导致一些约束被覆盖,从而造成设计“假收敛”的现象。

对于一个复杂的设计,除了用户约束文件外,还可能会有IP的约束文件,这些约束文件可能在用户约束文件之前被调用(约束文件属性PROCESSING_ORDER为EARLY),也可能在用户约束文件之后被调用(约束文件属性PROCESSING_ORDER为LATE)。report_constraints可报告出所有约束文件所包含的约束。

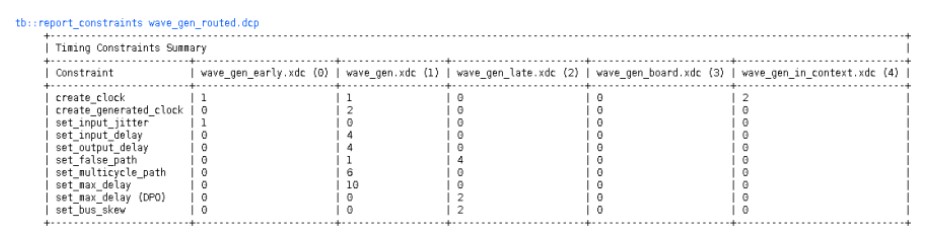

案例1:只报告上述10种时序约束的个数

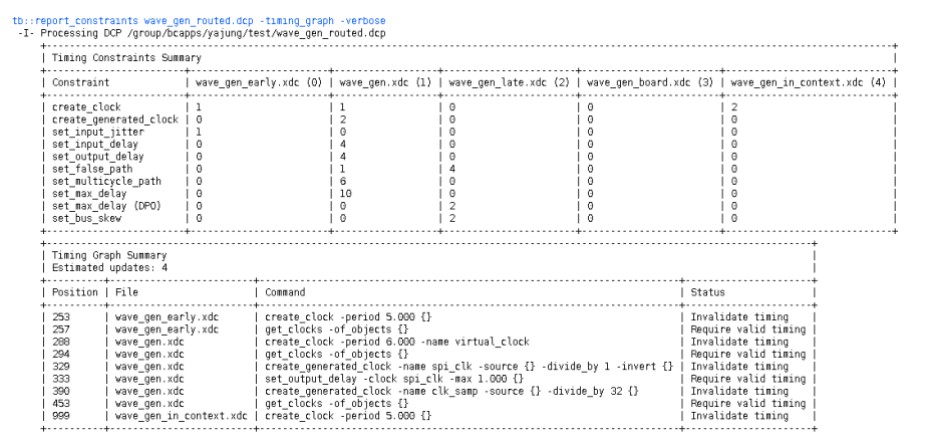

如下图所示(使用report_constraints时需要在添加作用域即tb::)。该报告第1列显示约束类型,第2列显示需要在用户约束之前调用的约束个数,第3列显示用户约束的个数,第4列显示需要在用户之后调用的约束个数,第5列显示和开发板相关的约束个数(当Part选择为开发板时),最后一列显示OOC综合时用到的约束个数。

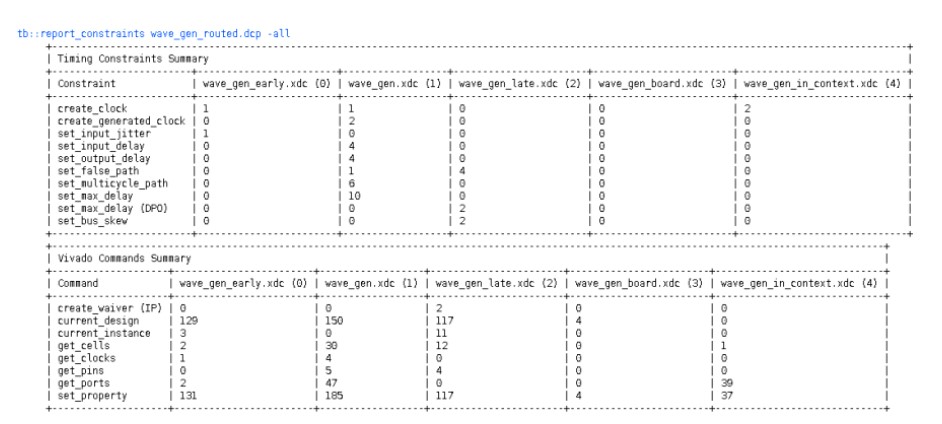

案例2:报告所有约束及约束用到的命令

通过添加-all选项,report_constratins可报告所有约束(时序约束+非时序约束)的数目以及这些约束用到的Tcl命令的个数,如下图所示。

在Vivado Commands Summary中,可以看到get_cells、get_pins、get_ports以及set_property等命令的使用情况。

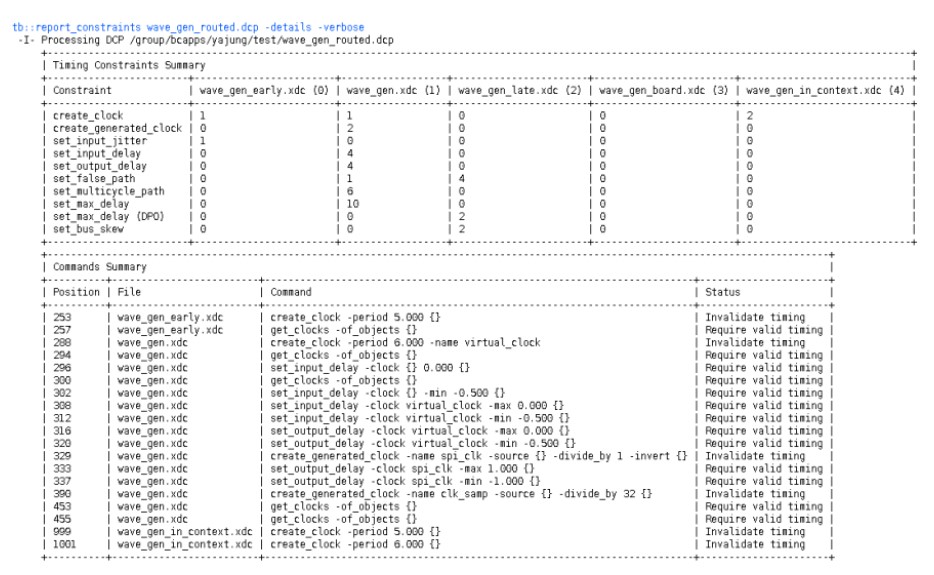

案例3:报告约束的具体信息

添加选项-details和-verbose,report_constratins可报告约束的详细信息,如下图所示。

案例4:报告时序画像

选项-timing_graph和-verbose可用于报告时序画像,如下图所示。当Status列由Invalidatetiming变为Required valid timing时,Estimatedupdates加1,这个值越小越好,根据此值可判断约束描述的顺序是否是最优的。

profiler

对Vivado编译时间进行调试时,命令profiler可帮助用户查看特定操作的运行时间,分析指定命令的调用次数,从而确定整体运行时间的瓶颈。profiler命令的具体使用方法如下所示:

profiler add *

profiler start

open_checkpoint top_routed.dcp

profiler stop

profiler summary

profiler summary -log profiler.log

profiler summary -log profiler.csv -csv

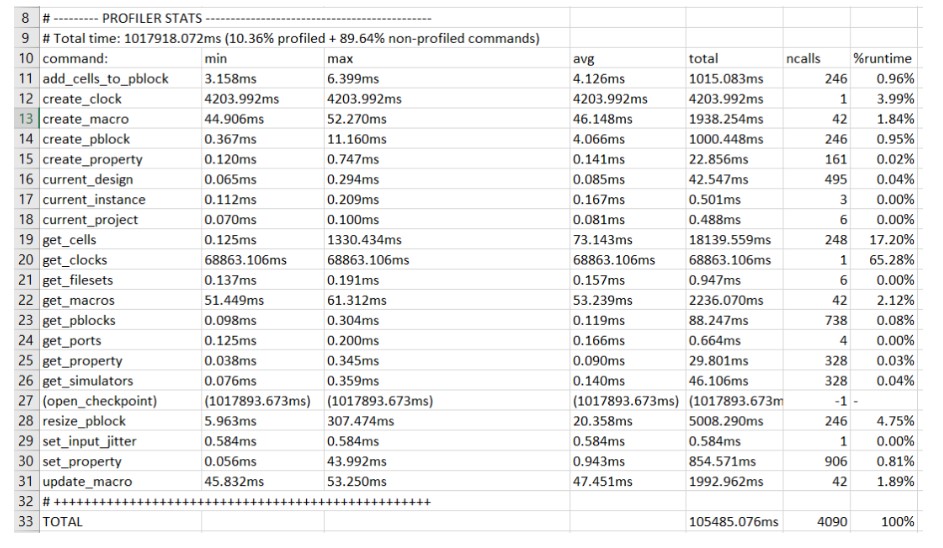

生成的csv文件可用excel打开,第一部分内容如下。第一列显示了所执行的命令,倒数第2列(ncalls)显示了该命令被调用的次数,最后一列显示了执行该命令所耗时间占整体运行时间的百分比。

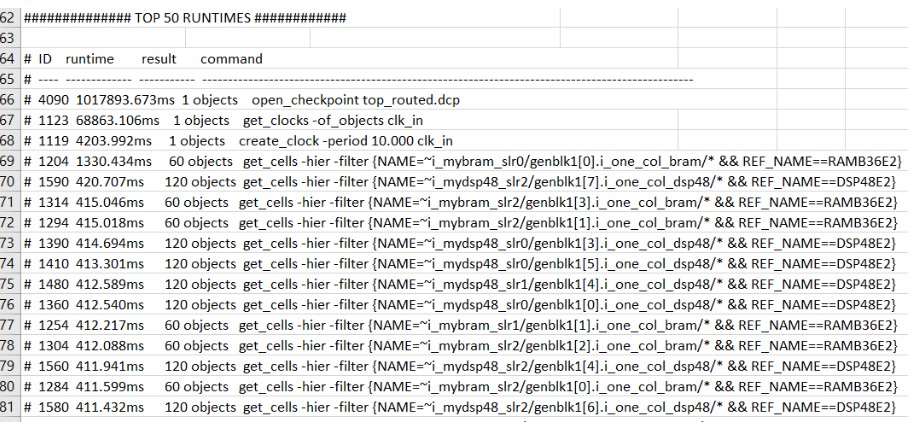

profiler生成报告还能显示前50条最耗时的命令,如下图所示。可用看到除open_checkpoint之外,get_clocks最耗时。

报告的第三部分可以看到设计中Tcl命令的使用情况,如下图所示。图中commands列(最后一列)为Tcl命令,size列为该命令返回的对象的个数,count列为返回同样个数的命令的个数,total列等于size与count的乘积。以第122行get_cells为例,返回120个对象的get_cells有24个,所以总对象个数为120x24即2880。

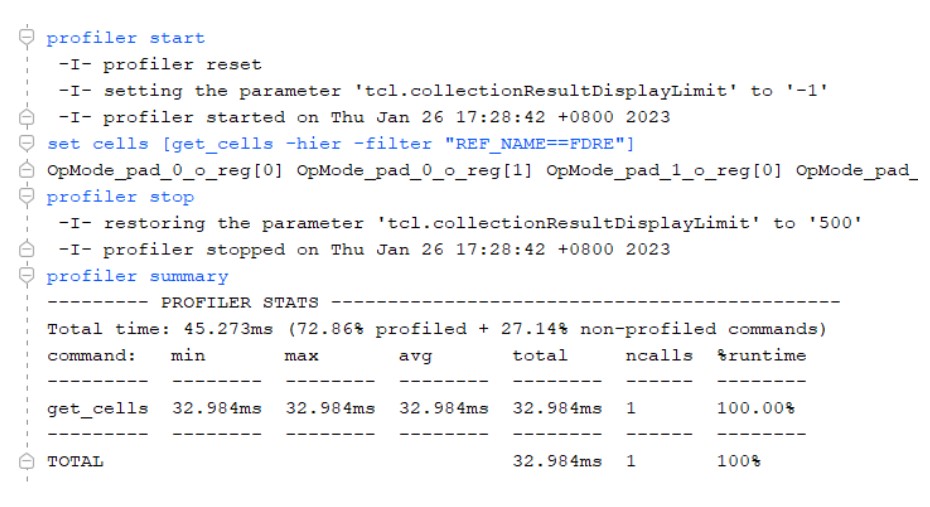

profiler命令还可用于查看指定命令的运行时间,这对于发现约束中哪些命令最为耗时很有帮助,使用方法如下所示。从生成报告中可以看到get_cells命令共耗时32.984ms。

profiler start

set cells [get_cells

-hier -filter"REF_NAME==FDRE"]

profiler stop

profiler summary

vivadoRuntime

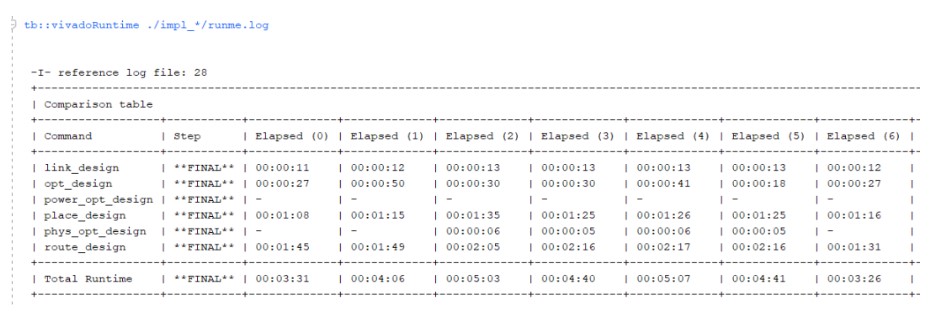

命令vivadoRuntime可用于查看不同策略下每个阶段所消耗的时间,使用方法如下图所示。每个Elapsed列对应1个策略(也就是1个DesignRun)。

使用上述3个命令我们可用快速侦测出约束中耗时的命令以及implementation阶段耗时的子步骤。

审核编辑:刘清

-

DCP

+关注

关注

0文章

30浏览量

17248 -

Vivado

+关注

关注

19文章

812浏览量

66607 -

csv

+关注

关注

0文章

39浏览量

5831

原文标题:缩短Vivado编译时间(4):时间都去哪儿了

文章出处:【微信号:Lauren_FPGA,微信公众号:FPGA技术驿站】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

三个对分析编译时间非常有效的Tcl脚本

三个对分析编译时间非常有效的Tcl脚本

评论