点击蓝字关注我们

本设计指南分为三部分,将讲解如何为电力电子应用中的功率开关器件选用合适的隔离栅极驱动器,并介绍实战经验。上两期分别讲解了隔离式栅极驱动器的介绍与选型指南以及使用安森美(onsemi)隔离式栅极驱动器的电源、滤波设计与死区时间控制(详情可点击查看),本文为第三部分,将为大家带来设计中的要点和PCB布局指南。

对于所使用的驱动器,要设计一个高能效且快速的电路,启动时间是一个重要因素。因此,启动时间必须要短。但是,启动时间受上电延迟的限制,上电延迟是指驱动器使能到首次栅极输出的时间。同许多电路一样,所用驱动器的最小上电延迟可以在数据表中找到,它用 tVPOR to OUT 来表示。

例如,安森美的隔离式栅极驱动器的 VCC 上电延迟时间典型值为 18μs。建议在驱动输入信号之前留一些裕量,以确保驱动器 VCC 偏置电源完全激活。特别是对于 NCP51561 和 NCP51563,建议 VCC 上电延迟时间留有适当的裕量。

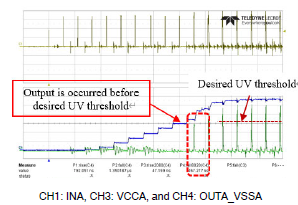

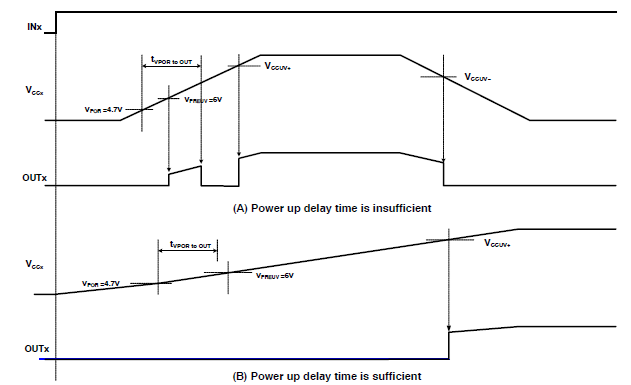

例如,在任何 VCC POR 之后的初始启动期间,VCC 上电时间至少需要 30μs 或以上,如图 23 (B)所示。如果 VCCX 上电斜坡使得 VCCX 上升时间小于 tVPOR to OUT,并且 INx 引脚上有 PWM 信号,那么在 VCC 达到实际 UVLO 阈值之前,只要 VCCX 电源电压超过预设 UVLO 阈值(例如 VCC=6 V),输出就会开始切换,然后停止,直至达到 UVLO 电平,实验结果如图 1 所示。

图1. VCC 上电时间小于 tVPOR to OUT 时的波形

图2. VCC 上电延迟时间

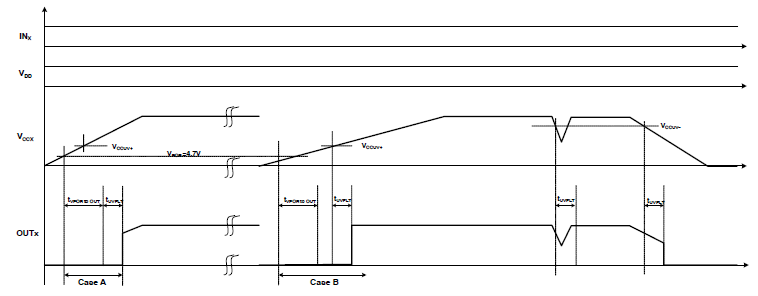

NCP51560 提供了修改 VCC 上电延迟时间的控制方法来解决图 24 中显示的问题。在栅极驱动器准备好提供适当的输出状态之前,从 VCC 上电复位 (POR) 阈值到输出有一个上电延迟时间,表示为 tVPOR to OUT(例如典型值 18μs)。

图3. VCC 上电延迟时间新概念

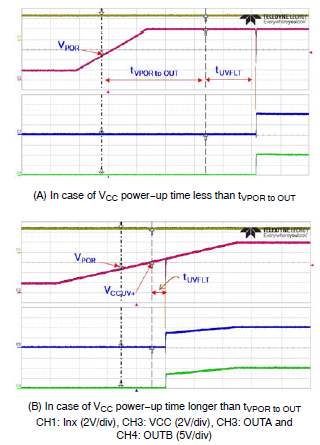

在 VCC 初始启动时,如果 VCC 上电时间小于 tVPOR to OUT,那么在上电延迟时间之后,输出就会开启,如图 4 所示。

但是,在 VCC 初始启动时,如果 VCC 上电时间大于 tVPOR to OUT,那么当 VCC 电源电压大于 UVLO 正阈值电压时,输出开启,如图 4 所示。

图4. VCC 上电时间波形

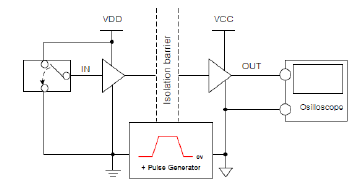

图 5 显示了 CMTI 测试配置的简化示意图。

图5. CMTI 测试简化设置

CMTI 水平是能够保持正确输出的最大可持续共模电压摆率。CMTI 适用于上升和下降共模电压边沿。CMTI 通过 GND 与 VSSA 和 VSSB 之间连接的瞬变发生器来测试。

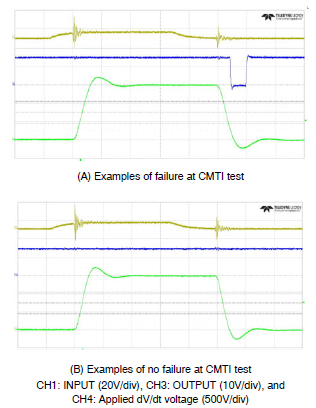

例如,有些隔离式栅极驱动器的共模瞬变抗扰度很差。图 6(a) 显示了一个测试结果,输出状态在下降 dV/dt 斜坡中从高电平变为低电平。

然而,安森美的大多数隔离式栅极驱动器具有高达 200 kV/μs 的共模瞬变抗扰度,如图 6(b) 所示。

图6. CMTI测试波形

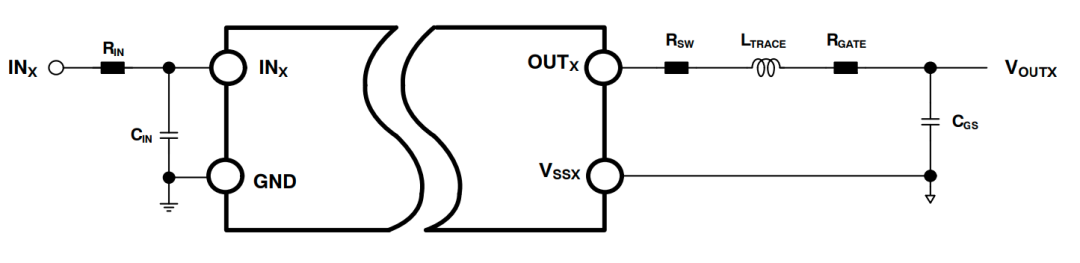

隔离式栅极驱动器输出信号取决于输出负载(通常是N沟道MOSFET)的特性。驱动器输出对于N沟道MOSFET负载的响应可以模拟为开关输出电阻 (RSW)、印刷电路板走线的电感 (LTRACE)、串联栅极电阻 (RGATE) 和栅源电容 (CGS),如图 7 所示。

图7. MOSFET栅极驱动的RLC模型

RSW 为内部隔离式栅极驱动器输出的开关电阻,约为 1.4 Ω。RGATE 为 MOSFET 的固有栅极电阻加任何外部串联电阻。

LTRACE 为印刷电路板走线的电感,其典型值为 5nH,或者若采用精心布局,从隔离式栅极驱动器输出端到MOSFET栅极具有短而宽的连接时,这个值会更小。

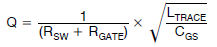

以下公式定义了 RLC 电路的质量因数Q,其表示栅极驱动器输出端如何响应阶跃变化。对于高阻尼输出而言,Q小于1。添加串联栅极电阻会抑制输出响应。

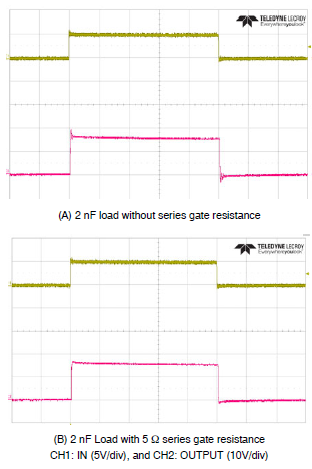

图 8 (A) 中的隔离式栅极驱动器输出波形显示输出有少量振铃,测试条件为:CGS为 2nF,RSW为 1.4Ω,RGATE 为 0,使用 15V 输出电源。通过添加串联栅极电阻可以减少输出振铃,从而抑制响应。

例如,建议添加一个大约 2Ω 至 5Ω 的串联栅极电阻,使用 2nFCGS 和 5Ω 串联电阻时的输出波形如图 8 (B) 所示。

图8. 2nF负载电容的输出波形

估算栅极驱动器功率损耗

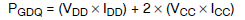

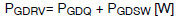

隔离式栅极驱动器给定通道的电源电流是电源电压、开关频率和输出负载的函数。通常,栅极驱动总功率损耗 PGDRV 包括静态功率损耗 PGDQ 和动态功率损耗 PGDSW。

自举二极管损耗未包含在总损耗 PGDRV 中,本部分不予讨论。第一个分量是静态功率损耗 PGDQ,当以开关频率工作时,它包括驱动器上的静态功率损耗和驱动器本身的功耗。

PGDQ 是在给定的 VDD、VCCA/VCCB、开关频率和环境温度下于试验台上测得,OUTA 和 OUTB 不连接负载。

其中:IDD 和 ICC 是在电源电压(VDD 和 VCC)和目标开关频率下测得的电流。

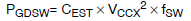

第二个分量是在有负载电容情况下的动态运行损耗 PGDSW,驱动器在每个开关周期中为负载充电和放电。

例如,MOSFET 的栅极可以近似仿真为容性负载。

由于米勒电容 CGD 及其他非线性因素影响,对所驱动负载的近似保守估计通常是将给定 MOSFET 的标称输入电容 CISS 乘以 5 倍。

其中:CEST = Ciss×5。fSW为开关频率。

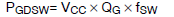

另外,使用栅极电荷可获得更精确的 PGDSW 值。

其中:QG为开关器件的总栅极电荷,fSW为开关频率。

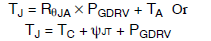

因此,可以计算栅极驱动总功率损耗 PGDRV:

本例中,VDD=5V,VCC=25V,QG=50nC。当 INA 和 INB 从 0V 切换到 5V 且开关频率为 250 kHz 时,每个电源上测得的电流为:IDD = 6.5 mA,ICCA = ICCB = 2.7 mA。

因此,总功率损耗 PGDRV 可以计算如下:

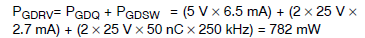

隔离式栅极驱动器输出级的损耗 PGDO 是 PGDSW 的一部分。如果栅极驱动器外部电阻为 0,并且所有栅极驱动器损耗都消耗在隔离式栅极驱动器内部,那么 PGDO 等于 PGDSW。

如果存在外部导通和关断电阻,则栅极驱动器开关的内部导通电阻和外部栅极电阻(RON 和 ROFF)共同产生此功耗。利用内部栅极电阻与总串联电阻的比值,可以计算隔离式栅极驱动芯片内每个通道的损耗。

因此,栅极驱动器的总功耗 PGDRV 为:

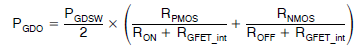

估算结温

芯片内部的功耗乘以RθJA,便可估算隔离式栅极驱动器结温比室温高出多少度:

其中:RθJA 为结至空气热阻,可从数据表中的热信息表获得。

TC为隔离式栅极驱动IC的外壳顶部温度,使用热电偶或其他仪器测量。

ΨJT为结至顶部特性参数,可从数据表中的热信息表获得。

为使器件不超出额定温度范围,TJ不得超过125℃。

隔离式栅极驱动器的逻辑接口不需要外部接口电路。

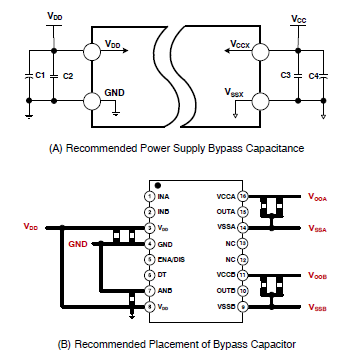

输入和输出电源引脚需要电源旁路电容,如图 9 所示。

尤其是输出电源引脚上的旁路电容必须避免使用过孔,或者必须使用多个过孔来降低旁路电感值。VDD 和 VCCA(或 VCCB)的电源旁路电容需要布置在尽可能靠近电源引脚的地方。

图9. 推荐的电源旁路电容布局

为了改善设计的开关特性和效率,开始 PCB 布局之前应考虑以下事项。

元件放置

输入/输出走线应尽可能短。

最大限度地降低寄生电感和电容对布局的影响。(为保持较低的信号路径电感,应避免使用过孔。)

VDD 和 VCCA(或 VCCB)的电源旁路电容以及栅极电阻需要布置在尽可能靠近栅极驱动器的地方。

栅极驱动器应尽可能靠近开关器件,以降低走线电感并避免输出振铃。

接地考量

在高速信号层下方应有一个实心接地平面。

VSSA 和 VSSB 引脚旁边应有一个实心接地平面,并为 VSSA 和 VSSB 使用多个过孔,以降低寄生电感并使输出信号上的振铃最小。

高压 (VISO) 考量

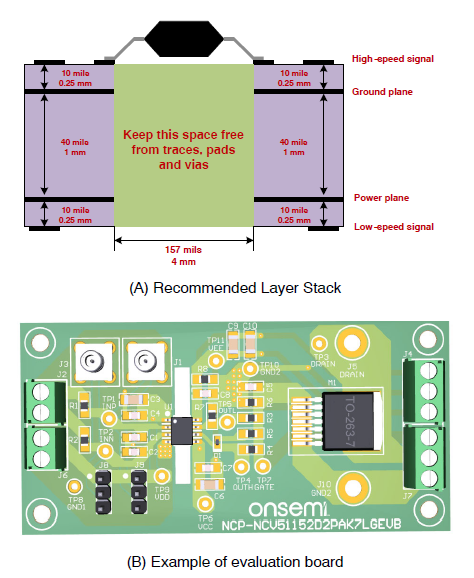

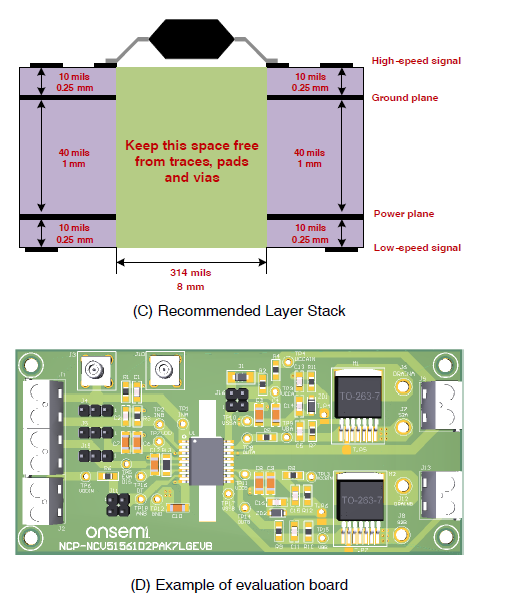

为确保初级侧和次级侧之间的隔离性能良好,对于窄体封装和宽体封装,驱动器件下方不应布置任何 PCB 走线或铜,如图 10 和图 11 所示。建议提供 PCB 切口以防止污染,避免损害隔离式栅极驱动器的隔离性能。

图10.推荐的窄体封装PCB布局

图11. 推荐的宽体封装PCB布局

本文为本设计指南的最后一部分

想了解完整内容

扫描下方二维码填写信息

获取英文原版完整应用笔记

点个星标,茫茫人海也能一眼看到我

原文标题:使用隔离式栅极驱动器的设计指南(三):设计要点和PCB布局指南

文章出处:【微信公众号:安森美】欢迎添加关注!文章转载请注明出处。

-

安森美

+关注

关注

32文章

1713浏览量

92212

原文标题:使用隔离式栅极驱动器的设计指南(三):设计要点和PCB布局指南

文章出处:【微信号:onsemi-china,微信公众号:安森美】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

采用 LLC 拓扑结构设计隔离式栅极驱动器电源,低成本 LLC 转换器的设计指南

TPSI3052Q1EVM具有集成15V栅极电源的汽车类增强型隔离式开关驱动器EVM用户指南

电隔离栅极驱动器的隔离能力评估

电隔离栅极驱动器选型指南

使用隔离式 IGBT 和 SiC 栅极驱动器的 HEV/EV 牵引逆变器设计指南

级联两个TPSI3050隔离式开关驱动器,以增加栅极驱动电压

PMP30629.1-具有集成开关PSR反激式转换器的隔离式2.5W SiC和IGBT栅极驱动器 PCB layout 设计

TIDA-020030-具有热敏二极管和感应 FET 的 SiC/IGBT 隔离式栅极驱动器 PCB layout 设计

使用隔离式栅极驱动器的设计指南(三):设计要点和PCB布局指南

使用隔离式栅极驱动器的设计指南(三):设计要点和PCB布局指南

评论