数字门级电路可分为两大类:组合逻辑和时序逻辑。锁存器是组合逻辑和时序逻辑的一个交叉点,在后面会作为单独的主题处理。

组合逻辑描述了门级电路,其中逻辑块的输出直接反映到该块的输入值的组合,例如,双输入AND门的输出是两个输入的逻辑与。如果输入值发生变化,输出值将反映这一变化,组合逻辑的RTL模型需要反映这种门级行为,这意味着逻辑块的输出必须始终反映该逻辑块当前输入值的组合。

SystemVerilog有三种在可综合RTL级别表示组合逻辑的方法:连续赋值语句、always程序块和函数。接下来几篇文章将探讨每种编码风格,并推荐最佳实践编码风格。

时序逻辑的时钟到Q传播和建立/保持时间

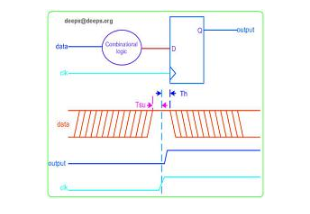

在ASIC和FPGA的实现层面,时钟时序逻辑具有不同于组合逻辑的特点。其中一个特点是,从时钟输入触发到触发器输出变化的传播延迟。这通常被称为时钟到Q的延迟。第二个特性是建立和保持时间。建立时间是在时钟触发前数据输入必须稳定的时间段。

保持时间是时钟触发后数据必须保持稳定的时间段。如果数据在建立和保持时间内发生变化,作为新的触发器状态存储的值将是不确定的。在这些条件下,一个触发器的状态也有可能在数值之间振荡一段时间,然后再稳定到一个稳定的数值。这种不稳定的时期被称为偏移性(metastability)。

RTL模型应该是零延迟模型--这是最佳协同结果质量(QoR)的要求--这意味着RTL模型不存在传播延迟。触发器的输出在仿真时间的同一时刻发生变化,没有门级时钟到Q的传播延迟。作为零延迟模型,抽象的RTL触发器也没有建立和保持时间,也不会发生变异。然而,时钟到Q的传播行为必须用抽象的RTL模型来表示,而且RTL模型需要反映适当的设计技术,以避免在ASIC或FPGA中实现后出现偏移性的情况。

时序逻辑的时钟到Q的传播延迟。在ASIC和FPGA的实现层面上,时钟序列器件有一个时钟到Q的传播延迟。触发器的状态或内部存储在时钟的一个边沿上被更新。过渡到一个新的状态并不是瞬间发生的。内部状态的改变需要少量的时间。在这个过渡时间内,翻转器的前一个状态可以在翻转器的输出上使用。当多个触发器串联在一起时,这种通过每个触发器的时钟到Q的传播延迟在一系列触发器中产生级联效应。移位寄存器和计数器就利用了这种级联效应。

图8-1中的电路表示一个4位的约翰逊(Johnson)计数器,它是一个移位寄存器,最后一个触发器的输出被反相并反馈到第一个触发器的输入。

图8-1:4位约翰逊(Johnson)计数器示意图

复位后,这个4位约翰逊(Johnson)计数器的输出示例是:

cnt[0:3]-0000 cnt[0:3]-1000 cnt[0:3]-1100 cnt[0:3]-1110 cnt[0:3]-1111 cnt[0:3]-0111 cnt[0:3]-0011 cnt[0:3]-0001 cnt[0:3]-0000

从一个触发器到下一个触发器的级联效应在这个输出中很明显。上一个触发器DFF4的O输出被反转,在第一个触发器的D输入端oFF1上变成1。在第一个时钟周期,这个1被存储到DFF1中,而DFFl的旧状态,一个0,被级联到DFF2。在第二个时钟周期,DFFl输出的1被级联到DFF2中。

在第三个时钟周期,DFF2的1级联到DFF3,而在第四个时钟周期,DFF3的1级联到DFF4。在第四个时钟周期后,DFF4的输出变为1,DFFl的D输入变为0。下一个时钟周期,0加载到DF Fl中,并且0在随后的每个时钟周期中级联通过四个触发器。

约翰逊(Johnson)计数器的设计取决于每个触发器的时钟到Q的传播延迟,它允许系列中每个触发器的前一个状态成为系列触发器中每个后续阶段的稳定D输入。即使RTL代码用零延迟建模,RTL模型也要保持这种时钟到Q的传播延迟行为,这一点至关重要。触发器行为的这一重要特征是由非阻塞赋值符号(<=)表示的。

审核编辑:刘清

-

FPGA

+关注

关注

1629文章

21729浏览量

602986 -

asic

+关注

关注

34文章

1199浏览量

120434 -

RTL

+关注

关注

1文章

385浏览量

59761 -

Verilog语言

+关注

关注

0文章

113浏览量

8224 -

门级电路

+关注

关注

0文章

15浏览量

1957

原文标题:SystemVerilog-时序逻辑建模(3)建立/保持时间

文章出处:【微信号:Open_FPGA,微信公众号:OpenFPGA】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

FPGA的时钟设计:如何建立时间与保持时间

芯片设计进阶之路—从CMOS到建立时间和保持时间

建立时间和保持时间讨论

FPGA实战演练逻辑篇51:建立时间和保持时间

FPGA实战演练逻辑篇57:VGA驱动接口时序设计之4建立和保持时间分析

VGA驱动接口时序设计数据的建立时间和保持时间

时序约束是如何影响数字系统的,具体如何做时序分析?

为什么触发器要满足建立时间和保持时间

建立时间和保持时间(setup time 和 hold time)

FPGA时序约束的建立和保持时间方法

PCB传输线建立时间、保持时间、建立时间裕量和保持时间裕量

时序逻辑的时钟到Q传播和建立/保持时间

时序逻辑的时钟到Q传播和建立/保持时间

评论