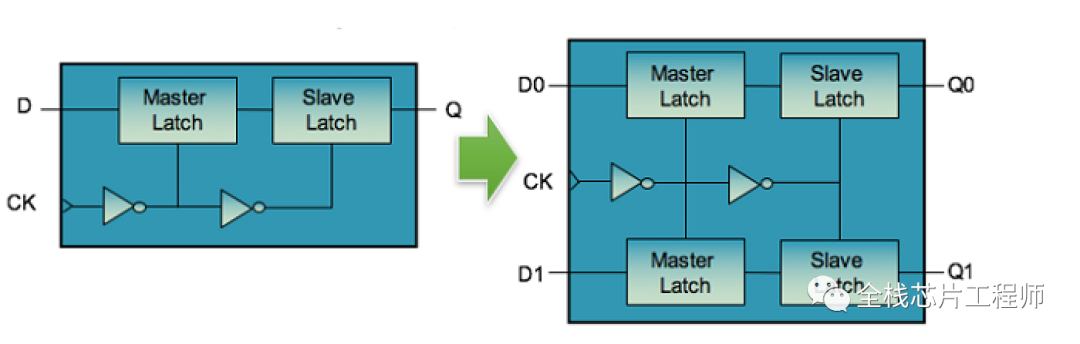

所谓multi-bit cell,可以理解成把多个完全相同的cell合并在一个cell里,如下图所示,集成2bit的multi-bit cell的clock inverter是共享的,那么可以节省2个clock inverter的面积、功耗。

同时由于flip-flop数量减少,时钟互联线也减少,即减少了clock net length、capacitance、clock inverter更利于总功耗的降低。

有一点非常重要,MBFF对SBFF的合并使用目的是降低功耗,但是前提是保证timing,若timing不满足,MBFF是应该被要求拆分成SBFF,SBFF更方便resize、move等操作。

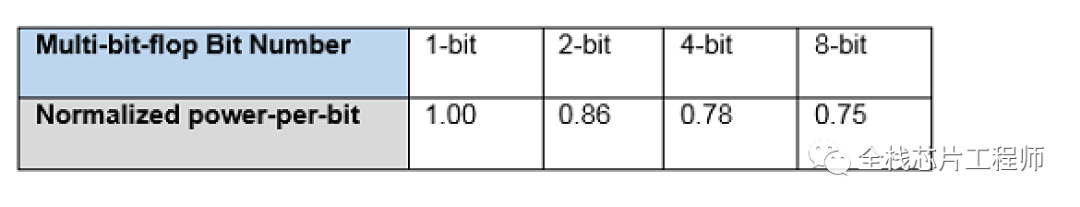

芯片功耗很大一部分在时钟树上,通过multi-bit cell技术我们可以获得如下图所示的功耗改观:

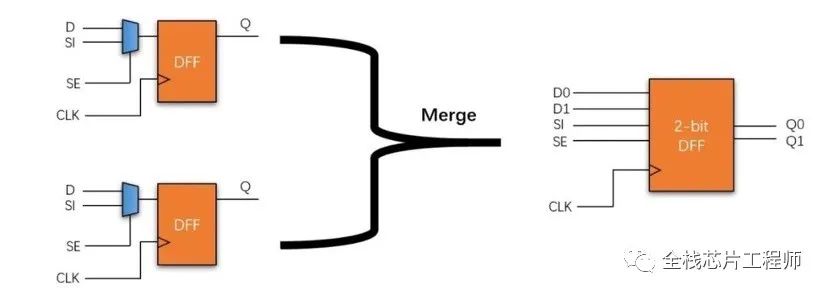

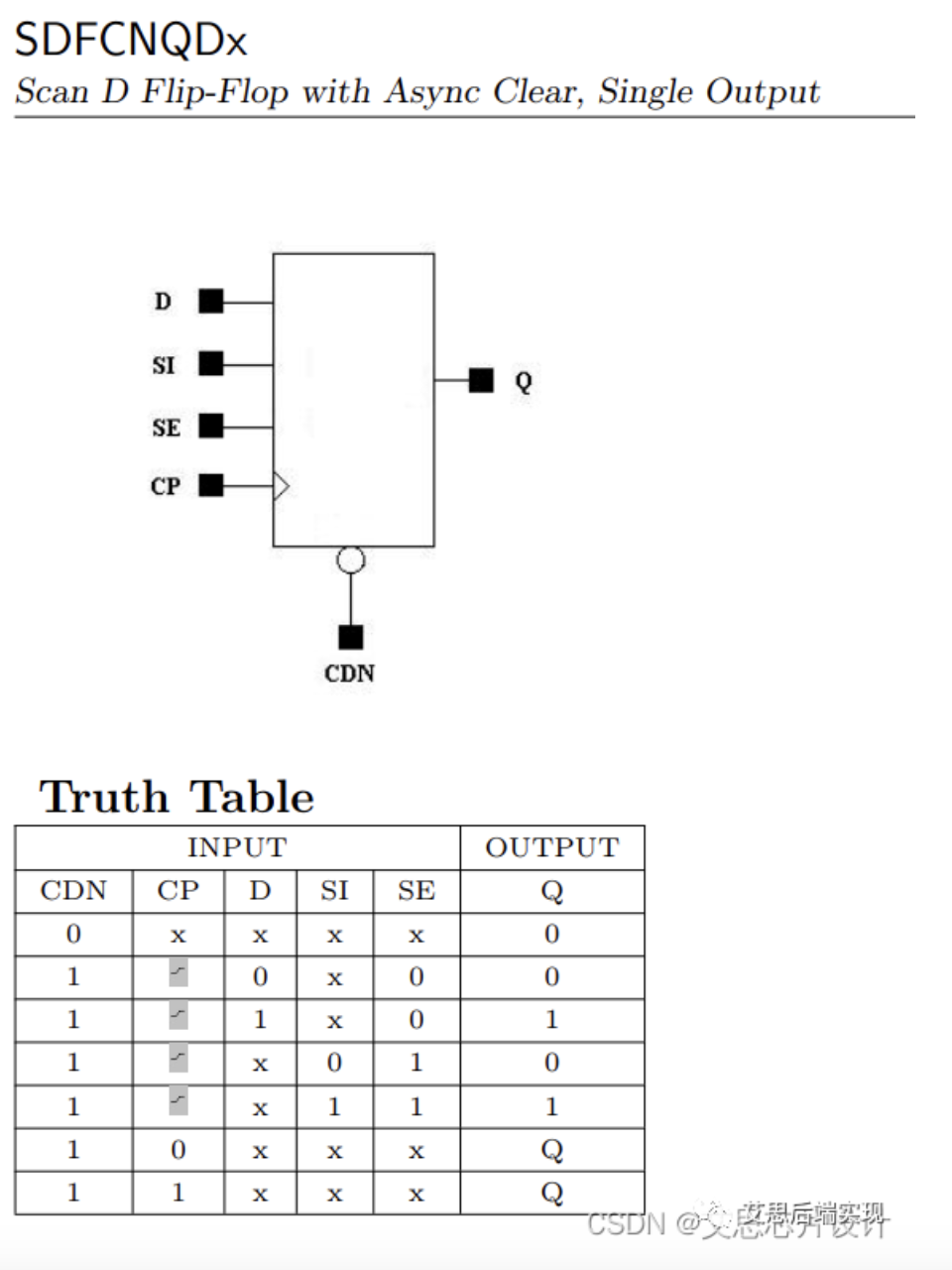

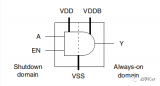

此外,通常scan DFF由于带了scan mux电路,其面积会更大,而Multi-bit flip-flop (MBFF)合并单bit寄存器后,可以更明显降低面积,以scan DFF为例,single bit 和multi bit的逻辑关系一般如下:

在晶体管级别的版图设计过程中,会采用优化晶体管连接,晶体管共用等手段来节约面积,因此multi-bit cell比同等bit数目的single-bit cell的版图面积总和要小一些。假设一个1-bit DFF的面积为 ,那么一个2-bit DFF的面积一般会比

小一些,4-bit DFF的面积会比

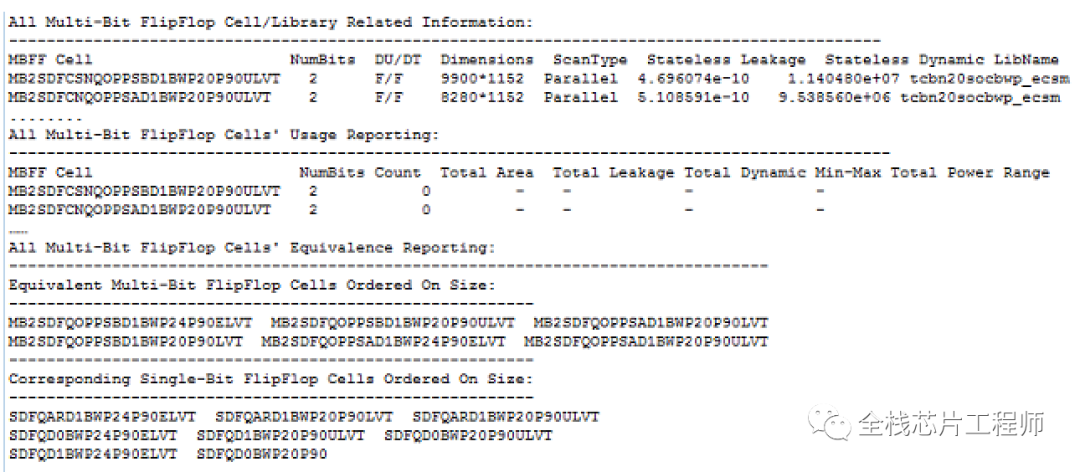

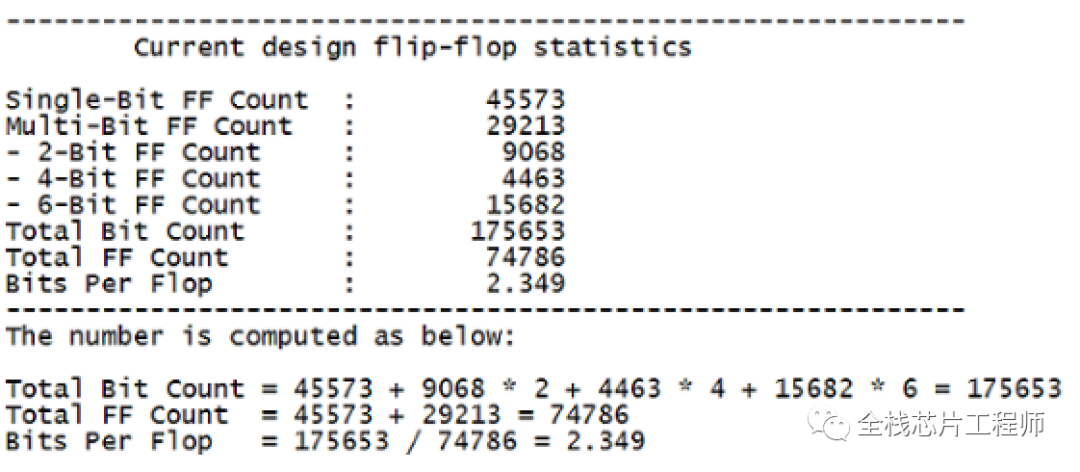

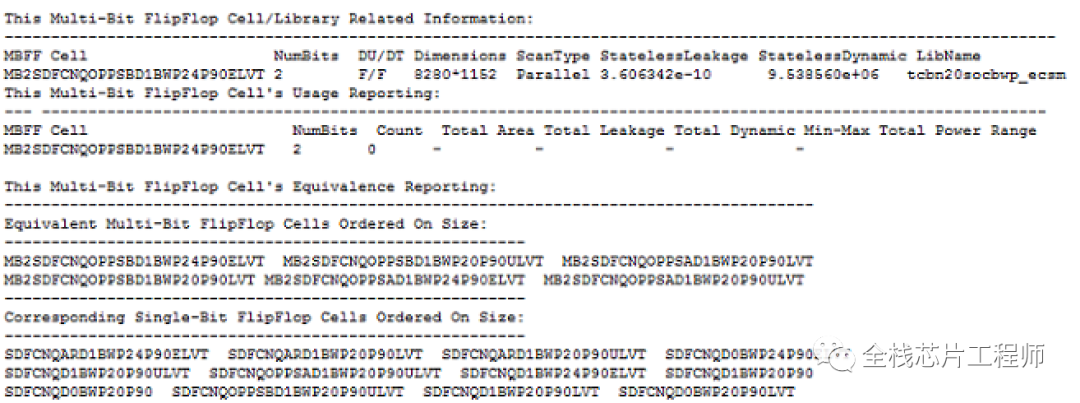

小更多。 在Cadence INNOVUS中可以用如下命令查看MBFF信息:

reportMultiBitFFs -all

reportMultiBitFFs -statistics

reportMultiBitFFs -cell MB2SDFCNQOPPSBD1BWP24P90ELVT

MBFF结构在功耗上带来的好处主要体现在以下几个方面,整体而言,就是减少了clock net length、capacitance、clock inverter。

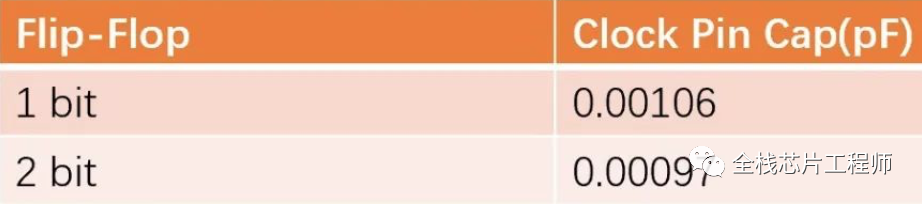

1)clock pin capacitance减少从而降低clock switching power

由下图可知,虽然2bit MBFF较1bit flip-flop的clock pin cap改观不大,但当design中有大量multi-bit DFF来替代single-bit DFF时,DFF数量大量降低,芯片时钟树上整体pin cap的下降是非常明显的。cap越小switching power也越小,动态功耗降低。

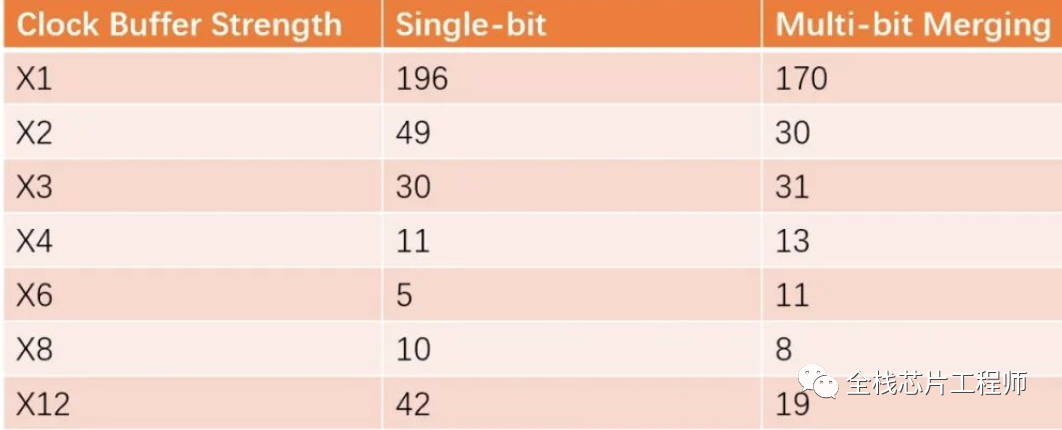

2)时钟树buffer数量减少,降低switching和leakage power

由于multi-bit DFF中每个DFF的clock pin cap相对于single-bit DFF有一些减小,那么在multi-bit design中一个相同的buffer可以驱动更多的MDFF,当然最主要还是DFF数量的减少,从而显著减少时钟树上的buffer数量和面积,进一步降低时钟树上的功耗。

3)时钟树绕线资源减少,时钟树寄生RC从而降低dynamic power

MBFF大量使用时,相对于single-bit design来说,芯片standard cell数量大幅下降,而且在很多时候DFF的摆放也可能会更加集中,时钟树绕线将节省大量走线资源,进而减少整个时钟网络的寄生RC。

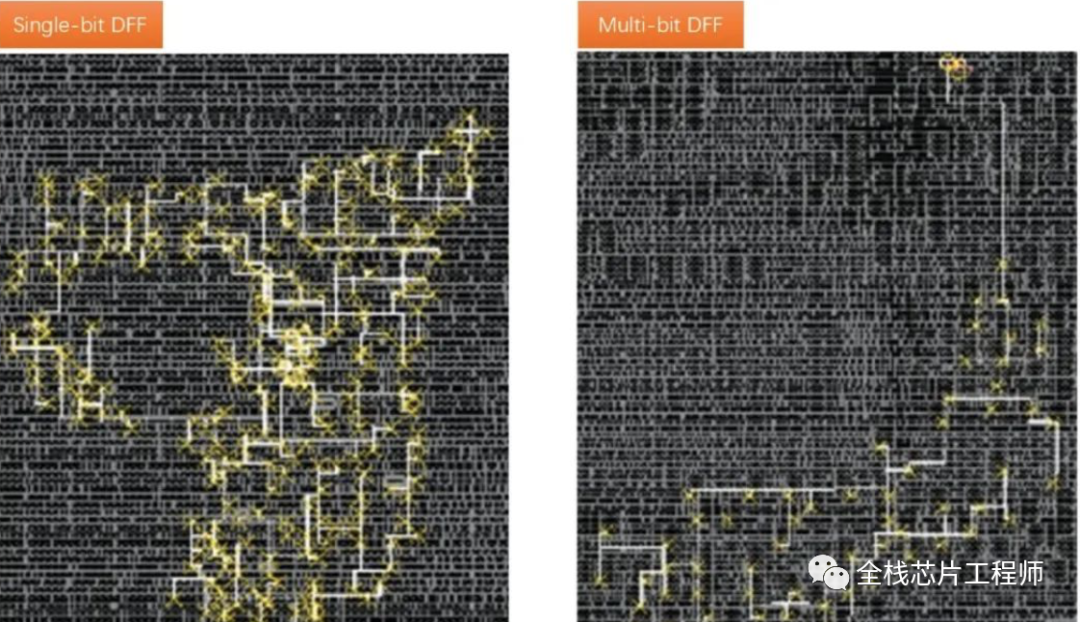

下图展示了single-bit DFF与multi-bit DFF的绕线差异,可以看出右侧的MBFF绕线明显更少,时钟整体的寄生RC得到减少,从而降低功耗。

尽管multi-bit有以上诸多优点,但是在实际应用中并不总能得到最好的结果。

其主要原因在于以下几个方面:

a) single-bit到multi-bit的转化有诸多条件限制,很多时候design实际的multi-bit cell比率不高。

b) multi-bit cell摆放不合理可能会引起congestion问题、timing问题,反而会增加更多的组合逻辑的power从而抵消clock tree上带来的功耗降低的效果。

比如,2bitsingle-bitDFF本来被place在不同位置,若合同为2bit的multi-bit DFF后,routing连线可能反而更长,增加了路径延迟,工具会采用buffering、sizing的优化方式优化时序,若依然不能满足timing,那么multi-bit cell不如拆分成single-bit cell,因为single-bit cell可以更方便resize、move。

c) IR/EM方面的考虑可能会故意让multi-bit cell互相摆放的远一些,从而无法达到减少clock net length寄生RC从而降低功耗的效果。

审核编辑:刘清

-

寄存器

+关注

关注

31文章

5334浏览量

120208 -

晶体管

+关注

关注

77文章

9678浏览量

138049 -

时钟树

+关注

关注

0文章

54浏览量

10741 -

dff

+关注

关注

0文章

26浏览量

3416

原文标题:低功耗设计之Multi-Bit Cell

文章出处:【微信号:ExASIC,微信公众号:ExASIC】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

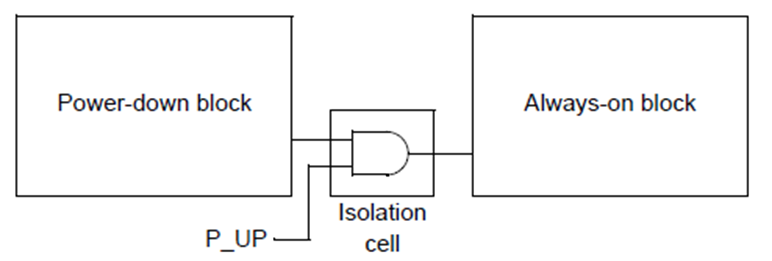

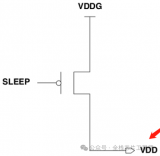

低功耗isolation cell设计

什么是Isolation Cell?低功耗设计基础—Isolation Cell

STM32CubeMX低功耗模式简介

STM32CubeMX低功耗模式简介

STM32之待机唤醒低功耗模式简介

ZXSC300-SINGLE OR MULTI CELL L

电子知识大全之树电运行低功耗电路简介

Multi-bit Flip Flop(MBFF)修复技巧

芯片设计里的Multi-Bit FF探究

isolation cell的低功耗设计

低功耗设计之multi-bit cell技术简介

低功耗设计之multi-bit cell技术简介

评论