关于摩尔定律在今天的有效性,有很多健康的争论。但不可否认的是,长期以来指导半导体行业的芯片性能每两年翻一番的可预测性正在放缓。最终,在物理上根本不可能开发出具有更小(和更多)晶体管的芯片。然而,工程独创性依然存在,芯片设计人员继续寻找方法,将信封推向更好的性能、功耗和面积(PPA)。

优化处理器架构以应对不断变化的工作负载是寻求从摩尔定律中提取更多内容的结果之一。由于仅仅通过移动到更小的几何尺寸和提高时钟频率来产生更高的性能变得徒劳无功,设计工程师正在考虑不同的SoC架构,以更有效地针对其苛刻且不断变化的工作负载进行定制。算法也变得更加创新,以满足人工智能(AI)和传感器融合等应用的需求;这也会影响 SoC 架构决策。在这篇博文中,我们将探讨不断变化的处理工作负载和日益创新的算法如何推动对新处理器 IP 的需求,以及嵌入式 SoC 设计人员如何在保持其面积和功耗预算的同时满足对更高性能的永无止境的需求。

性能需求推动新的处理器架构

固态硬盘 (SSD) 闪存、传感器融合、AI 和 5G 无线等高性能嵌入式应用共同挑战,推动了处理器端架构改进的需求:

逻辑速度的增长速度快于嵌入式存储器访问时间

大多数嵌入式设计的时钟速度在 1 GHz 至 2 GHz 范围内达到顶峰

时钟速度也需要适度来管理功耗

对性能、功能和特性的需求持续增长

为了满足这些相互竞争的需求,设计工程师正在实施更多的异构处理元素,以便为不同类型的工作负载提取更高的性能。在具有异构处理器架构的 SoC 中,设计人员将这些不同的处理器类型与处理其专用应用的每个内核相结合。支持 Linux 的 CPU、实时控制器、数字信号处理器 (DSP)、GPU 和神经网络加速器是当今高级 SoC 中常见的处理器类型示例。

但是,异构方法的优点不仅限于具有大型工作负载的应用程序。智能家居自动化中心可以通过这种方式设计,以提高处理和电源效率。这些设备处理各种不同的功能:图像处理、语音识别、自然语言处理、控制功能等。像自然语言处理这样的任务需要重型处理器,这也消耗大量功率。同时,设备本身始终处于打开状态,因此在同一重型处理器上运行始终在线的任务是不切实际的。为了节省功耗,具有内置数字信号处理支持的小型低功耗控制器可以管理关键字唤醒或人脸检测等始终在线的任务。一旦设备完全启动,自然语言处理或人脸识别等计算密集型任务可以转移到更大、更强大的内核,如高性能 DSP 或 AI 加速引擎。

异构处理器方法的优势不仅限于具有大型工作负载的应用程序。

异构工作负载在手机等大容量、小尺寸设备中变得很常见,这些设备可以轻松包含 50 多个内核,每个内核专门用于一组特定的任务。如今,这些类型的工作负载正在进入更广泛的应用领域。即使是现代汽车,也正在从整个车辆的分布式控制器演变为集中式异构多核控制器。软件定义汽车的出现,以支持更高的自动化水平和复杂的车载应用,正在推动汽车行业转向异构计算模型。

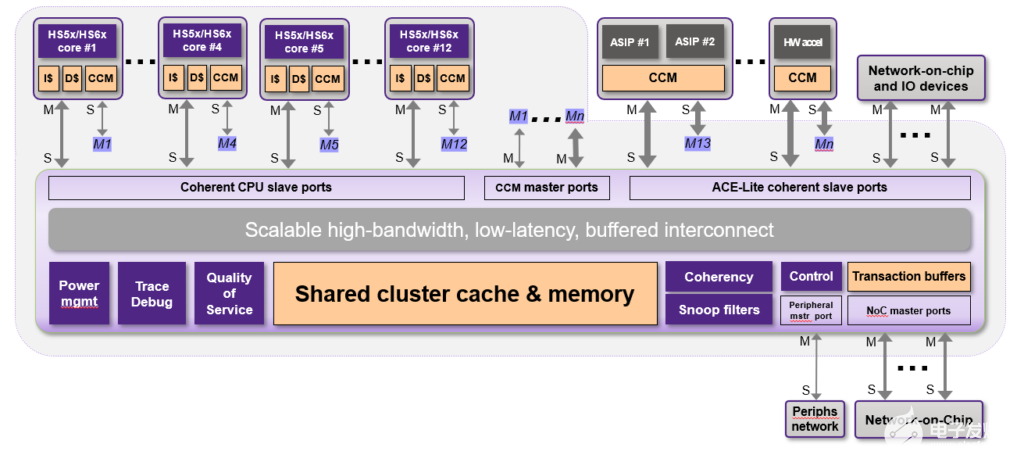

即使在同构的多核处理器实现中,设计人员也在寻找运行异构工作负载的能力。提供具有高带宽互连的大规模、一致的多核集群(大于八核)和定制处理器的能力,为异构任务提供了另一种架构选择,尤其是那些需要共享连贯数据的任务。例如,在计算存储应用程序中,核心集群的一个子集可以用作主机处理器(运行 Linux),而运行 RTOS 的另一个核心子集可以管理 SSD 存储阵列。所有这些都可以通过单个多核群集进行管理。

支持专用处理器架构需要什么?

我们现在看到的专用处理器架构为可编程性和工具带来了一系列新的挑战。毕竟,如果芯片难以编程,支持这些工作负载的复杂、多处理架构几乎没有用处。这就要求人们注意需要一组与这些类型的架构相一致的强大工具,从而简化工程师将其应用程序编程和移植到不同处理器的过程。

异构处理架构提出了一个大问题,即如何连接所有组件以最好地支持并行处理。某些内核可能放置在非常接近的位置,因此可以共享缓存等资源。因此,采用以数据为中心的体系结构视图并确定数据的位置、处理位置以及需要数据的位置非常有用。将数据保留在处理集群的本地可降低功耗和读取延迟,同时减轻片上网络的负载。为了提供灵活的内存方案来处理本地数据,可以在二级集群缓存和集群共享内存之间动态分区共享 SRAM(供可能与多核集群共享资源的其他处理元素使用)。设计人员可以决定如何在不同的处理器之间共享这些内存资源。高带宽和低延迟互连还可确保内核之间的快速数据传输。

处理器架构的另一个重要考虑因素涉及电源和时钟域。独立的电源和时钟域有助于简化物理设计,同时最大限度地降低功耗和面积。集群中的内核可以驻留在自己的电源域中,每个内核运行自己的时钟。

处理器架构师工具箱内

为了促进有效的异构处理架构,处理器架构师在工具箱中提供了多种选项。

可并行化应用程序的多核性能扩展可实现近乎线性的加速;实现这一目标的关键是低延迟处理器集群架构和足够的通信带宽

通过专用处理器或定制硬件进行硬件加速

专用指令集处理器 (ASIP) 加固件,提供处理器加软件选项的灵活性以及硬件加速器的功耗和面积效率

广泛的处理器 IP 解决方案组合

具有适当功能的处理器和工具可以帮助缓解开发定制、异构、多核架构的一些挑战。选择处理器时,评估过程应涵盖性能、功耗、可扩展性和灵活性规格。另一个重要的考虑因素是创建这些架构的生态系统:基于事实或行业标准的工具可以降低风险并提供一致性。

在我们的 DesignWare® ARC® 处理器 IP 产品组合中,Synopsys 提供功耗和面积高效的 32/64 位 CPU 和 DSP 内核、视觉处理器、子系统和软件开发工具。ARC 处理器还受到一系列第三方工具、操作系统和中间件的支持,这些工具、操作系统和中间件来自加入 ARC 访问计划的领先行业供应商。

下一代嵌入式处理器架构示例。

我们的工具包括开发工具包、编译器、调试器、模拟器、开源软件、GNU 工具和旨在简化开发和编程过程的文档。例如,使用我们的API,程序员可以编写神经网络应用程序,而不必担心工作负载如何在硬件级别进行分区或处理。API 通过一个层来处理这个问题,该层确定运行软件的最有效处理元素。另一个示例是调试环境,在该环境中,用户可以看到不同异构内核的并发视图,以实现高效、同步的调试过程。

当现成的处理器 IP 不能完全满足设计的独特工作负载要求时,或者如果需要面向未来的处理能力,团队可能会选择设计特定于应用的处理器 (ASIP),它在其应用领域内提供软件可编程性。Synopsys ASIP Designer 工具可自动设计和实施 ASIP,提供对架构选择的快速探索,生成基于 C/C++ 编译器的高效软件开发套件,可自动适应架构变化,并自动生成功耗和面积优化的可合成 RTL。

总结

摩尔定律的放缓为芯片设计人员开辟了新的创新途径,这些设计人员寻求为其目标应用提取最佳PPA。专用处理器架构已成为满足不断变化的处理器工作负载和复杂新算法需求的答案。大多数现代 SoC 都有处理要求,可以通过可配置的现成 IP 和专用专用硬件加速器的组合来优化 PPA。设计这些架构可能具有挑战

审核编辑黄宇

-

处理器

+关注

关注

68文章

19348浏览量

230255 -

芯片

+关注

关注

456文章

50950浏览量

424725 -

嵌入式

+关注

关注

5087文章

19145浏览量

306120 -

摩尔定律

+关注

关注

4文章

636浏览量

79096 -

时钟

+关注

关注

11文章

1736浏览量

131582

发布评论请先 登录

相关推荐

英特尔10nm处理器预计2017年推出 驳斥摩尔定律放缓说法

晶圆和摩尔定律有什么关系?

摩尔定律也适用于EPON芯片商用之路?

半导体行业的里程碑“摩尔定律”竟是这样来的

摩尔定律,摩尔定律是什么意思

摩尔定律的准确性_摩尔定律失效的原因_超越摩尔发展的新趋势

摩尔定律不会死去!这项技术将成为摩尔定律的拐点

为什么处理器工作负载随着摩尔定律的放缓而变化

为什么处理器工作负载随着摩尔定律的放缓而变化

评论