有时,电源上的高dV/dt上升时间会导致下游组件出现问题。在具有高电流输出驱动器的24V供电工业系统中尤其如此。本应用笔记介绍了如何控制上升时间,同时限制通过控制FET的功率损耗。

概述

电源上的高 dV/dt 上升时间会导致下游组件出现问题。在具有大电流输出驱动器的24V供电工业和汽车系统中尤其如此。该设计思想描述了如何控制上升时间,同时限制通过控制FET的功率损耗。

限制上升时间

对于许多系统而言,一个简单的pFET电路和相关元件就足以限制电源的上升时间。但是,当电流达到8A及以上时,R德森的pFET会导致系统中的热量上升。具有较低 R 的 nFET德森是一个不错的选择。

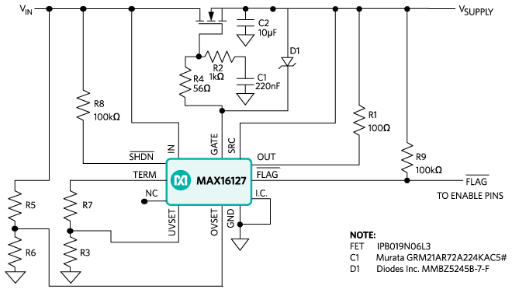

MAX16127为3mm × 3mm nFET控制器,设计用于过压保护。它还可用于控制电源电压的斜坡。该保护电路上的电源良好/FLAG输出使其能够在受控电压为输入电压的90%时使能下游器件,而与输入电压无关。与设置固定导通电压或延迟时间相比,此功能是一个很好的改进,特别是在输入电压可以在很宽范围内变化的工业和汽车系统中。

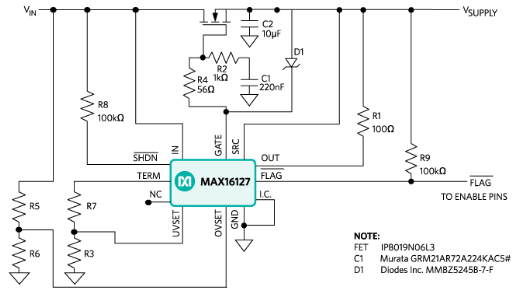

图1中的电路显示了用于斜坡V的基本配置在.MAX16127的GATE引脚为电流输出电路,来自内部电荷泵。它将 nFET 晶体管的栅极驱动至比 nFET 源极高约 10V 的电压。GATE上的附加电容可用于控制nFET栅极电压的上升时间,并且电容的值可以根据所需的压摆率进行调整。在本例C1中,显示的是220nF电容。电阻R2 (1kΩ)与C1串联。R2隔离C1,因此当MAX16127在过压或故障情况下关断时,关断时间很快。

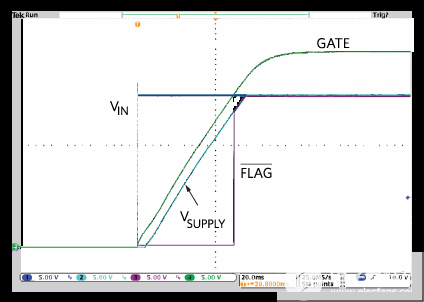

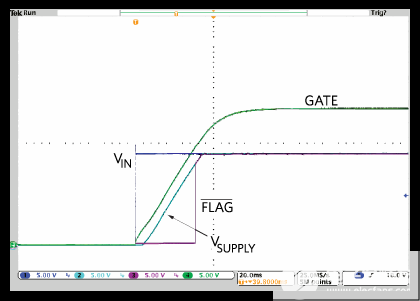

当栅极斜坡时,nFET将处于其线性区域。因此,如果所有下游电路在斜坡上升时开始工作,则可以看到大量的功耗。MAX16127的/FLAG引脚用作下游驱动器和电源的使能引脚。图2和图3显示了/FLAG使能信号如何及时移出V。在更改,始终启用当 V供应处于 V 的 90%在.使用/FLAG作为使能时,您只需担心在一切正常时调整最后10%的nFET大小。

MAX16127的GATE引脚标称电流为180μA,使用公式计算栅极驱动上升时间:I = C dV/dT。使用所示的220nF电容可获得约0.82V/ms的dV/dT。图 2 显示 V供应在大约30ms内斜坡上升至40V,这接近我们的预期,因为栅极驱动呈线性斜坡上升。

该电路还使用电阻R5和R6提供标准过压保护,并使用电阻R3和R7提供欠压锁定。

图1.上升时间控制电路原理图

图2.30V V 的波形和/FLAG行为在.

图3.18V V 的波形和/FLAG行为在.

确定场效应管的尺寸

在本例中,我们使用 90% /FLAG 来实现 10A 的下游负载。假设VIN上的最大电压为30V,我们需要调整FET的大小,使其能够在大约4ms内处理VSUPPLY从27V斜坡上升到30V时的平均功率。平均功率为 I × 1/2 (VIN - VOUT) 或 1.5V × 10A = 15W,但持续时间很短。大多数功率FET数据手册都有一个安全工作区(SOA)图,该图显示VDS与电流的关系以及时间叠加。检查 SOA 以调整 FET 的大小。

审核编辑:郭婷

-

电源

+关注

关注

185文章

18083浏览量

253702 -

驱动器

+关注

关注

54文章

8440浏览量

148146 -

控制器

+关注

关注

113文章

16739浏览量

181019

发布评论请先 登录

相关推荐

限制稳压器启动时dV/dt和电容的电路

高电压和高dv/dt中的电压传感器抗噪性

Analysis of dv/dt Induced Spur

Analysis of dv_dt Induced Spur

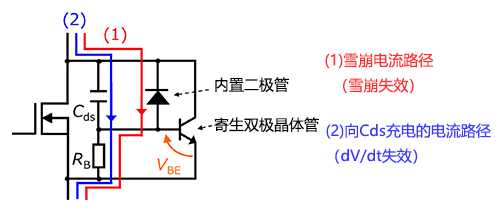

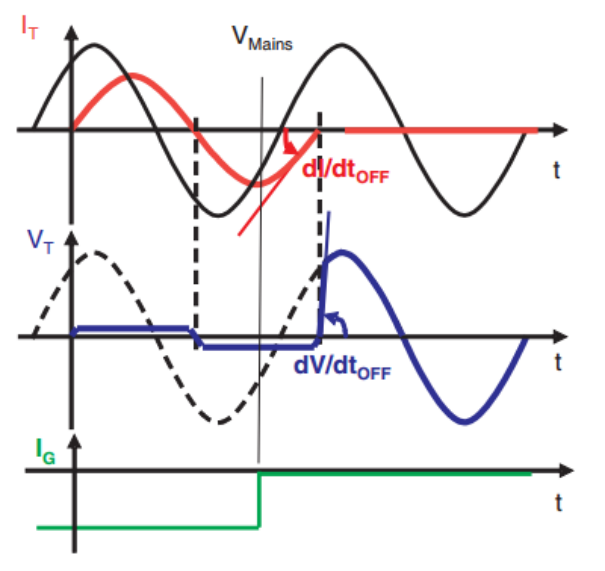

电压源型驱动dv/dt的表现

混合动力系统驱动器内dV/dt噪声的来源及解决方案

如何控制电源dV/dt上升时间同时限制通过控制FET的功率损耗

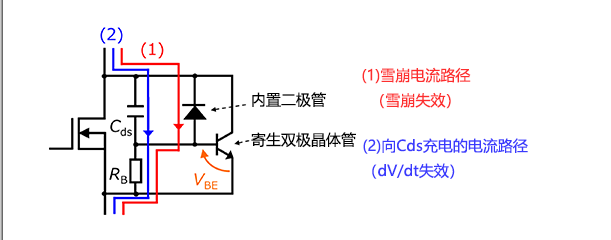

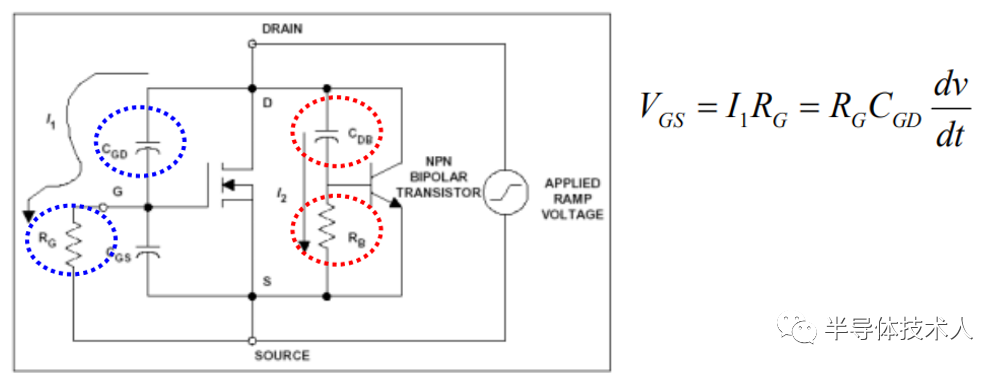

MOSFET的失效机理:什么是dV/dt失效

“dv/dt”和“di/dt”值:这些值的水平对固态继电器有什么影响?

摆脱高dV/dt电源的优势

摆脱高dV/dt电源的优势

评论