PCIe标准自从推出以来,1代和2代标准已经在PC和Server上逐渐普及,用于满足高速显卡、高速存储设备对于高速数据传输的要求。出于支持更高总线数据吞吐率的目的,PCI-SIG组织在2010年制定了PCIe 3.0,即PCIe 3代的规范,数据速率达到8Gbps。

PCIe3.0总线究竟有什么特点?对于其测试有什么特殊的地方呢?本文我们就来探讨一下。

1PCI-E 3.0简介

制定PCI-e 3代规范的目的主要是要在现有的廉价的FR4板材和接插件的基础上提供比PCI-e 2代高一倍的有效数据传输速率,同时保持和原有1代、2代设备的兼容。别看这是个简单的目的,但实现起来可不容易。

如何将数据传输速率提高一倍?

PCI-E 2代在每对差分线上的数据传输速率是5Gbps,相对于1代数据速率的两倍;而PCI-E 3代要相对于2代把速率也提高一倍,理所当然的是把数据传输速率提高到10Gbps。

但是就是这个10Gbps带来了很大的问题,因为PC和Server上出于成本的考虑,普遍使用便宜的FR4的PCB板材以及廉价的接插件,如果不更换板材和接插件,很难保证10Gbps的信号还能在原来的信号路径上可靠地传输很远的距离(典型距离是15~30cm)。因此PCI-SIG最终决定把PCI-E 3代的数据传输速率定在8Gbps。但是8Gbps相比2代的5Gbps并没有高一倍,所以PCI-E协会决定在3代标准中把在1代和2代中使用的8b/10b编码去掉。

在PCI-E 1代和2代中,为了保证数据的传输密度、直流平衡以及内嵌时钟的目的,会把8bit数据编码成10bit数据传输。因此,5Gbps的实际有效数据传输速率是5Gbps×8b/10b=4Gbps。这样,在PCI-E 3代中,如果不使用8b/10b编码,其有效数据传输速率就能比 2代的4Gbps提高1倍。

如何保证数据传输密度和直流平衡?

但是这样问题又来了,数据如果不经编码传输,很难保证数据传输密度和直流平衡,接收端的时钟恢复电路也很容易失锁。为了解决这个问题,PCI-E 3代里面采用了扰码的方法,即数据传输前,先和一个多项式进行异或,这样传输链路上的数据就看起来就比较有随机性,到了接收端再用相同的多项式把数据恢复出来。

通过上述方法,PCI-E 3代就可以用8Gbps的传输速率实现比2代的5Gbps高1倍的数据传输速率。实际应用中,PCI-E 3代的总线上也仍然有数据编码,不过采用的是128b/130b的编码,编码效率很高,由此损失的总线有效带宽比8b/10b编码小多了。

2PCI-E 3.0 发送及接收端的变化

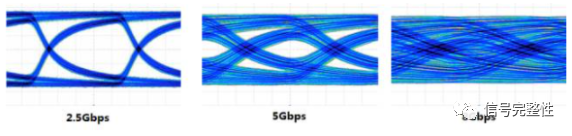

但是问题远没有结束,即使数据速率只有8Gbps,要在原有的廉价PCB和接插件上实现可靠传输也还要解决一些新的问题。其中最大的问题是信号的损耗,FR4板材对信号高频成分有很大衰减,而信号速率越高,其高频成分越多,所以衰减也就更厉害。图1是不同速率的信号经过10英寸的FR4板材的PCB传输以后信号的眼图,我们可以看到,8Gbps的信号在接收端基本上看不到眼图了,更不要说进行有效的数据接收。

▲图1 不同速率信号经过10英寸的FR4板材的PCB传输以后信号的眼图

发送端的变化

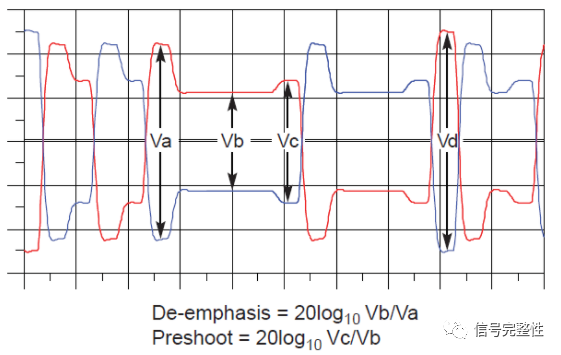

为了解决这个问题,在PCI-E的1代和2代中使用了去加重(De-emphasis)技术,即信号的发射端(TX)在发送信号时对跳变bit(代表信号中的高频成分)加大幅度发送,这样可以部分补偿一下传输线路对高频成分的衰减,从而得到比较好的眼图。PCI-E 1代中采用了-3.5db的去加重,PCI-E 2代中采用了-3.5db和-6db的去加重。而对于3代来说,由于信号速率更高,需要采用更加复杂的去加重技术,因此除了跳变bit比非跳变bit幅度增大发送以外,在跳变bit的前1个bit也要增大幅度发送,这个增大的幅度通常叫做Preshoot。图2是PCI-E 3代中采用的预加重技术对波形的影响的例子(参考资料:PCI Express Base Specification 3.0 )。

▲图2PCI-e 3.0 预加重技术对信号波形的影响

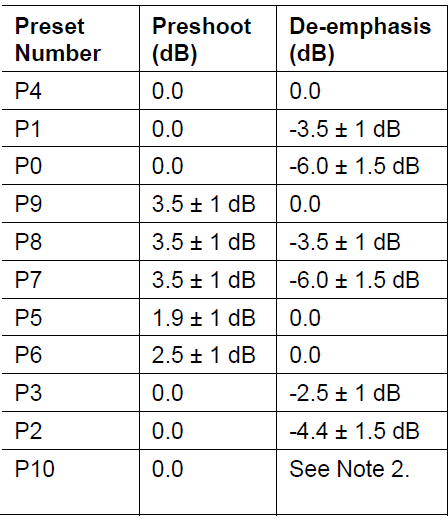

为了应对复杂的链路环境,PCI-E3代中规定了共11种不同的Preshoot和De-emphasis的组合,每种组合叫做一个Preset,实际应用中Tx和Rx端可以在Link Training阶段根据接收端收到的信号质量协商出一个最优的Preset值。下图是11种Preset的组合(参考资料:PCI Express Base Specification 3.0)。比如P4代表没有任何预加重,P7代表最厉害的预加重。

接收端的变化

那做了这些工作就够了吗?经过实验发现,仅仅在发送端对信号高频进行补偿还是不够,于是PCI-E 3代标准中又规定在接收端(RX端)还要对信号做均衡(Equalization),从而对线路的损耗进行进一步的补偿。均衡电路的实现难度较大,以前主要用在通信设备的背板或长电缆传输的场合,现在也逐渐开始在计算机领域应用,比如USB3.0中和SATA 6G中也采用了均衡技术。下图是PCI-E 3.0里对均衡器的频响特性的要求。我们可以看到均衡器的强弱也有很多档可选,在Link Training阶段TX和RX端会协商出一个最佳的组合(参考资料:PCI Express Base Specification 3.0)。

经过各种信号处理技术的结合以及大量的实验,PCI-E 3.0总算初步实现了在现有的FR4板材和接插件的基础上提供比PCI-E 2代高一倍的有效数据传输速率。但我们同时也看到,PCI-E 3代的芯片会变得更加复杂,系统设计的难度也也更大。如何保证PCI-E 3代总线工作的可靠性和很好的兼容性,就成为设计和测试人员面临的严峻挑战。

3PCI-E 3.0 发送端信号质量测试

对于发送端的测试,主要是用宽带示波器捕获其发出的信号并验证其信号质量满足规范要求。按照目前规范中的要求,PCI-E 3.0的一致性测试需要至少13GHz带宽的示波器,并配合上相应的测试夹具和测试软件。之所以PCI-E 3.0测试需要的示波器带宽相对于PCI-E 2.0来说变化不大,是因为信号的上升时间基本没变,不过如果是出于调试的目的,一般建议最好使用16GHz或以上带宽的示波器进行测试。

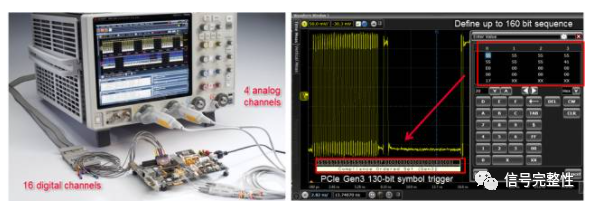

由于PCI-E 3代的信号经过传输以后信号幅度都已经衰减得很小(典型值是100mV左右),为了保证足够的测量精度,除了示波器的带宽要足够以外,还需要示波器有很低的底噪声才能保证测量的准确性和测量重复性。比如Keysight公司的高端的V或者Z系列示波器都可以用于PCI-E 3.0这样的高速信号的测试中。以V系列示波器来说,其带宽选择可从8GHz~33GHz,最高采样率80G/s,具有业内最低的底噪声和本底抖动。同时V系列示波器还可以选配高达20G/s的数字通道用于DDR3/4等总线的调试,或者选配高达160bit长度、12.5Gbps数据速率的硬件串行触发及误码检测功能,这是市面上唯一能对PCIE3.0 的128b/130b编码数据进行硬件触发和调试的示波器。

▲图3 PCI-E 3.0 发送端信号质量测试方法

在PCIE3.0的测试中,首先使用PCI-E协会提供的PCI-E 3代的夹具把被测信号引出(PCI-E3代的夹具和PCI-E 2代一样分为CBB板和CLB板,CBB板用于插卡的测试,CLB板用于主板的测试),然后通过测试夹具上的切换开关控制DUT输出PCI-E 3代的一致性测试码型。在切换板上的按键开关时,正常的PCI-E 3代的被测件依次会输出2.5Gbps、5Gbps -3dB、5Gbps -6dB、8Gbps P0、8Gbps P1、8Gbps P2、8Gbps P3、8Gbps P4、8Gbps P5、8Gbps P6、8Gbps P7、8Gbps P8、8Gbps P9、8Gbps P10的码型。需要注意的一点是,由于PCI-E 3代信号如前所述共有11种Preset值,测试过程中应明确当前测试的是哪一种Preset值,做信号质量测试常用的有Preset7、Preset8、Preset1、Preset0等。下图是PCI-E 3代的CBB板及一致性测试码型。

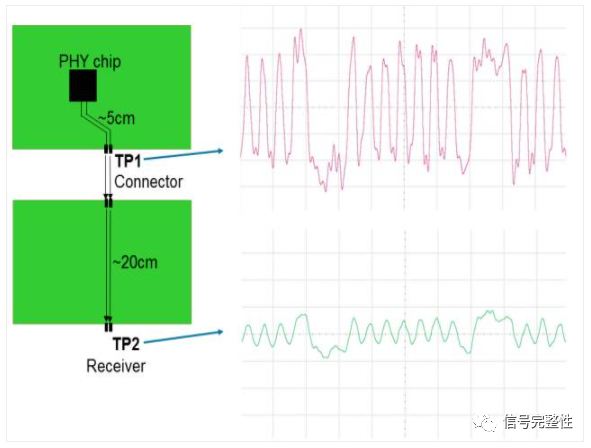

另外,由于PCI-E 3代的标准里,在接收芯片侧使用了信号均衡技术,而且均衡器对于最终信号质量做了改善调整。为了把传输通道对信号的恶化以及均衡器对信号的改善效果都考虑进去,PCI-E 3代的测试里很重要的一点是其发送端眼图、抖动等测试的参考点是在接收端。也就是说,即使我们是在发送端进行测试,在进行眼图、抖动等测试时也不是直接测试发送端的波形,而是需要把传输通道对信号的恶化的影响以及均衡器对信号的改善影响都考虑进去。图4比较直观地显示出了在不同位置信号质量的情况。

▲图4 PCI-e 3.0信号在传输过程中的信号质量的变化

为了模拟出传输通道和芯片封装对信号的影响,测试中需要做传输通道参数的嵌入操作,即Embed。这个传输通道的模型是PCI-E协会以S参数文件的形式提供的,测试过程中需要示波器能把这个S参数文件的影响加到被测波形上。同时,测试过程中示波器是用两个通道分别连接信号的正负端,要得到最后的差分波形需要示波器对两个通道的波形做相减运算。如果波形相减和S参数嵌入的工作都由示波器软件计算,会大大影响测试速度,因此有些公司的高端示波器内部会有硬件的通道相减及S参数运算功能,可以大大提高测试的速度和效率。

对测试数据做分析的方法有2种:一种是使用PCI-SIG提供的Sigtest软件做手动分析;一种是使用示波器厂商提供的自动测试软件。

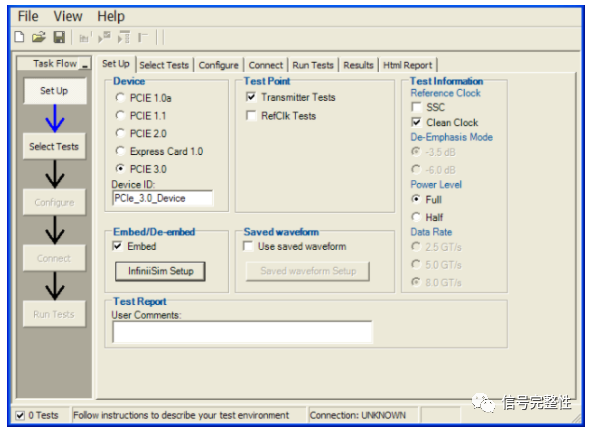

Sigtest软件算法由PCI-SIG免费提供,可以进行信号的眼图、模板、抖动的测试,但是需要用户手动捕获数据进行后分析,不熟练的测试人员, 经常由于设置不对造成测试结果不一致,而且其测试项目有限,没有覆盖全部的信号要求。所以针对PCI-E3.0的测试有些示波器厂商还提供了相应的自动化测试软件,比如Keysight公司的N5393D自动化测试软件。这个软件以图形化的界面指导用户完成设置、连接和测试过程,除了可以自动进行示波器测量参数设置以及自动生成报告外,还提供了Swing、Preset、Common Mode等更多测试项目以,提高了测试的效率和可重复性。除此以外,这个软件在测试过程中还会对被测件发出的码型和速率进行检查,以确认测试使用的是规范要求的正确码型。另外,很重要的一点是,在N5393D软件里,使用的是和SigTest软件完全一样的分析算法,从而可以保证分析结果和SigTest软件的一致性。图5是N5393D软件的设置界面。

▲图5 N5393D软件的设置界面

因此,简单来说,对于以前从事PCI-E 2.0的测试人员来说,进行PCI-E 3.0的测试除了需要重新购置PCI-E3.0的测试夹具CLB3和CBB3以外(其实原有的CLB2和CBB2等针对PCI-E2.0测试的夹具勉强也仍然可以用于PCI-E3.0的发送信号测试中),PCI-E3.0的信号测试相对于PCI-E2.0来说硬件设备的变化不大,基本使用13GHz或16GHz带宽的示波器就可以,但是测试软件对于测试数据的处理变得更加复杂了。数据分析时除了要嵌入传输通道和芯片封装的线路模型以外,还要把均衡器对信号的改善也考虑进去,好在无论是PCI-E协会提供的免费的Sigtest软件还是Keysight公司的N5393D自动测试软件都可以为PCI-E3.0的测试提供很好的帮助。

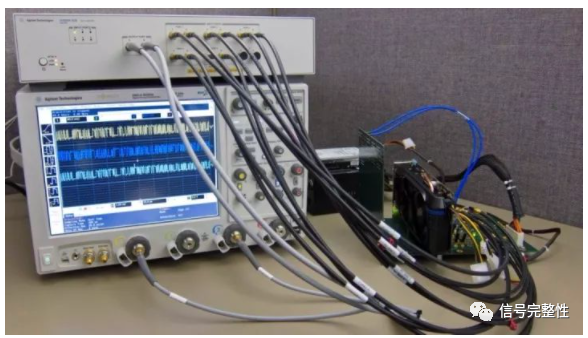

此外,由于PCI-E总线上要测试的数据Lane的数量很多,虽然测试项目可以由软件自动完成,但是连接还是需要人工进行,因此每测试完一对差分线就需要测试人员来更改一下连接,非常麻烦。为了提高测试效率,可以把示波器配合相应的微波开关矩阵使用,微波开关矩阵可以在自动测试软件的控制下根据需要进行信号的切换。这样测试人员只需要一次把所有的被测信号都连接到开关矩阵上,然后运行测试软件就可以了。图6是在PCI-E的测试中配合开关矩阵使用的情况。

▲图6 PCI-E测试中配合开关矩阵使用

4PCI-E 3.0 接收端容限测试

在PCI-E 1.0和2.0的时代,接收端测试不是必须的,通常只要保证发送端的信号质量基本就能保证系统的正常工作。但是对于PCI-E3.0来说,由于速率更高,发送端发出的信号经过长线传输后信号质量总是不会太好,所以接收端使用了复杂的均衡技术来提升接收端的接收能力。由于接收端更加复杂而且其均衡的有效性会显著影响链路传输的可靠性,因此在PCI-E3.0时代,接收端的测试变成了必测的项目。

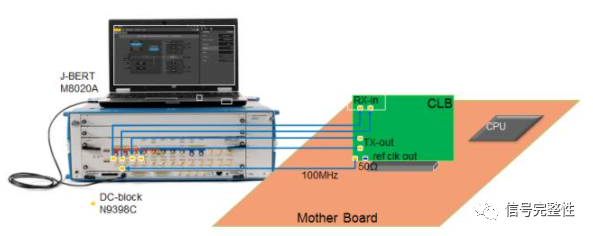

Keysight的M8020A是高性能的串行误码仪,其单路可以产生16.2Gbps的高速数据流,固有抖动只有300fs(RMS),同时其内部集成时钟恢复电路、预加重模块、噪声注入、参考时钟倍频、信号均衡电路等,非常适合PCIE3.0接收测试这种速率高同时对信号质量又有很好要求的场合。除此以外,M8020A支持到16.2Gbps信号的8阶的预加重,可以充分满足未来PCIE4.0的接收测试的要求。图7是用 M8020A进行PCI-E 3.0接收测试的一个示意图。

▲图7 PCI-E 3.0接收端测试示意图。

所谓接收端测试,就是要验证接收端对于恶劣信号的容忍能力。这就涉及到两个问题,一个是这个恶劣信号怎么定义,另一个是怎么判断被测系统能够容忍这样的恶劣信号。

首先来看一下这个恶劣信号的定义,这不是一个随便的差信号就可以,这个信号的恶劣程度有精确定义才能保证测量的重复性。这个恶劣信号通常叫做Stress Eye,即压力眼图,实际上是借鉴了光通信里的叫法。这个Stress Eye实际上是用高性能的误码仪先产生一个纯净的带预加重和Preshoot的8Gbps的信号,然后在这个信号上叠加上精确控制的随机抖动(RJ)、周期抖动(SJ)、差模和共模噪声以及码间干扰(ISI)。为了确定每个成分的大小都符合规范的要求,所以测试之前需要先用示波器对误码仪输出的信号进行校准,确定产生的是规范要求的Stress Eye。其中信号的RJ、SJ、共模噪声等都可以由误码仪产生,而ISI抖动是由PCI-E协会提供的CLB3或CBB3夹具产生,其夹具上会模拟典型的主板或者插卡的PCB走线对信号的影响。

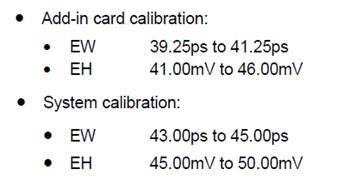

为了方便接收测试,CLB3和CBB3夹具相对于前一代夹具做了一些电路的改动,主要是考虑了接收测试的情况。比如为了切换测试码型,在PCI-E2.0的CLB2夹具上,从主板发过来的RefClk是直接环回到主板的Lane0的接收端,不能断开;而在PCI-E3.0的CLB3的夹具上,由于要考虑到可能还会对主板Lane0的接收端进行测试,因此这个连接是通过SMP的跳线完成的。另外,在CBB3的夹具上,增加了专门的Riser板以模拟服务器等应用场合的走线对信号的影响。要精确产生PCI-E3.0要求的压力眼图需要调整很多参数,比如需要调整输出信号的幅度、预加重、差模噪声、随机抖动、周期抖动等以满足眼高、眼宽和抖动的要求。而且各个调整参数之间也会相互制约,比如调整信号的幅度时,除了会影响眼高也会影响到眼宽,因此各个参数的调整需要反复进行以得到一个最优化的组合。校准中会调PCI-SIG的Sigtest软件对信号进行通道模型嵌入和均衡,并计算最后的眼高和眼宽。如果没有达到要求,会在误码仪中进一步调整注入的随机抖动和差模噪声的大小,直到眼高和眼宽达到以下参数要求:

校准时,信号的参数分析和调整需要反复进行,人工操作非常耗时耗力。为了解决这个问题,Keysight公司在业内最早推出了N5990A的针对PCI-E3.0接收容限的自动测试软件,这个软件可以提供设置和连接向导、控制误码仪和示波器完成自动校准、发出训练码型把被测件设置成环回状态并自动进行环回回来数据的误码率统计。

设置被测件进入环回模式有两种方式,一种是借助于误码仪本身的Training序列,另一种是借助于芯片厂商提供的工具(比如Intel公司的ITP工具)。传统的误码仪不具有对于PCIE协议理解的功能,只能盲发训练序列,缺点是没有经过正常的预加重和均衡的协商,这就可能造成不能把被测件设置成正确的状态。而很多新的CPU平台要求误码仪和被测件进行有效的预加重和均衡的沟通,然后再进行环回,这就要求误码仪能够识别对端返回的训练序列并做相应的调整。M8020A平台集成了Link协商的功能,能够真正和被测件进行训练序列的沟通,可以有效地把被测件设置成正确的环回状态。

当被测件进入环回模式并且误码仪发出压力眼图的信号后,被测系统会把其从RX端收到的数据再通过TX端发送出来送回误码仪,误码仪通过比较误码来判断数据是否被正确接收,测试通过的标准是要求误码率小于1E-12。

-

信号

+关注

关注

11文章

2804浏览量

77046 -

总线

+关注

关注

10文章

2900浏览量

88320 -

PCIe

+关注

关注

15文章

1258浏览量

83085 -

PCIE3.0

+关注

关注

0文章

14浏览量

7119 -

单元测试

+关注

关注

0文章

42浏览量

3179

原文标题:【硬件的单元测试_3】PCIe 3.0测试

文章出处:【微信号:Hardware_10W,微信公众号:硬件十万个为什么】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

嵌入式系统开发中的测试方法 嵌入式系统开发与AI结合应用

开发者必读!CircleCI 组件测试与单元测试全解析

汽车软件单元测试的重要性

严格的单元测试造就完美的软件

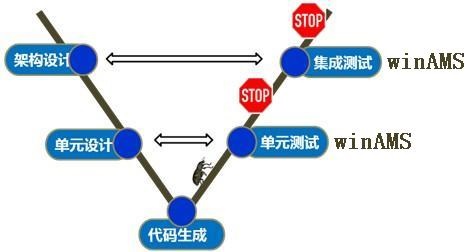

嵌入软件单元/集成测试工具专业分析

如何测试PCIe插槽的速度

PCIe 4.0与PCIe 3.0的性能对比

鸿蒙语言基础类库:ohos.application.testRunner TestRunner 测试

pcie4.0和pcie3.0接口兼容吗

单元测试、集成测试自动化工具

接口测试的工具有哪些种类

LitePoint推出其最新的5G O-RAN无线电单元测试技术

单元/集成测试服务

硬件的单元测试:PCIe 3.0测试

硬件的单元测试:PCIe 3.0测试

评论