在笔者看来,市场对新兴存储器并不友善,尽管人们仍然希望存内计算(copute in memory)能够重振基于电阻、相变和其他特性的新型存储器。

不过,这并没有阻止存储器的研发,当前的新兴存储器领域的大部分研究现在都集中在铁电存储器(ferroelectric memories)上,如IEDM内存分委会约有三分之一的研究人员从事FeRAM研发。其中锆酸铪 (HZO:hafnium zirconate) 和其他材料的极化(正或负)可以通过施加电压来控制。

存储技术委员会主席兼首尔国立大学教授 Sang Bum Kim 在 IEDM会议上也指出,FeRAM 比 DRAM 慢,但比 NAND 快。而且它们真的很小。不过,他们还有很多材料问题需要解决,其循环耐力和保持力(cycling endurance and retention)仍然没有达到应有的水平。

从IEDM的统计数据看来,中国的FeRAM研究已经达到了一相当高的水平。例如,来自北京大学的一个研究小组考虑了一个棘手的问题,那就是如何在 HZO 晶体中保持正斜方相(orthorhombic phase),这是铁电效应所需的相。“我们系统地表征了 La 掺杂 HfO2 器件中出色的铁电性。观察到超过 38 nm 的大单晶斜方晶相。实现了超快速和高可靠性的偏振切换。”中国研究人员在报告说。

如何在铁电材料中保持O-phase这一挑战促使英特尔创建了一个复杂的模型,该模型着眼于电场循环过程中的相变。英特尔表示:“拥有一个可以描述所有这些阶段的统一理论框架对于更好地理解场循环过程中的潜在物理机制以及探索基于氧化铪薄膜(hafnia-based thin films)的混合阶段的设备设计非常重要。”

中国团队的新型存储器研究

正如前文所说,中国北京大学团队在IEDM 2022上发布了一些研究进展。北京大学集成电路学院也撰文分享了其在新型存储器及可靠性研。需要强调一下,本章节内的主要内容都是引自北京大学集成电路学院的新闻稿,仅供读者学习,其内容版权归北京大学所有。

DRAM作为存储器市场的主力军,传统的1T1C结构在10nm节点附近面临巨大的瓶颈。后道兼容的宽禁带氧化物半导体基2T0C DRAM,具有极低的关态漏电流,热预算低,与硅基后道工艺兼容,可以在数据保持时间、功耗与密度上实现突破。然后,氧化物半导体特殊的渗流输运机制导致了其高阈值电压与高开态电流不可兼得,从而需要负保持电压来实现高数据保持时间,并且写入速度也远低于当前主流水平。

针对上述问题,吴燕庆研究员、黄如院士团队对基于宽禁带氧化物半导体IGZO的晶体管载流子迁移率与源漏接触进行优化,实现了阈值电压在100 pA*W/L的标准下大于1.2V,同时输出电流在过驱动电压为1V下达到24 mA/mm,栅压为0时的关态电流在常温和85℃下均小于10-19A/mm。2T0C DRAM单元成功实现了10 ns的超快写入速度,以及室温断电情况下数据保持时间大于10ks和85℃下保持时间大于7ks,分别为之前同类工作的10倍与100倍。此外,通过调节写入管的字线和位线电压,成功在常温和85℃下实现了具有超高区分度和线性度的3-bit存储,并可通过电压协同调节进一步扩展存储容量。该工作展示了宽禁带氧化物半导体在三维集成的大容量、高密度、非易失DRAM方向应用的潜力。

氧化铪基薄膜铁电材料由于其与硅基工艺的兼容性,近年来受到广泛的关注和研究。如何通过掺杂适合的元素以制备出具有优异铁电性的薄膜材料,是铪基铁电材料的重要问题。此外,如何在ns量级脉冲下获得足够的极化翻转量也是实现高速非易失存储的关键。针对以上问题,吴燕庆研究员、黄如院士团队提出了通过镧元素掺杂氧化铪薄膜提升铁电性的方法,系统研究了其铁电回滞特性以及翻转特性。实验表征到超过38nm的大尺寸正交铁电相(O相)单晶,在5ns脉冲下实现了文献中最高的超过60mC/cm2的极化翻转量,实现了1.3×104A/cm2的最高翻转电流。提出了新的反映翻转特性的参数-翻转电导G,并测量到了最高的1.03×104S/cm2的翻转电导。

铪基铁电晶体管(FeFET),由于其与CMOS工艺兼容性好、可微缩性强和低功耗等优势,在嵌入式和存储级内存等存储器应用领域具有广泛的前景。针对铪基FeFET耐久性低(<106)的问题,唐克超研究员、黄如院士课题组从硅沟道FeFET的器件原理出发,提出了铁电层-中间层协同优化的耐久性改善新方法;结合第一性原理计算的理论预测,选取了Al:HfO2铁电层和Al2O3中间层的材料组合,具有较低的电荷俘获密度和较长的俘获时间常数,利于耐久性的提升。优化后器件的耐久性超过5×109,超过通常报道的FeFET耐久性三个数量级以上,并具有10年以上的保持特性。研究成果对高耐久性的硅沟道FeFET提供了重要指导。

针对FeFET写后读延迟和循环操作中存储窗口退化机理不清晰的问题,王润声教授、黄如院士课题组与合作者首次对不同应力条件下器件中缺陷的物理性质进行了全面的实验研究。通过eMSM、DMP和RTN等先进表征方法,发现写后读延迟和存储窗口退化的可靠性根源分别来自两种不同的缺陷,并揭示了它们在循环电应力下的动力学行为变化,为厘清FeFET的缺陷物理本质、改善器件可靠性提供了重要的依据。

四层铁电容器堆栈

根据 Intel 在最近的技术会议上也发表了相关论文,很明显,Intel 正在紧追 FeRAM,以此作为提供快速、密集、嵌入式 L4 缓存的一种方式。在 IEDM 2022 上,英特尔研究员 Shriram Shivaraman 发表了题为“Hafnia-Based FeRAM: A Path Toward Ultra-High Density for Next-Generation High-Speed Embedded Memory”的受邀论文。该演示文稿描述了创建具有四层 FeRAM 电容器堆叠层的嵌入式存储器的能力,这表明堆叠电容器可以实现与传统 AFE(anti ferroelectric)沟槽电容器相同的行为,并且架构变化不会影响 AFE 电容器的结晶和电气特性。

负责 imec 铁电项目的 imec研究员 Jan Van Houdt 则对此持谨慎态度。当被问及(正交)O-phase是否难以在 HZO 中保持时,Van Houdt 说:“我们仍在努力优化材料。

他接着指出,我们绝对希望拥有一种在加工过程中稳定的材料,一种在使用寿命结束前保持相同相组成的材料,虽然我们现在还没有。但它将是一种动态材料,随温度而变化,随循环而变化。如果我们在设备上做一些压力测试,它就会改变。这是一个不便的事实,我们不能完全控制材料的成分。与 DRAM 电容器中的常规电介质或其他控制非常好的材料完全不同。

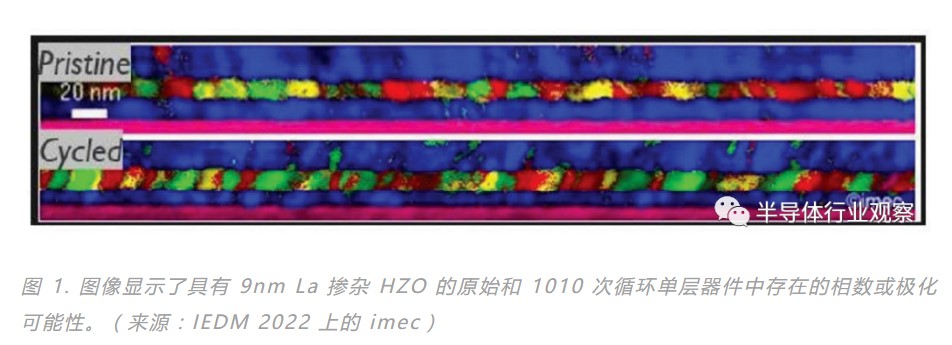

Van Houdt 说,一个乐观的事实是原子级沉积 (ALD) 与锆酸铪 (HZO) 薄膜配合得很好。“有了锆酸铪,我们就有了 ALD,这让 imec 看到了希望。我想我们会成功的。但以何种形式,这仍在争论中。有一件事是肯定的,不再只是学术界在研究这个了。它已经转向业界。” 图 1 显示了 HZO 设备中的相数或极化可能性。

正如IL(interfacial)层在 CMOS 逻辑中起着至关重要的作用一样,imec 研究人员在 IEDM 2022 上展示了界面工程( interfacial engineering)工作,研究了 IL 种子(seed)层和覆盖(cap)层如何“显著改善”基于 La 掺杂 HZO 的铁电电容器,包括铁电响应和剩余极化 (PR:remnant polarization)。

imec 团队在具有 TiN 顶部和底部电极的BL( bilayer) 和/或TL (trilayer) 配置中创建了 1 nm TiO2seed层和/或 2nm Nb2O5cap层。“我们展示了 Nb2O5cap 如何通过在 HZO 中注入氧气来促进从((anti-FE)四方相(tetragonal)到(FE)正交相(orthorhombic phase)的转变,并发现 TiO2seed层有利于改善 HZO 内部的晶粒取向,从而带来更高的 2PR 和减少的唤醒。最后,根据所使用的 Hf 和 Zr 的前体( precursors),我们展示了两种 trilayer器件的耐久性高达 1011次循环,其在1.8 MV/cm能获得约为30μC/cm²的2PR。在3 MV/cm的时候,历经 3x106的循环以后,更是获得了一个创纪录的66.5μC/cm²的2PR。”Van Houdt 说。

imec 团队成员 J. Bizin davyi 表示,Bilayer 和trilayer堆叠可以成功组合以提高铁电性,同时仍具有出色的耐用性。

从IGZO 氧化物半导体受益

有趣的是,日本研究人员在 IEDM 上展示了将 FeRAM 电容器与基于铟镓锌氧化物 (IGZO) 的氧化物半导体制成的控制设备相结合的工作,IGZO 是会议上的另一个热门话题。Semiconductor Energy Laboratory Co., Ltd.(日本厚木)描述了一种使用氧化物半导体场效应晶体管 (OSFET) 和铁电电容器的 FeRAM,“利用 OSFET 的高击穿电压,即使栅极长度成比例 ” 。这家以研发为导向的公司报告称,其 FeRAM 具有前所未有的尺寸——0.06μm²,实现了 10 ns 的写入时间,在 85°C 下的保留时间为 1,000 分钟或更长时间。在2.5V的工作电压,它更是展现出了108的耐受循环。

“这种内存具有较高的运行速度、非易失性以及较高的重复写入耐久性,因此将成为未来新兴内存的候选者,”SEL在其论文中写道。

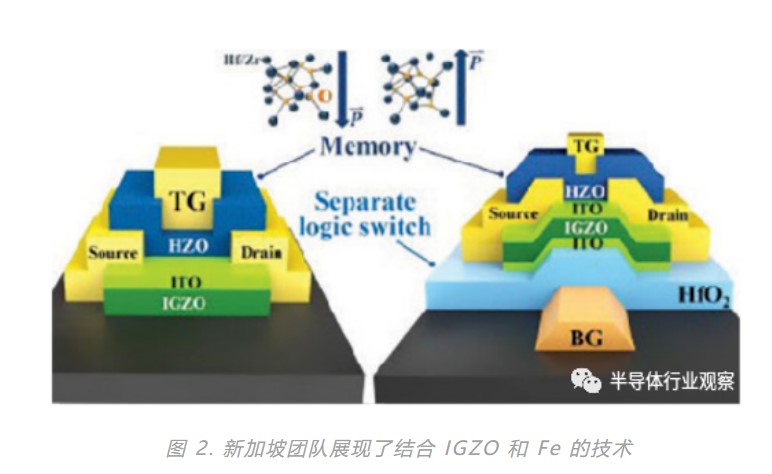

新加坡国立大学的一篇论文还在 BEOL 兼容的非易失性开关中结合了 IGZO 器件和铁电 HZO 电容器,这是一种 FPGA 类型的器件,NUS 团队称之为 MemTransistor(图 2)。Soitec声称首次展示了与 BEOL 兼容的“3D Fin-Gate 氧化物半导体 Fe-FET。

三星追逐MRAM

除了铁电存储器外,MRAM 在 IEDM 2022 上也受到关注,三星在两个背靠背的演示中详细介绍了其 MRAM 进展。J.H. Park 详细介绍了三星在 STT-MRAM 方面的大量工作,他说,与 SRAM 相比,STT-MRAM 在速度、尺寸和耐用性方面具有许多优势。”

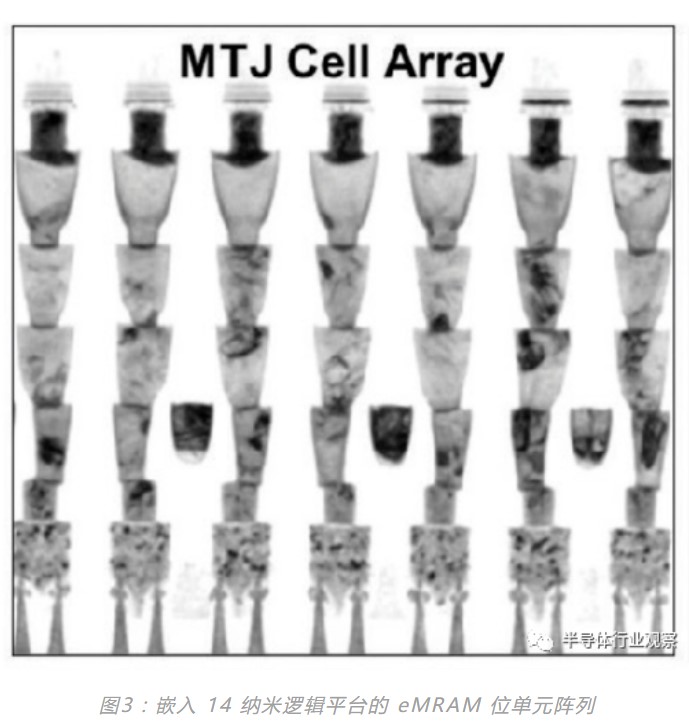

在接下来的演讲中,T.Y. Lee 描述了“用于非易失性 RAM 应用的世界上最节能的 MRAM 技术”。将磁隧道结 (MTJ) 缩小到 14 纳米 FinFET 节点,可使面积缩小 33%,读取时间加快 2.6 倍(图 3)。“MRAM 具有用作低泄漏工作存储器的良好潜力,”Lee 说。

三星的研究人员声称,他们开发的这个产品是有史以来最小、最节能的非易失性随机存取存储器。

该团队采用了该公司的 28 纳米嵌入式 MRAM,并将磁性隧道结扩展到 14 纳米 FinFET 逻辑工艺。论文摘要涉及该团队生产的独立存储器,其写入能量要求为每位 25pJ,以每秒 54MB 的数据速率进行读取的有源功率要求为 14mW,写入的有源功率要求为 27mW。循环是1014个周期,当缩放到 16Mbit 设备时,芯片将占用 30 平方毫米。

按照三星所说,该研究的目标之一是证明嵌入式 MRAM 作为缓存存储器适用于依赖大型数据集和分析的应用程序(例如边缘 AI)的适用性。

审核编辑:刘清

-

DRAM

+关注

关注

40文章

2337浏览量

184923 -

存储器

+关注

关注

38文章

7610浏览量

165872 -

CMOS工艺

+关注

关注

1文章

59浏览量

15831 -

IEDM

+关注

关注

0文章

5浏览量

11380 -

驱动电压

+关注

关注

0文章

83浏览量

13611

原文标题:IEDM 2022上的新型存储

文章出处:【微信号:光刻人的世界,微信公众号:光刻人的世界】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

AI驱动新型存储器技术,国内新兴存储企业进阶

IEDM 2022上的新型存储器简介

IEDM 2022上的新型存储器简介

评论