“开关噪声-EMC基础篇”前后共有21篇文章,本文是最后一篇。从“EMC基础”知识开始,以开关电源为前提分别介绍了“降噪对策(步骤与概要)”、“使用电容器降低噪声”、“使用电感降低噪声”、“其他降噪对策”相关的基础内容。本文将对各篇文章的关键要点做最终总结。

<EMC基础>

▶何谓EMC

关键要点

・EMC(电磁兼容性)是指兼备EMI和EMS两方面的性能。

・EMI(电磁干扰)是指因辐射/发射(Emission)电磁波而对环境产生的干扰。

・EMS(电磁敏感性)是指对电磁波干扰(EMI)的耐受性/抗扰度(Immunity)。

▶频谱基础

关键要点

・当频率升高时,频谱振幅整体增加。

・上升/下降延迟时,进入-40dB/dec衰减时的频率降低,频谱的振幅衰减。

・Duty变更时,虽然会产生偶次谐波,但对谱峰无影响。基波频谱衰减。

・仅上升延迟时,tr分量从更低的频率开始衰减。

▶差模(常模)噪声与共模噪声

关键要点

・电磁干扰EMI大致可分为“传导噪声”和“辐射噪声”两种。

・传导噪声可分为差模(常模)噪声和共模噪声两类。

・关于辐射噪声,差模噪声的线缆环路面积、共模噪声的线长是非常重要的因素。

・注意;即使条件相同,共模噪声带来的辐射远远大于差模噪声。

▶何谓串扰

关键要点

・平行的布线间会产生串扰。

・串扰的因素有杂散(寄生)电容引发的电容(静电)耦合和互感引发的电感(电磁)耦合。

▶开关电源产生的噪声

关键要点

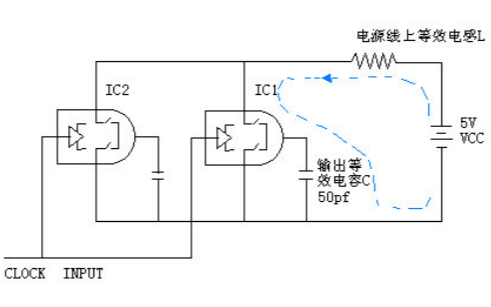

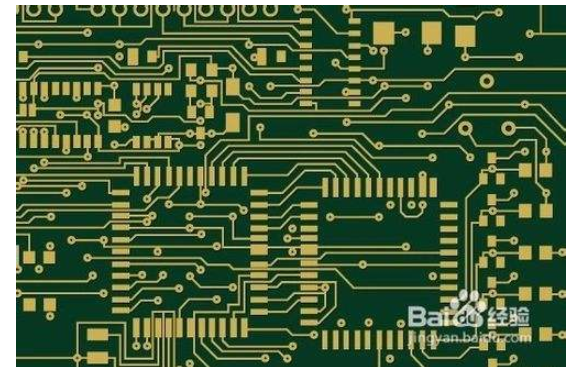

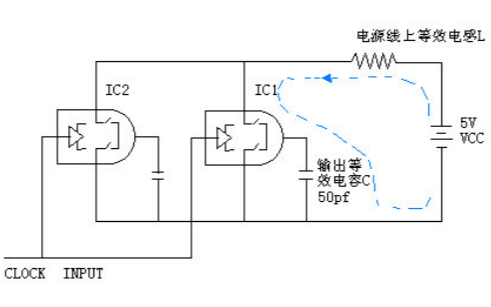

・在开关时会产生急剧电流ON/OFF的环路中,会因寄生分量产生高频振铃=开关噪声。

・这种开关噪声可通过优化PCB板布线等来降低,但即使这样,残留的噪声也会作为共模噪声传导至输入电源,因此需要采取防止噪声漏出的措施。

<降噪对策>

▶降噪对策步骤

关键要点

・随着开发进程的推进,可使用的降噪对策技术和手段越来越有限,对策成本也越来越高。

・在产品开发的初期阶段,预先进行充分探讨与评估,可以从容有效地采取降噪对策。

・掌握噪声的种类和性质,并针对不同的噪声采取不同的有效对策是非常重要的。

・降噪对策按照“把握频率成分→把握产生源和传导路径→强化GND→增加降噪部件”的步骤进行。

▶开关电源噪声对策的基础知识

关键要点

・要想降低差模噪声,可在电路板上缩小大电流路径的环路面积,并增加最优解耦和输入滤波器。

・尽可能地抑制噪声的发生源–差模噪声是非常重要的,也关系到降低共模噪声。

・要想降低共模噪声,可缩短布线,抑制串扰,切断(滤波)共模路径。

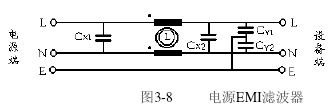

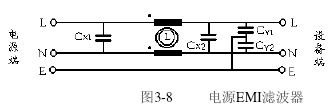

▶开关电源的输入滤波器

关键要点

・开关电源的输入滤波器,需要针对共模噪声和差模噪声分别采用不同的处理。

・对共模噪声使用共模滤波器。

・对差模噪声使用由电容器、电感、磁珠、电阻等部件组成的滤波器。

<使用电容器降低噪声>

▶电容的频率特性

关键要点

・降噪用电容器的选型需要根据阻抗的频率特性进行(而非容值)。

・容值和ESL越小,谐振频率越高,高频区域的阻抗越低。

・容值越大,容性区域的阻抗越低。

・ESR越小,谐振频率的阻抗越低。

・ESL越小,感性区域的阻抗越低。

▶使用电容器降低噪声

关键要点

・通过降低目标噪声频率的阻抗来降低噪声幅度。

・降噪用电容器的选型需要根据阻抗的频率特性进行(而非容值)。

▶去耦电容的有效使用方法要点1

关键要点

・去耦电容的有效使用方法有两个要点:①使用多个电容,②降低电容的ESL。

・使用多个电容时,容值相同时和不同时的效果不同。

▶去耦电容的有效使用方法要点2

关键要点

・去耦电容的有效使用方法有两个要点:①使用多个电容,②降低电容的ESL。

・通过降低电容的ESL,可改善高频特性,并可更有效地降低高频噪声。

・有的电容虽然容值相同,但因尺寸和结构不同而ESL更小。

▶去耦电容的有效使用方法其他注意事项

关键要点

・理解Q与频率-阻抗特性之间的关系,并根据目的区分Q的差异。

・高Q电容窄带阻抗急剧下降。低Q电容在较宽频段相对平缓下降。

・PCB图形的热风焊盘等会增加电感分量,使谐振频率向低频端移动。

・探讨对策时的试装,如果不按照现实的修改实际安装,很可能在修改后的PCB板上无法获得探讨时的效果。

・电容量变化率大时,谐振频率会变化,无法获得目标频率理想的噪声消除效果。

・在温度条件和变动较大的严苛应用中,可以探讨使用具有CH、C0G特性的温度特性优异的电容。

▶去耦电容的有效使用方法总结

<使用电感降低噪声>

▶电感的频率特性

关键要点

・电感在谐振频率之前呈现感性特性(阻抗随频率升高而增加)。

・电感在谐振频率之后呈现容性特性(阻抗随频率升高而减小)。

・在比谐振频率高的频段,电感不发挥作为电感的作用。

・电感值L变小时,电感的谐振频率会升高。

・电感的谐振点阻抗受寄生电阻分量的限制。

▶使用电感和铁氧体磁珠降低噪声的对策

关键要点

・用于降噪对策的电感,大致可以分为绕组型电感构成的滤波器和利用铁氧体磁珠进行热转换两种。

・铁氧体磁珠与普通电感相比,具有电阻分量R较大、Q值较低的特性。

・普通的电感可容许较大的直流叠加电流,只要在其范围内,阻抗不怎么受直流电流的影响。

・铁氧体磁珠对于直流电流容易饱和,饱和会导致电感值下降,谐振点向高频段转移。

・普通电感构成的滤波器,可选电感值的范围较宽。

・铁氧体磁珠的Q值较低,因此在较宽频率范围内具有有效的降噪效果。

▶使用共模滤波器降低噪声的对策

关键要点

・使用共模滤波器消除对共模噪声。

・共模滤波器是利用自感作用来阻止共模电流通过的滤波器。

▶注意点 : 串扰、GND线反弹噪声

关键要点

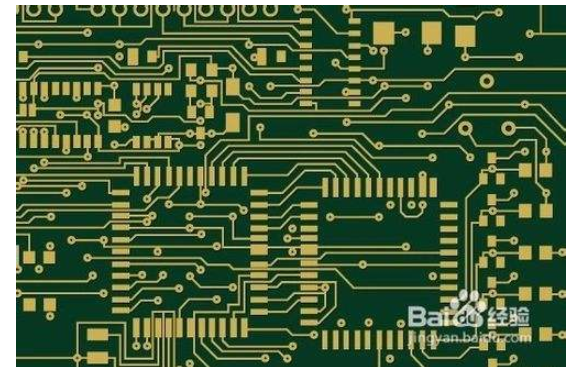

・有些PCB板布线布局,会因串扰而导致滤波效果下降。

・Π型滤波器的电容的GND的某些设置方法可能会带来地线反弹噪声。

・优化PCB板布线布局可避免这些问题。

▶使用电感降低噪声 总结

<其他降噪对策>

▶RC缓冲电路

关键要点

・RC缓冲电路可通过电阻将寄生电容、寄生电感等产生的尖峰电压转换为热,从而降低尖峰电压。

・增加缓冲电路可能会导致效率降低,因此需要探讨噪声水平和效率之间的平衡点。

・电阻是将噪声电压转换为热,因此需要注意电阻的容许损耗。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

相关推荐

本帖最后由 eehome 于 2013-1-5 09:56 编辑

EMI-EMC设计积验总结

发表于 08-09 13:24

EMI-EMC设计积验总结

发表于 08-20 13:07

1、为什么数字电路的地线和电源线上经常会有很大的噪声电压?怎样减小这些噪声电压? 数字电路工作时会瞬间吸取很大的电流,这些瞬变电流流过电源线和地线时,由于电源线和地线电感的存在,会产生较大的反冲电压,这就是观察到的噪声电压。减小这些噪声电压的方法一是减小电源线和地线的电感,如使用网格地、地线面、电源线面等,另一个方法是在电源线上使用适当的解耦电容(储能电容)。 2、在实践中,常见到将多股导线绞起来作为高频导体,据说这样可以减小导线的射频阻抗,这是为什么? 这样增加了导线的表面积,从而减小了高频电阻。 3、电路或线路板电磁兼容性设计时要特别注意关键信号的处理,这里的关键信号指那些信号? 从电磁发射的角度考虑,关键信号线指周期性信号,如本振信号、时钟信号、地址低位信号等;从敏感度的角度考虑,关键信号指对外界电磁干扰很敏感的信号,如低电平模拟信号。 4、怎样防止搭接点出现电化学腐蚀现象? 选择电化学电位接近的金属,或对接触的局部进行环境密封,隔绝电解液。 5、什么是搭接,举出几种搭接的方法。 金属构件之间的低阻抗(射频)连接称为搭接,搭接的方式有焊接、铆接、螺钉连接、电磁密封衬垫连接等。 6、请尽可能多的列出降低地线射频阻抗的方法。 尽量使用表面积大的导体,以减小高频电流的电阻;尽量使导体短些,以减小电阻和电感;在导体表面镀银,减小表面电阻;多根导体并联,减小电感。 7、为什么在有些进口样机中看到有些地线通过电容或电感接地? 为了使地线系统对于不同频率的信号呈现不同的地线结构。 8、导致地线干扰问题的根本原因是什么? 地线的阻抗是导致地线问题的根本原因,由于地线阻抗的存在,当地线上流过电流时,就会产生电压,形成电位差,而我们在设计电路时,是假设地线上各点电位是相同的,地线电位是整个系统工作的参考电位,实际地线电位与假设条件的不同导致了各种各样的地线问题。 9、在进行电磁干扰问题分析时,往往用什么定义来描述地线? 将地线定义为信号的回流线。 10、当穿过面板的导线很多时,往往使用滤波连接器或滤波阵列板,在安装滤波连接器或滤波阵列板时要注意什么问题? 要在滤波连接器或滤波阵列板与机箱面板之间安装电磁密封衬垫或用导电胶带将缝隙粘起来,防止缝隙处的电磁泄漏。

发表于 09-27 11:15

EMI-EMC设计积验总结

发表于 09-15 17:05

华为的EMC设计资料:本书对PCB的EMC设计现有成果加以总结,推广,同时对一些未知的领域进行积极的探索。结合PCB设计过程中的经验教训以及产品的EMC测试数据。

发表于 04-01 19:08

•0次下载

华为的EMC设计资料:本书对PCB的EMC设计现有成果加以总结,推广,同时对一些未知的领域进行积极的探索。结合PCB设计过程中的经验教训以及产品的EMC测试数据。

发表于 02-24 09:33

•0次下载

华为pcb的emc设计指南:本书对PCB的EMC设计现有成果加以总结,推广,同时对一些未知的领域进行积极的探索。结合PCB设计过程中的经验教训以及产品的EMC测试数据。

发表于 02-24 09:34

•0次下载

电磁兼容性EMC(Electro Magnetic Compatibility)是指设备或系统在其电磁环境中符合要求运行并不对其环境中的任何设备产生无法忍受的电磁干扰的能力。因此,EMC包括两个方面

发表于 07-07 09:24

•7883次阅读

此文档为EMC设计指导文件本文档的主要内容详细介绍的是电磁兼容EMC的设计总结。

整体布局

1、高速、中速、低速电路要分开;

2、强电流、高电压、强辐射元器件远离弱电流、低电压、敏感元器件

发表于 09-20 08:00

•7次下载

本书旨在对我司PCB的EMC设计现有成果加以总结、推广,同时对一些未知的领域进行积极的探索。结合我司PCB设计过程中的经验教训以及产品的EMC测试数据,我们对PCB的EMC设计进行了较

发表于 12-18 08:00

•0次下载

RJ45以太网口EMC设计总结

发表于 12-30 11:07

•86次下载

本书旨在对我司PCB的EMC设计现有成果加以总结、推广,同时对- -些未知的领域进行积极的探索。结合我司PCB设计过程中的经验教训以及产品的EMC测试数据,我们PCB的EMC设计进行了

发表于 06-06 10:45

•0次下载

EMC设计总结

发表于 12-30 09:20

•4次下载

转载一篇华为《PCB的EMC设计指南》,合计94页PDF,对PCB的EMC设计从布局、布线、背板的EMC设计、射频PCB的EMC设计等方面做了系统的

![的头像]() 发表于

发表于 01-15 10:09

•1043次阅读

EMC基础-总结

EMC基础-总结

评论