ROHM最近推出了SiC MOSFET的新系列产品“SCT3xxx xR系列”。SCT3xxx xR系列采用最新的沟槽栅极结构,进一步降低了导通电阻;同时通过采用单独设置栅极驱动器用源极引脚的4引脚封装,改善了开关特性,使开关损耗可以降低35%左右。此次,针对SiC MOSFET采用4引脚封装的原因及其效果等议题,我们采访了ROHM株式会社的应用工程师。

-关于SiC MOSFET的SCT3xxx xR系列,除了导通电阻很低,还通过采用4引脚封装使开关损耗降低了35%,对此我们非常感兴趣。此次,想请您以4引脚封装为重点介绍一下该产品。

-首先,请您大致讲一下4引脚封装具体是怎样的封装,采用这种封装的背景和目的是什么。

首先,采用4引脚封装是为了改善SiC MOSFET的开关损耗。包括SiC MOSFET在内的电源开关用MOSFET和IGBT,被作为开关元件广泛应用于各种电源应用和电源线路中。必须尽可能地降低这种开关元件产生的开关损耗和传导损耗,但不同的应用,其降低损耗的方法也不尽相同。作为其中的一种手法,近年来发布了一种4引脚的新型封装,即在MOSFET的源极、漏极、栅极三个引脚之外,另外设置了驱动器源极引脚。此次的SCT3xxx xR系列,旨在通过采用最新的沟槽栅极结构,实现更低的导通电阻和传导损耗;通过采用4引脚封装,进一步发挥出SiC本身具有的高速开关性能,并降低开关损耗。

-那么,我想详细了解一下刚刚您的概述中出现的几个要点。首先,什么是“驱动器源极引脚”?

驱动器源极引脚是应用了开尔文连接原理的源极引脚。开尔文连接是通过电阻测量中的4个引脚或四线检测方式,在电流路径基础上加上两条测量电压的线路,以极力消除微小电阻测量或大电流条件下测量时不可忽略的线缆电阻和接触电阻的影响的方法,是一种广为人知的方法。这种4引脚封装仅限源极,通过使连接栅极驱动电路返回线的源极电压引脚与流过大电流的电源源极引脚独立,来消除ID对栅极驱动电路的影响。

-也就是说基本的思路就是开尔文连接对吧。

是啊!稍后会给您看实际的封装,首先我来介绍一下驱动器源极引脚对降低开关损耗的贡献。

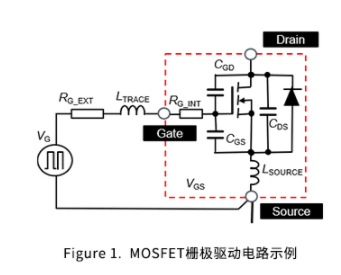

MOSFET通常为电压驱动,通过控制栅极引脚的电压来导通/关断MOSFET。Figure 1为以往的3引脚封装(TO-247N)MOSFET的常规栅极驱动电路示例。红色虚线表示MOSFET封装内部和外部的边界。

通常,在驱动电源VG和MOSFET的栅极引脚之间,会插入用来控制开关速度的外置栅极电阻RG_EXT,而且还包含印刷电路板的布线电感LTRACE。另外,在源极引脚和内部的MOSFET芯片之间,包含封装电感LSOURCE。

在寄生分量中,栅极引脚的封装电感包含在LTRACE中,而漏极引脚的封装电感LDRAIN不包含在栅极驱动电路中,因此在这里省略。

-这就涉及到MOSFET驱动中基本的栅极电阻和寄生分量了吧。

是的。但是,如果是普通IGBT的开关速度的话,可能不会造成很大影响,但在SiC MOSFET的特点之一“高速开关”条件下,开关的漏极-源极间电流ID的转换和LSOURCE引起的电动势VLSOURCE就成了问题。

我们用Figure 2来更具体一点进行说明。Figure 2表示在开关工作中的电路内部电压情况。

当MOSFET被施加VG并导通后,ID急剧增加,LSOURCE产生图中的电动势VLSOURCE(Ⅰ)。

由于电流IG流入栅极引脚,因此RG_EXT产生电压降VRG_EXT(Ⅰ)。

虽然栅极线路的LTRACE也以相同的机制产生电动势,但非常小,影响很小,因此在此省略。

这些电压包含在导通时的驱动电路网中,因此,实际上施加给内部芯片并使MOSFET导通的电压VGS_INT减少了。VGS_INT的减少可以通过公式(1)来表示。

-也就是说,实际上施加给内部芯片的VGS_INT,是从栅极施加电压VG减去外置栅极电阻的电压降和源极引脚寄生电感的电动势之后的电压对吧。

是的。当VGS_INT减少后,MOSFET导通的速度(即开关)就会变慢。

关断时也同样适用公式(1)。但是,由于IG和dID/dt变为负数,因此RG_EXT和LSOURCE产生标记为(Ⅱ)的电压上升,VGS_INT反而增加。增加后使关断速度下降。

-关于您提到RG_EXT和LSOURCE会导致开关速度下降,RG_EXT是外置的栅极电阻,因此只要减小电阻值就可以减少影响了吧?

如您所述,通过减小RG_EXT是可以提高开关速度的。RG_EXT本来是用来调整开关速度的,在这里应该理解如果RG_EXT大于所需的值,就会不必要地降低开关速度,而且开关损耗会增加。

另外,LSOURCE是封装内部的寄生分量,因此无法从外部进行调整。这是非常重要的一点。一般来讲,电源开关元器件的LSOURCE为几nH到十几nH,加上当dID/dt达到几A/ns时可能会产生10V以上的电动势VLSOURCE,这些将对开关工作产生很大的影响。

-前面看到数学公式时我还有些疑问,现在基本理解了。

您可能已经猜到,要想消除这种VLSOURCE的影响,就需要改变封装的结构。我们因此而采用了电源源极和驱动器用源极分开的4引脚封装。

抱歉引言有些长。下面是4引脚封装的示例。目前ROHM已经推出的产品有(a)TO-247-4L和(b)TO-263-7L。

(未完待续)

审核编辑:汤梓红

-

MOSFET

+关注

关注

147文章

7164浏览量

213305 -

封装

+关注

关注

126文章

7901浏览量

142965 -

SiC

+关注

关注

29文章

2814浏览量

62649 -

引脚

+关注

关注

16文章

1196浏览量

50486

发布评论请先 登录

相关推荐

Nexperia全球最小且最薄的14、16、20和24引脚标准逻辑DHXQFN封装

EVAL-ADCMP551BRQ,采用ADCMP551,提供16引脚QSOP封装

ADP5024CP-EVALZ,ADP5024采用24引脚4 mm 4 mm LFCSP封装

ADP5034-1-EVALZ,采用24引脚4 mm 4 mm LFCSP封装

ADP5023CP-EVALZ,采用24引脚4 mm 4 mm LFCSP封装

FAN4810引脚图及其功能

UG-082:双通道高速运算放大器评估板(16引脚、4 mm×4 mm LFCSP封装,带专用反馈引脚)

AD7904/AD7914/AD7924:内置序列器的4通道、1 MSPS、8位模数转换器,采用16引脚TSSOP封装

采用4引脚封装的SiC MOSFET:SCT3xxx xR系列

什么是4引脚PWM接头?4引脚PWM风扇如何工作?

采用4引脚封装的原因

采用4引脚封装的原因

评论