FPGA的用处比我们平时想象的用处更广泛,原因在于其中集成的模块种类更多,而不仅仅是原来的简单逻辑单元(LE)。

1)尽可能采用单一时钟;

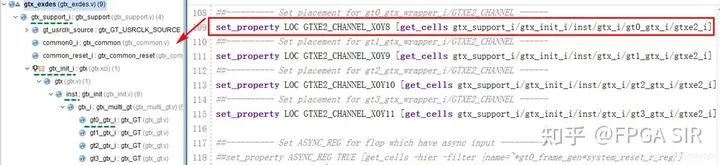

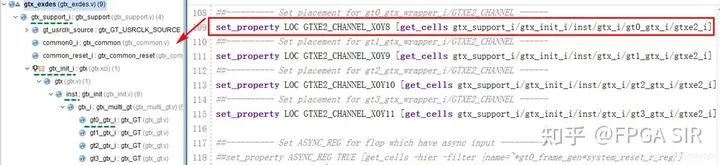

2)如果有多个时钟域,一定要仔细划分,千万小心,同时设置时序约束;

1)尽可能采用单一时钟;

2)如果有多个时钟域,一定要仔细划分,千万小心,同时设置时序约束;

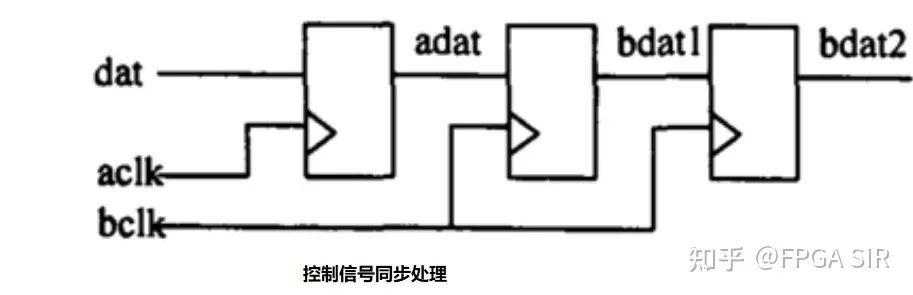

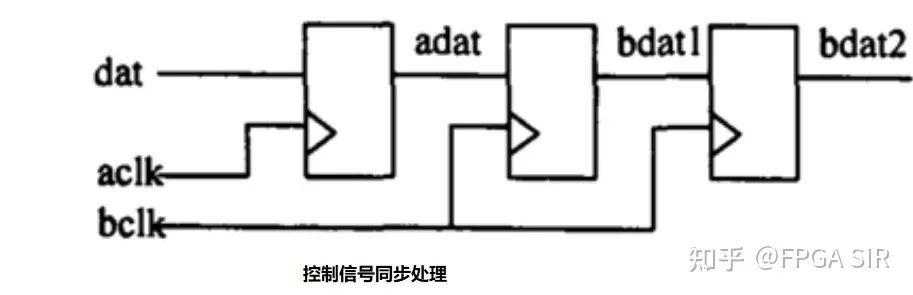

3)跨时钟域的信号一定要做同步处理;

对于控制信号的异步处理是寄存器打两拍缓存;

3)跨时钟域的信号一定要做同步处理;

对于控制信号的异步处理是寄存器打两拍缓存;

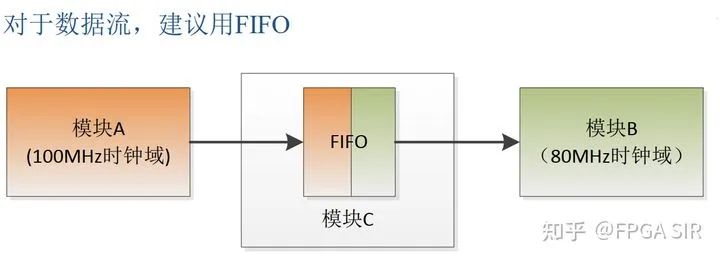

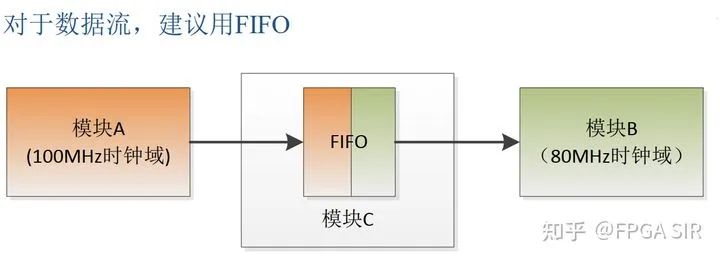

对于数据信号的异步处理是异步fifo缓存,同时注意FIFO两侧的数据流的速率问题;

对于数据信号的异步处理是异步fifo缓存,同时注意FIFO两侧的数据流的速率问题;

4)尽可能将FPGA内部的PLL、DLL利用起来,这会给你的设计带来大量的好处;

5)对于高速的IO接口,需对高速IO设置的delay约束。

4)尽可能将FPGA内部的PLL、DLL利用起来,这会给你的设计带来大量的好处;

5)对于高速的IO接口,需对高速IO设置的delay约束。

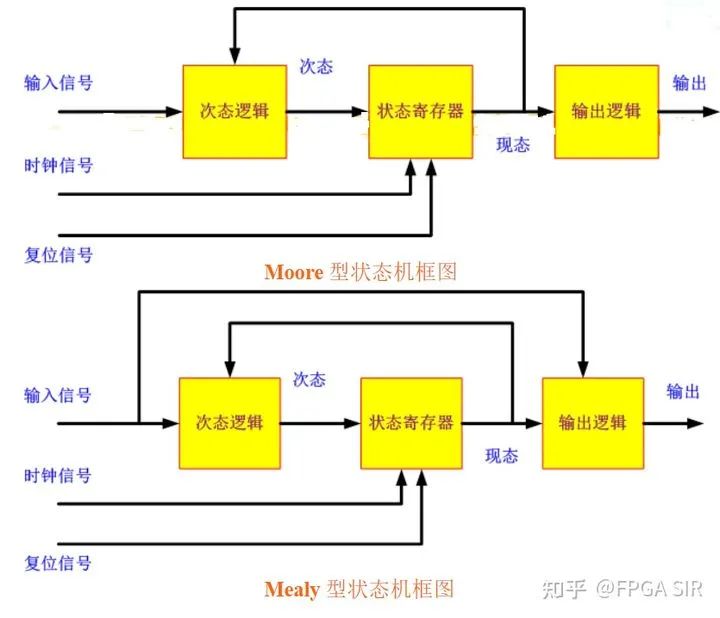

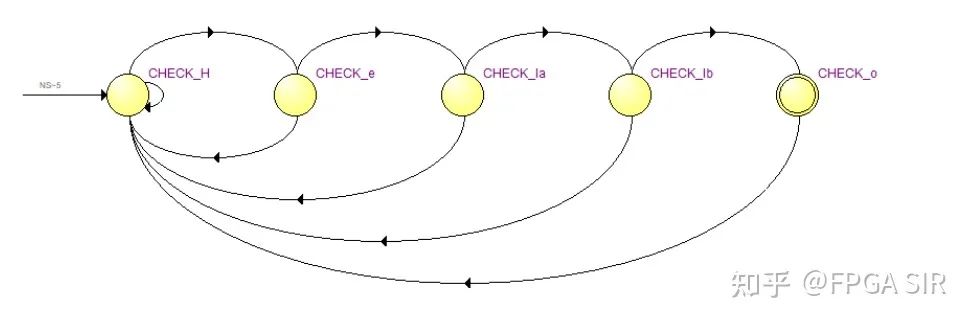

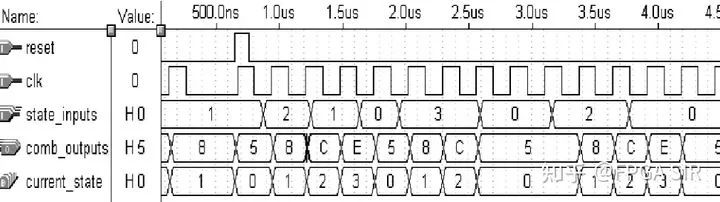

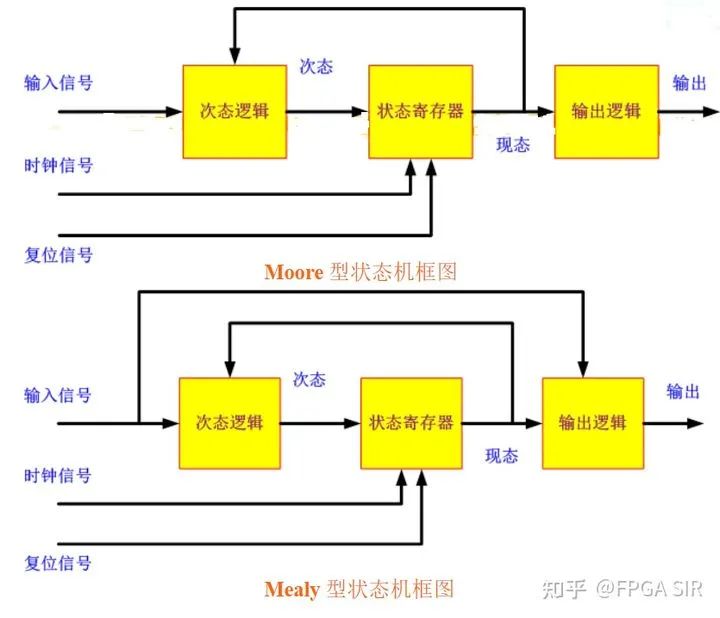

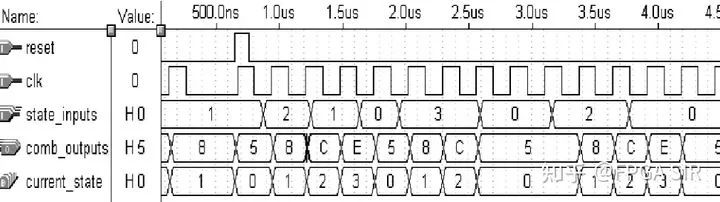

FSM:有限状态机,FPGA最基本的程序设计之一。FSM分为moore型和merly型,moore型的状态迁移和变量无关,merly型则有关。

FSM:有限状态机,FPGA最基本的程序设计之一。FSM分为moore型和merly型,moore型的状态迁移和变量无关,merly型则有关。

实际使用中大部分都采用merly型。

状态机的编码:二进制编码(Binary),格雷码编码(Gray-code),独热码(One-hot)。

实际使用中大部分都采用merly型。

状态机的编码:二进制编码(Binary),格雷码编码(Gray-code),独热码(One-hot)。

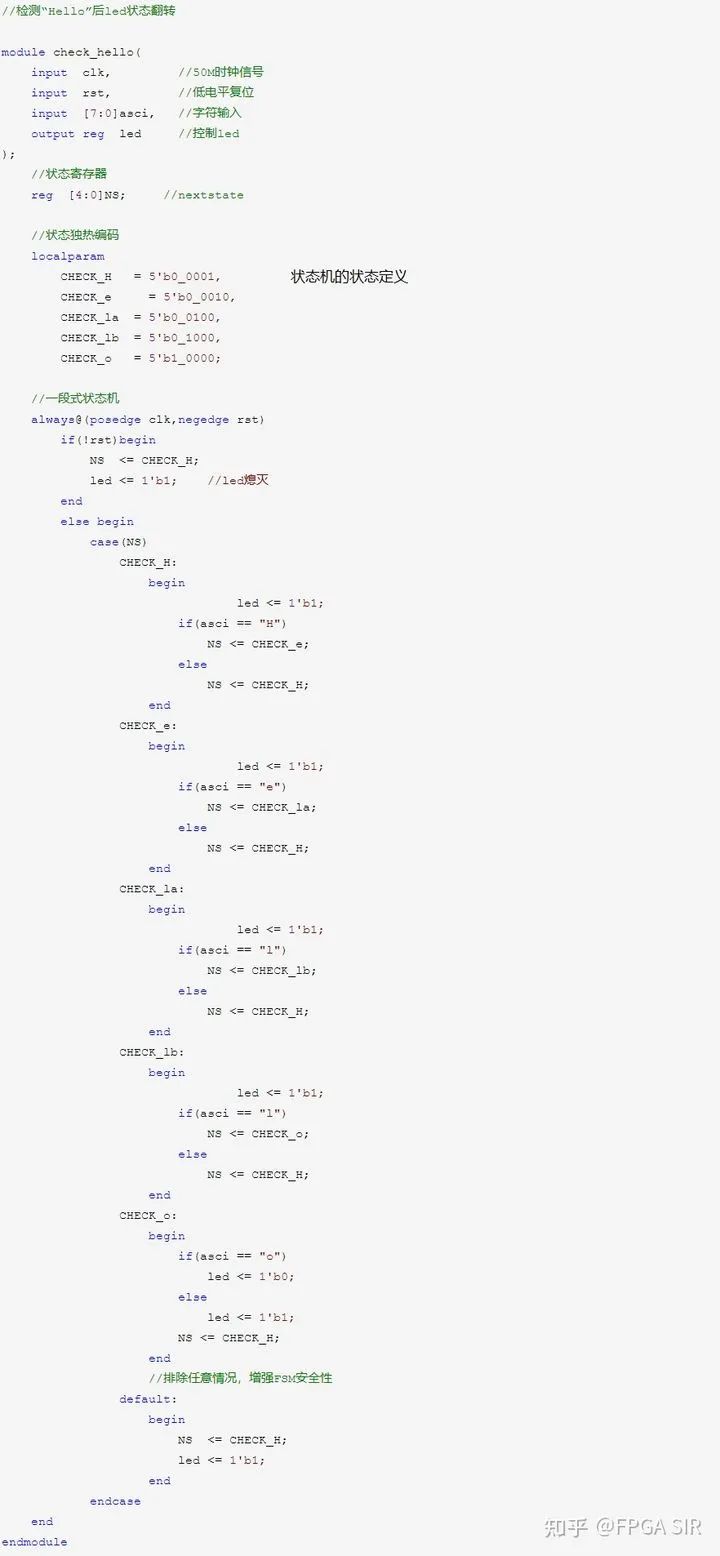

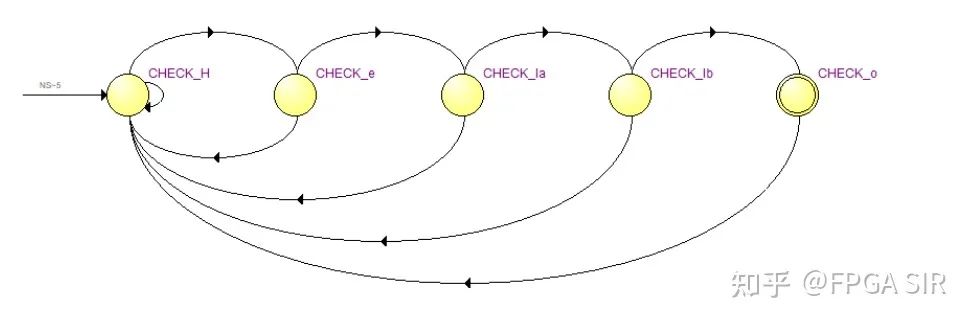

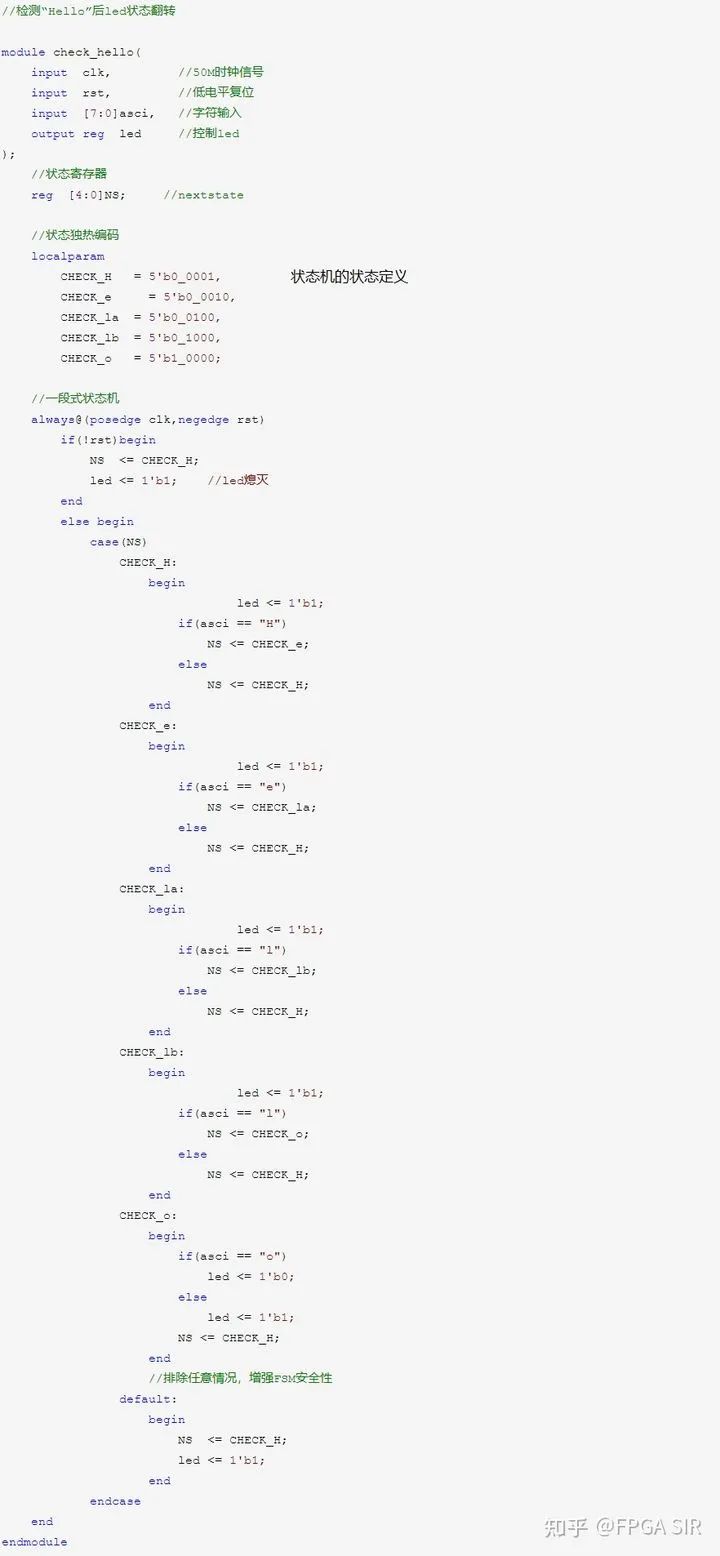

状态机FSM一段式FPGA编码参考。

状态机FSM一段式FPGA编码参考。

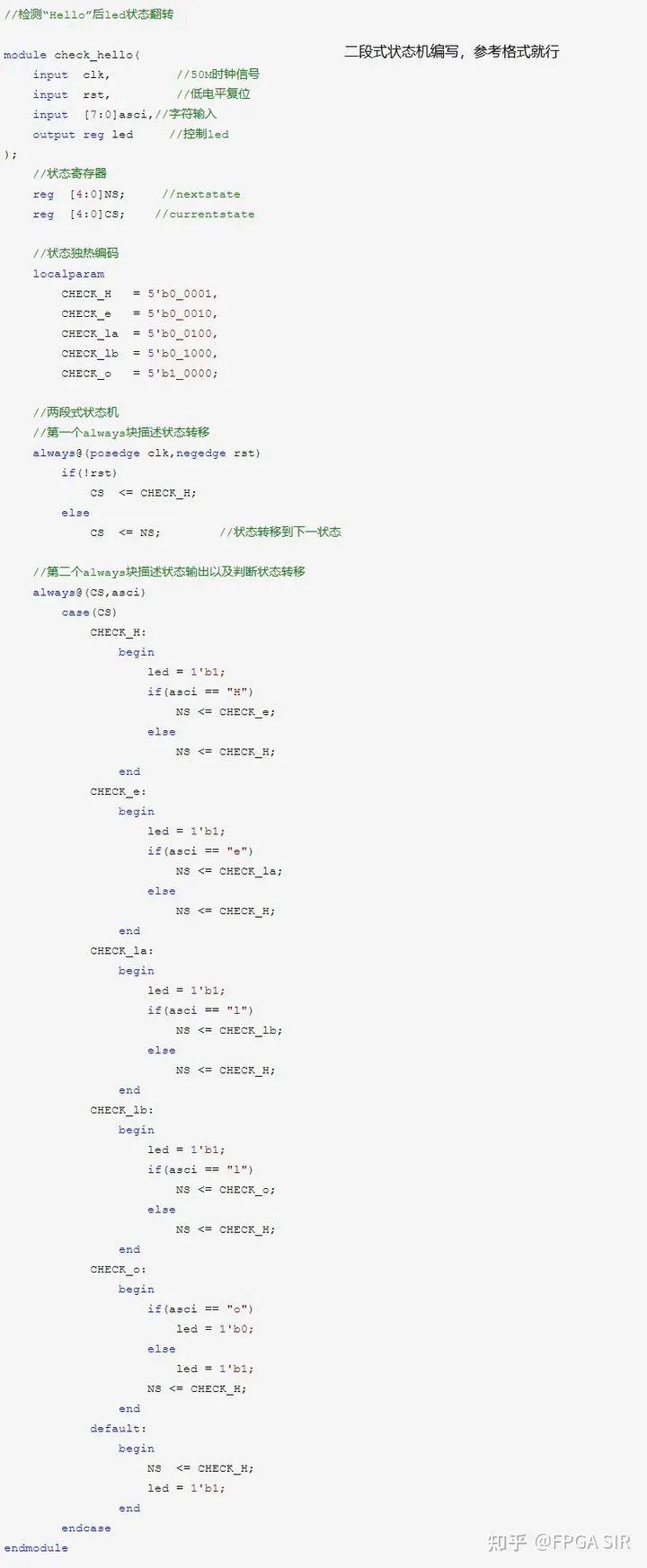

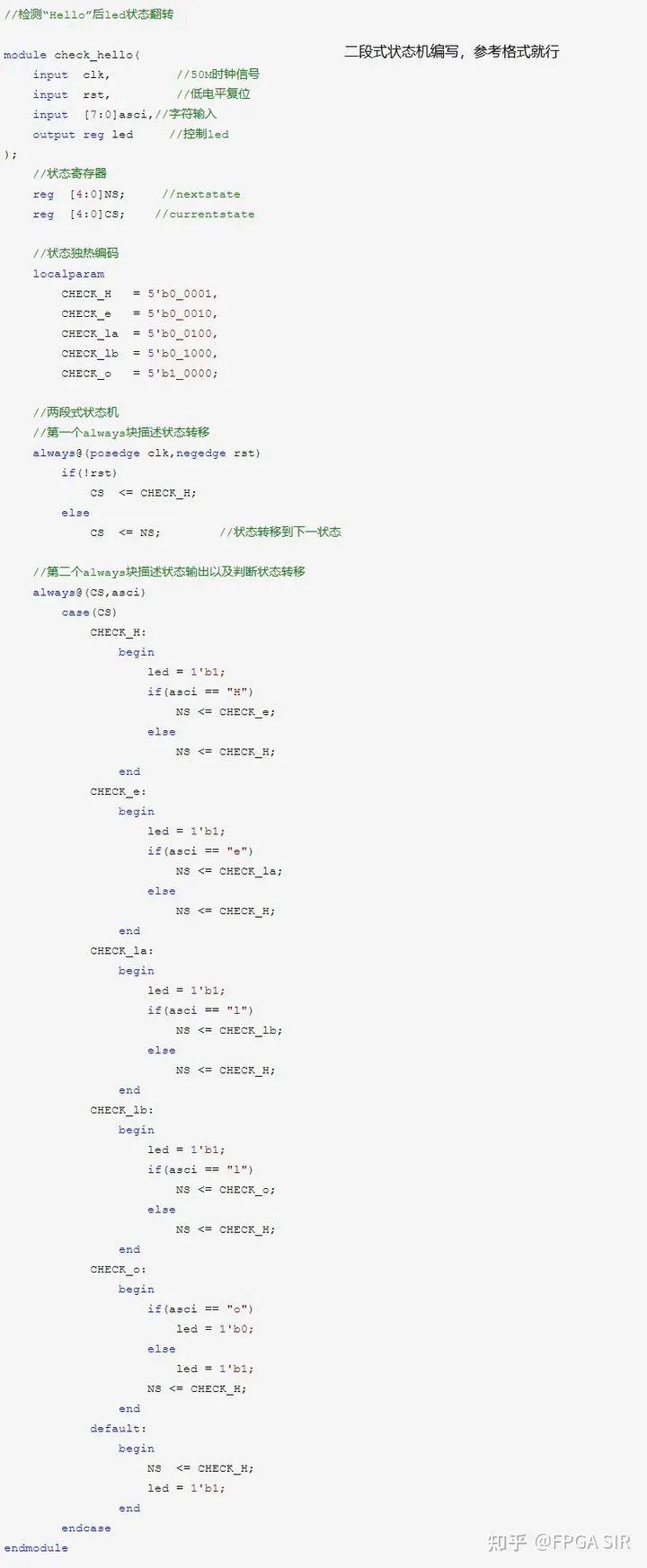

状态机FSM二段式FPGA编码参考。

状态机FSM二段式FPGA编码参考。

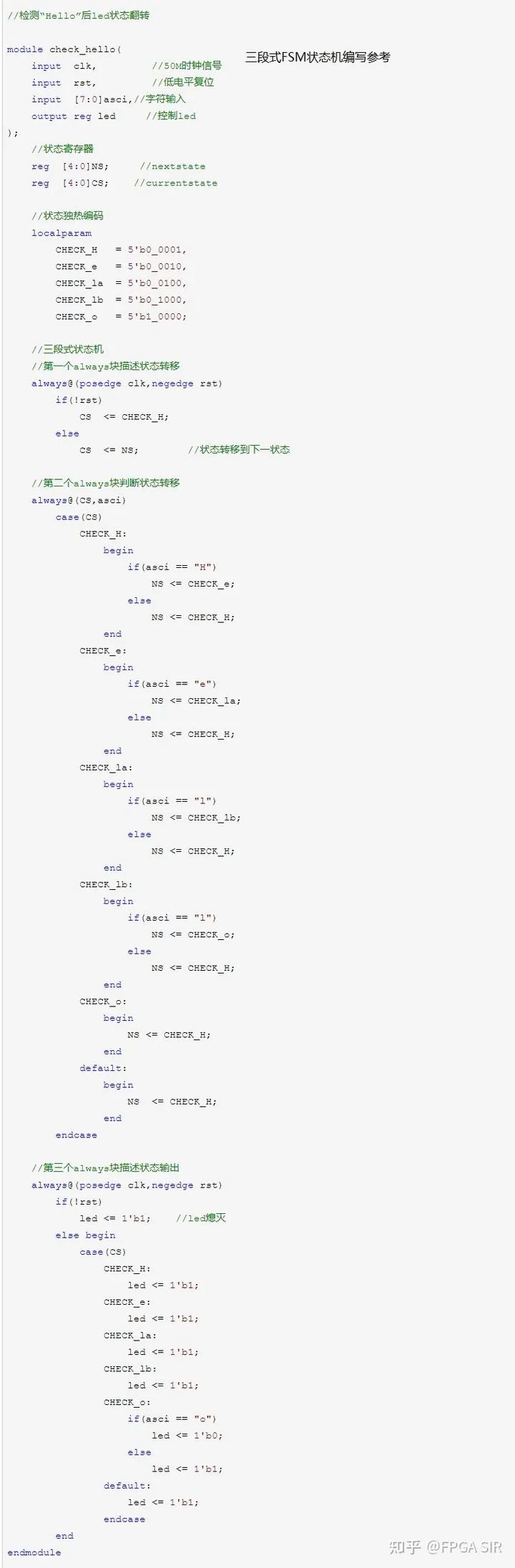

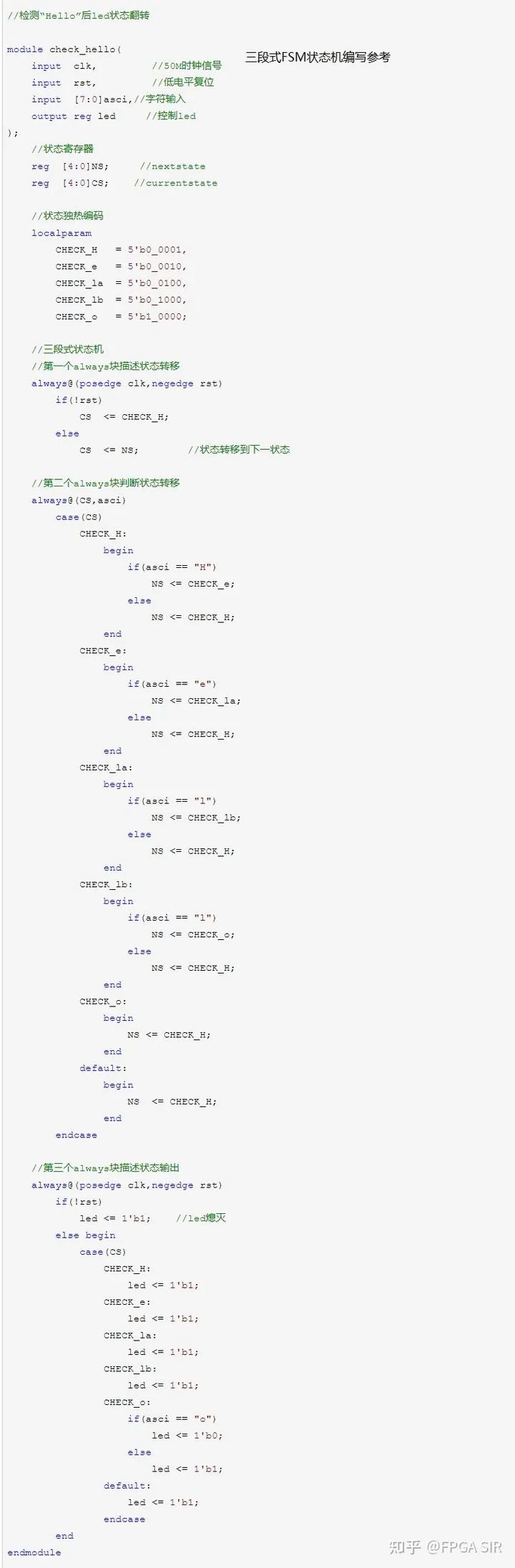

状态机FSM三段式FPGA编码参考。

状态机FSM三段式FPGA编码参考。

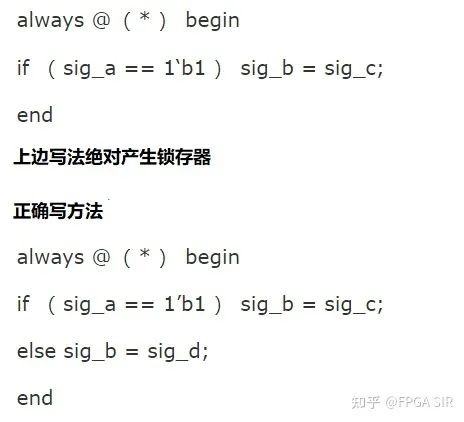

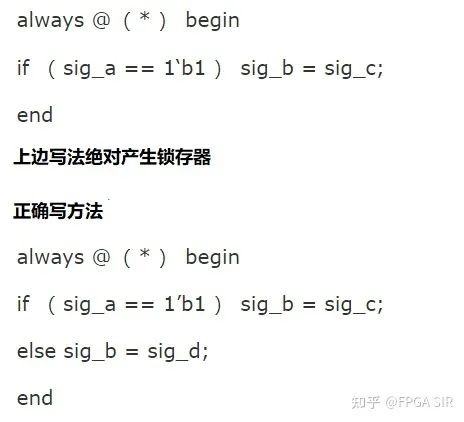

1)在组合逻辑always块中,if语句一定要有else。

2)在组合逻辑always块中,case语句的default一定不能少。

3)组合逻辑进程敏感变量不能少也不能多。

1)在组合逻辑always块中,if语句一定要有else。

2)在组合逻辑always块中,case语句的default一定不能少。

3)组合逻辑进程敏感变量不能少也不能多。

1)模块仿真:针对每一个最小基本模块的仿真;

单元仿真要求代码行覆盖率、条件分支覆盖率、表达式覆盖率必须达到100%,这三种覆盖率都可以通过modelsim来查看,不过需要在编译该模块时要在Compile option中设置好。

1)模块仿真:针对每一个最小基本模块的仿真;

单元仿真要求代码行覆盖率、条件分支覆盖率、表达式覆盖率必须达到100%,这三种覆盖率都可以通过modelsim来查看,不过需要在编译该模块时要在Compile option中设置好。

2)集成仿真:将多个大模块合在一起进行仿真,覆盖率要求尽量高;

3)系统仿真:将整个硬件系统合在一起进行仿真。

此时整个仿真平台包含了逻辑周边芯片接口的仿真模型,以及BFM、Testbench等。系统仿真需要根据被仿真逻辑的功能、性能需求仔细设计仿真测试例和仿真测试平台。

审核编辑 :李倩

2)集成仿真:将多个大模块合在一起进行仿真,覆盖率要求尽量高;

3)系统仿真:将整个硬件系统合在一起进行仿真。

此时整个仿真平台包含了逻辑周边芯片接口的仿真模型,以及BFM、Testbench等。系统仿真需要根据被仿真逻辑的功能、性能需求仔细设计仿真测试例和仿真测试平台。

审核编辑 :李倩

1)尽可能采用单一时钟;

2)如果有多个时钟域,一定要仔细划分,千万小心,同时设置时序约束;

1)尽可能采用单一时钟;

2)如果有多个时钟域,一定要仔细划分,千万小心,同时设置时序约束;

3)跨时钟域的信号一定要做同步处理;

对于控制信号的异步处理是寄存器打两拍缓存;

3)跨时钟域的信号一定要做同步处理;

对于控制信号的异步处理是寄存器打两拍缓存;

对于数据信号的异步处理是异步fifo缓存,同时注意FIFO两侧的数据流的速率问题;

对于数据信号的异步处理是异步fifo缓存,同时注意FIFO两侧的数据流的速率问题;

4)尽可能将FPGA内部的PLL、DLL利用起来,这会给你的设计带来大量的好处;

5)对于高速的IO接口,需对高速IO设置的delay约束。

4)尽可能将FPGA内部的PLL、DLL利用起来,这会给你的设计带来大量的好处;

5)对于高速的IO接口,需对高速IO设置的delay约束。

FSM:有限状态机,FPGA最基本的程序设计之一。FSM分为moore型和merly型,moore型的状态迁移和变量无关,merly型则有关。

FSM:有限状态机,FPGA最基本的程序设计之一。FSM分为moore型和merly型,moore型的状态迁移和变量无关,merly型则有关。

实际使用中大部分都采用merly型。

状态机的编码:二进制编码(Binary),格雷码编码(Gray-code),独热码(One-hot)。

实际使用中大部分都采用merly型。

状态机的编码:二进制编码(Binary),格雷码编码(Gray-code),独热码(One-hot)。

状态机FSM一段式FPGA编码参考。

状态机FSM一段式FPGA编码参考。

状态机FSM二段式FPGA编码参考。

状态机FSM二段式FPGA编码参考。

状态机FSM三段式FPGA编码参考。

状态机FSM三段式FPGA编码参考。

1)在组合逻辑always块中,if语句一定要有else。

2)在组合逻辑always块中,case语句的default一定不能少。

3)组合逻辑进程敏感变量不能少也不能多。

1)在组合逻辑always块中,if语句一定要有else。

2)在组合逻辑always块中,case语句的default一定不能少。

3)组合逻辑进程敏感变量不能少也不能多。

1)模块仿真:针对每一个最小基本模块的仿真;

单元仿真要求代码行覆盖率、条件分支覆盖率、表达式覆盖率必须达到100%,这三种覆盖率都可以通过modelsim来查看,不过需要在编译该模块时要在Compile option中设置好。

1)模块仿真:针对每一个最小基本模块的仿真;

单元仿真要求代码行覆盖率、条件分支覆盖率、表达式覆盖率必须达到100%,这三种覆盖率都可以通过modelsim来查看,不过需要在编译该模块时要在Compile option中设置好。

2)集成仿真:将多个大模块合在一起进行仿真,覆盖率要求尽量高;

3)系统仿真:将整个硬件系统合在一起进行仿真。

此时整个仿真平台包含了逻辑周边芯片接口的仿真模型,以及BFM、Testbench等。系统仿真需要根据被仿真逻辑的功能、性能需求仔细设计仿真测试例和仿真测试平台。

审核编辑 :李倩

2)集成仿真:将多个大模块合在一起进行仿真,覆盖率要求尽量高;

3)系统仿真:将整个硬件系统合在一起进行仿真。

此时整个仿真平台包含了逻辑周边芯片接口的仿真模型,以及BFM、Testbench等。系统仿真需要根据被仿真逻辑的功能、性能需求仔细设计仿真测试例和仿真测试平台。

审核编辑 :李倩

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

FPGA

+关注

关注

1629文章

21735浏览量

603187 -

仿真

+关注

关注

50文章

4080浏览量

133584 -

数据信号

+关注

关注

0文章

58浏览量

11971

原文标题:FPGA常见的基本设计要点

文章出处:【微信号:FPGA研究院,微信公众号:FPGA研究院】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

FPGA设计验证关键要点

FPGA设计验证关键要点不同于ASIC设计,FPGA设计中的标准元件或客制化实作,一般欠缺大量的资源及准备措施可用于设计验证。由于可以重新程式化元件,更多时候验证只是事后的想法。本文将探讨在F

发表于 05-21 20:32

Protel99SE要点、经验及常见问题

Protel99SE要点、经验及常见问题:PCB emi设计要点PCB LAYOUT技术大全PCB精品技术技巧PCB设计常见问题PCB设计流程(新手必读)Protel 99se快捷键大

发表于 09-13 15:13

•0次下载

Virtex5 FPGA在ISE + Planahead上部分可重构功能的流程和技术要点

部分可重构技术是Xilinx FPGA的一项重要开发流程。本文结合Virtex5 FPGA,详细讲解在ISE + Planahead上完成部分可重构功能的流程和技术要点。

FPGA视频教程之FPGA设计中时序逻辑设计要点的详细资料说明

本文档的主要内容详细介绍的是FPGA视频教程之FPGA设计中时序逻辑设计要点的详细资料说明免费下载。

发表于 03-27 10:56

•20次下载

常见的fpga芯片有哪些

FPGA(现场可编程门阵列)芯片是一种可编程逻辑器件,其内部包含了大量的可编程逻辑单元和连接关系,可以通过编程来实现不同的逻辑功能。目前市面上有许多常见的FPGA芯片,这些芯片各自具有不同的规格、性能和特点,适用于不同的应用场景

FPGA常见的基本设计要点

FPGA常见的基本设计要点

评论