“过去我们往往只关注晶体管的大小,但随着芯片微缩逐渐逼近极限,芯片的互连问题已经难以被忽略。自从IBM在20世纪90年代将铜互连引入双大马士革工艺以来,半导体行业一直在利用铜的高导电性、低电阻率和可靠互连的优势,但随着技术节点不断迭代,铜互连面临着电迁移寿命差、无法消除衬垫等问题。在转向新材料的同时,业界也在向铜互连技术寻求更具成本优势的解决方案。本文介绍了一些提高铜互连优势的方法,以及突破铜互连的机遇,比如引入减法刻蚀等。

自动翻译:

随着领先的芯片制造商继续扩大fin FET——很快纳米片晶体管——到越来越紧的间距,最小的金属线最终将无法使用铜及其衬垫和势垒金属。接下来会发生什么,什么时候发生,还有待确定。有多种选择正在探索,每个都有自己的一套权衡。

自从IBM在20世纪90年代将大马士革工艺引入铜互连以来,半导体行业一直在利用铜的高导电性、低电阻率和可靠的互连。但随着电阻和电容的增加,RC延迟将继续显著影响器件的性能。

铜的替代品,如钌和钼,可以集成使用双镶嵌。不过,它们可能更适合使用金属蚀刻的减法方案,自从铝互连的日子以来,金属蚀刻还没有在逻辑中广泛使用。尽管如此,领先的设备制造商和设备公司都在寻求几种有趣的途径来获得这些最低水平的铜。与此同时,工程师和研究团队正在进一步扩展铜线,这是迄今为止更实惠、更有吸引力的路线。

“在过去的25年里,双大马士革一直是,现在仍然是互联网的支柱。但是我们看到,由于RC延迟原因,金属图案化可能变得相关,”imec研究员、纳米互连项目主任Zsolt Tokei说。Imec的计划被称为半镶嵌工艺,由于向减法工艺的过渡将是戏剧性的,它可能会逐步引入。“我们认为,最初它将用于一个层,但后来这将传播到几个层。这与自对准过孔相结合,也许还可以改变线的中间位置。”

与此同时,如果可能的话,系统性能驱动程序使得将内存设备移动到生产线的后端成为一种吸引力。如果业界开始引入具有较低热预算的互连工艺,存储器或其他设备集成等将变得可行。但首先,必须解决当前的工程挑战,扩大铜和引入背面配电方案。

更多的里程从铜

在2nm逻辑节点,铜线和过孔通过创造性的手段被扩展。一些最有吸引力的选项涉及限制阻挡层和衬里材料的电阻率影响,要么通过使这些薄膜更薄——从化学气相沉积(CVD)到原子层沉积(ALD)——或消除它们,例如,沿着通孔和线路之间的垂直路径。

TEL和Applied Materials都提供使用自组装单层膜(SAMs)实现选择性沉积的集成工艺。这些SAM使用CVD或旋涂薄膜,选择性地沉积在金属上,而不是电介质上,以便钴或钌衬里,或势垒,如ALD Ta/TaN,粘附到所需的表面。

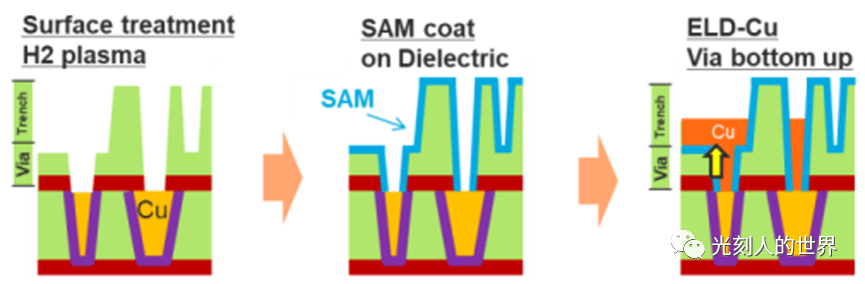

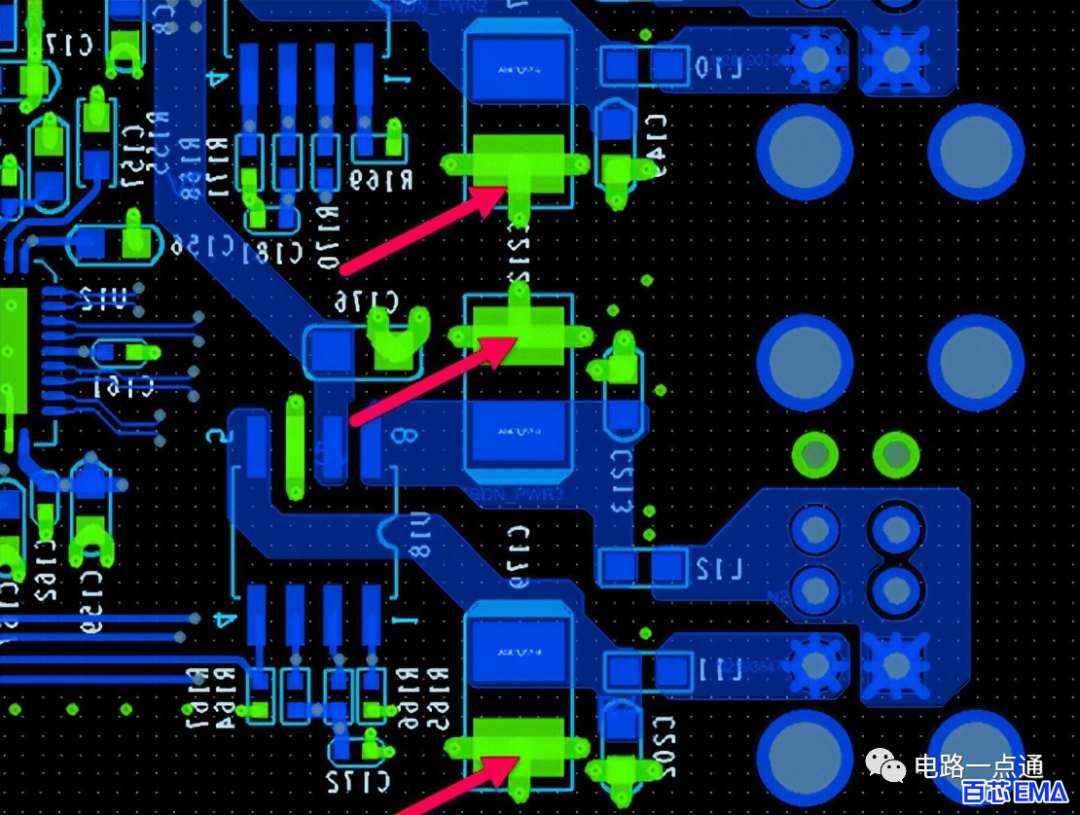

在IITC的一次演讲中,TEL公司研发部门和JSR Micro的Yuki Kikuchi和同事们展示了与使用JSR的SAM抑制ALD TaN相关的电阻和铜体积的改善,甚至取代了铜阻挡金属。[1]通过在通孔底部使用一种SAM(SAM_B),然后在低k上使用另一种材料(SAM_F),实现了对低k介质(2.5)的最佳选择性(见图1)。该工序可以完全消除通孔侧壁上的钌XXX?

图1:氢预处理后,自组装单分子层(SAM)在化学沉积预通孔填充过程中起屏障作用.资料来源:IITC 2022。

有趣的是,研究人员测试了预通孔填充工艺,其中在铜填充物下使用阻挡层(TaN),而是在化学沉积(ELD)后沉积。设备制造商正在对预填充过孔进行更广泛的测试,以降低电阻率,确保可靠性,并延长铜流的生产率。

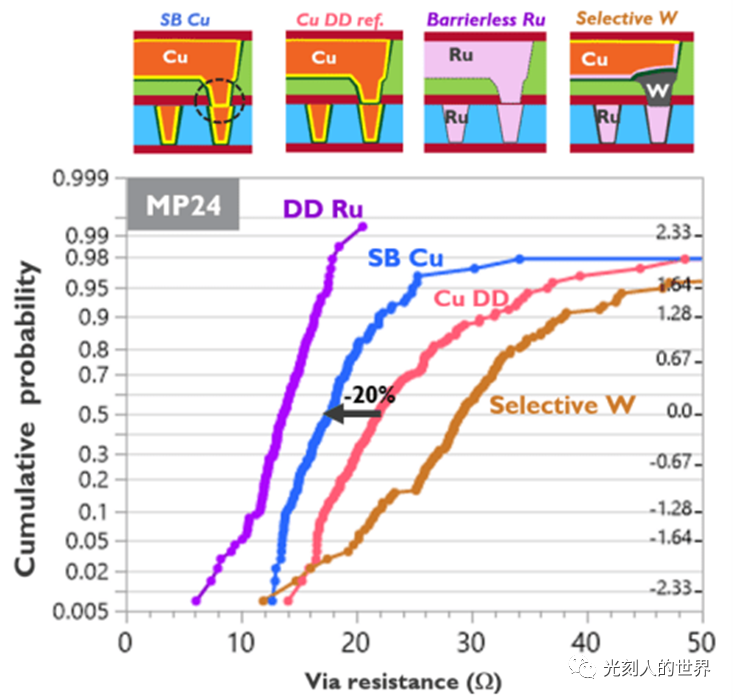

微小的过孔是互连链中最薄弱的环节。Imec和Applied Materials比较了钌、钨和铜的过孔,以了解相对于使用钨或钌的24nm过孔,通过消除铜中的底部Ta势垒实现了哪些电阻收益。(见图二)。[2]imec互连金属化专家Marleen van der Veen表示:“关键的工艺步骤是在对通孔底部的裸露铜进行原位界面工程之后,仅在电介质上进行选择性ALD TaN势垒沉积。”该团队确定,通过消除屏障,通孔电阻降低了20%。在更小的尺寸,减少会更大。

图二:单通孔电阻比较双镶嵌铜参考选择性势垒铜,无势垒双镶嵌钌和钨/铜混合显示消除在过孔底部的势垒20%的好处。资料来源:2022年印度国际贸易理事会

拐点:引入减蚀

在2nm节点之后的某个时间,该行业可能会从双金属镶嵌转变为一种形式的减法金属化。这是一个巨大的变化,不能掉以轻心。

Imec的减法金属化版本被称为半镶嵌,因为它从沟槽的介电蚀刻开始,类似于双镶嵌。“这是非常大的一步,因为这是一个新的模块,它有风险,”imec的Tokei说。“然后,长宽比可以逐渐增加,并且在某个点可以加入空气间隙。” 该工艺使用介电化学机械抛光步骤,这是类似于在浅沟槽隔离(SunTrust Banks)步骤进行的介电化学机械抛光。

最有可能的是,Tokei预计将用钌进行四代左右的半镶嵌加工。在此之后,二元或三次金属合金可能会发挥作用。他说:“根据电阻率和其他一些因素,我们已经确定了几个优秀的人选,但这是非常早期的研发工作。”“我们有大约六年的时间来真正把它缩小到最好的候选人身上。”

在半镶嵌,过孔的图案首先在介电堆栈,其次是钌沉积,这over fill的功能。然后,该金属层被掩模和蚀刻以形成垂直于通孔的线层。在金属图案化之后,线可以用电介质填充或用于在局部层处形成部分气隙。根据I MEC模拟,此工艺具有与双镶嵌工艺相当的成本。

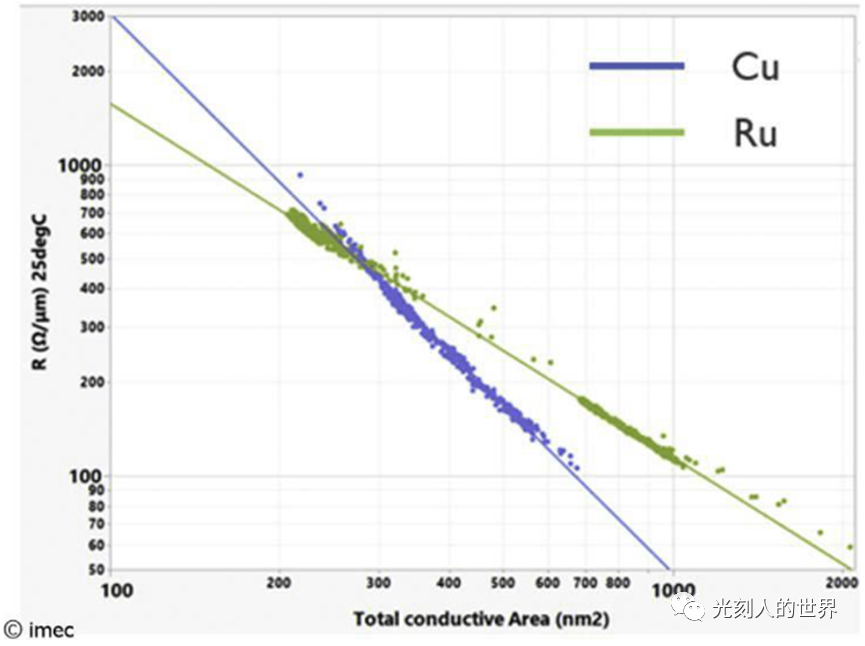

那么铜互连的规模有多大呢?在与钌的直接比较中,最近的一项研究确定了从铜到钌在电阻率方面的交叉点为略低于300nm2,约17 x 17nm。(见图三)。

有不同的制造空气间隙的方法,包括部分间隙填充或使用牺牲材料。然而,Tokei指出,在相同尺寸的特征上,在硅片上实现一致的气隙深度是一个行业挑战。他强调,气隙的形成不应需要额外的掩模层,而应作为加工的一部分形成。此外,必须特别注意散热,因为空气是劣质导体。

图三:钌的电阻率低于铜的电阻率,低于300nm2。资料来源:VLSI 2022

过渡到减法金属化有根本的优势,包括没有由于CMP和蚀刻造成的介电损伤,能够达到更高的纵横比线(降低电阻),以及潜在的更简单的工艺。然而,更多的负担被放置在蚀刻工艺,特别是当CD移动到10纳米金属间距。

Lam Research和imec探索了一些与氧基钌蚀刻化学品相关的挑战。[3]通常,钌是通过溅射(物理气相沉积,或PVD)沉积,然后退火约400°C,以达到最低的电阻率。在Si3N4/TiN硬掩模(心轴)中的间隔物图案用于形成紧密的尺寸,从中蚀刻大于3纵横比钌线。一个关键的挑战涉及硬掩模侧壁上的氧化层的生长,这显着缩小沟槽。先进的清洗步骤和原位等离子清洗,以消除残留物和限制TiN咬边。

用于在Cl2/O2中进行钼蚀刻,Lam和imec确定的主要问题是侧壁钝化和金属氧化不足。该团队能够通过在部分钼蚀刻后沉积薄氧化物来解决这一问题,他们指出,由于金属的氧化潜力,封装可能是必要的。

imec的Tokei说:“根据数据,我们在钌上取得的进展要比在钼上取得的进展要大。”“与钼的关注之一是氧化,这使得它更适合于一种镶嵌类型的方法。这是非常有趣的中间线,它是一种廉价的金属。”

过程建模在帮助建立设计规则、评估过程窗口和斜坡产量方面起着关键作用。“虚拟制造是对工艺和工艺流程的一步一步的行为描述,与关键的设计信息相结合,以创建硅片中发生的事情的硅精确三维模型,”Lam负责计算产品的副总裁戴维·弗里德(David Fried)说。

例如,来自Lam的Coventor部门的SEMulator 3D平台被用来评估imec的半镶嵌流与工艺助推器如何影响14nm和16nm(1.5nm节点)的金属间距的新掩膜集上的RC性能。[4]性能助推器,包括完全自对准图案,高AR金属线,和空气间隙进行了建模和确认。在其他研究结果中,模拟器比较了不同的过孔自对准方法,以确定哪种方法在10nm和7nm节点上实现了最宽的覆盖公差。

“因为这些模型必须是硅精确的,我们花了大量的时间在校准技术上,”Fried说。“在我们的基准流程模型中,我们使用机器学习技术对流程模型进行多变量非线性优化,从而创建该流程的可视化表示。当它校准到过程空间中的多个点时,它就可以预测过程窗口的其余部分。”

绑在背后的力量

背面功率传递(BPD)是一种创新的方法,从晶片背面向晶体管输送功率,使前端互连线只传送信号。这缓解了拥塞,领先的芯片制造商将在2NM节点上实现它。LAM Research高级工程总监汤姆·蒙齐尔(Tom Mountsier)表示:“利用晶片背面进行配电,有效地增加了模具的功能区,而不增加其足迹。”

“背面电源集成的最大挑战之一是在连接芯片的正面和背面的电气。这就是TSV的作用”他指出,芯片制造商正在评估不同的集成方案。所有的选择涉及蚀刻和金属填充。

最具挑战性的方案涉及直接背面接触源epi。他说:“市场前景将是小而高的纵横比。”他说:“你也需要与epi进行低电阻接触,就像前端的源/排水接触一样。”因此,钨填充,或可能的钼,将是可能的选择。实施将需要时间,因为需要大量的集成挑战,例如将背面接触对准前端epi,以及在降低温度(400°C或更低)时使金属与epi之间进行欧姆接触。“

Lam的高级半导体工艺工程师Assawer Soussou总结道:“背面供电以工艺复杂性为代价实现了技术优势。”

电力输送也已成为一个热门话题,在包装方面的业务。“最近,人们对光子学很感兴趣,尤其是共同封装的光学,”日月光销售与市场高级副总裁尹昌说。“这极大地增加了数据传输的带宽。很多公司都达到了他们可以通过基板携带多少带宽的限制,如果你不能满足这些要求,那么光子学真的是唯一的选择。所以基板真的变成了一个能量输送系统。”

结论

今天,双大马士革铜互联被伸到20纳米间距,但是一种与钌或其他替代金属有关的减法方案的根本改变即将到来。在电阻率方面,钌变得有吸引力,因为它的特征下降到17×17nm以下,这是领先的器件制造商正在接近的。公司可以利用无障碍通过底部获得额外的收益,同时为一个伟大的过渡做准备。

审核编辑 :李倩

-

芯片

+关注

关注

455文章

50732浏览量

423249 -

存储器

+关注

关注

38文章

7484浏览量

163770 -

晶体管

+关注

关注

77文章

9684浏览量

138092

原文标题:铜互连

文章出处:【微信号:半导体设备与材料,微信公众号:半导体设备与材料】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

新型铜互连方法—电化学机械抛光技术研究进展

关于如何提高SRAM存储器的新方法

PCB的覆铜技巧和方法有哪些

铝/铜互连工艺与双镶嵌法(AL/Cu Interconnect and Dual Damascenes)

铜互连,还能撑多久?

新型铜芯电缆的优势大吗

什么是铜互连?为什么铜互连非要用双大马士革工艺?

提高铜互连优势的方法

提高铜互连优势的方法

评论