always @ (posedge inputs)

begin

...

end

因为这个时钟inputs很有问题。如果begin ... end语句段涉及到多个D触发器,你无法保证这些触发器时钟输入的跳变沿到达的时刻处于同一时刻(准确的说是相差在一个很小的可接受的范围)。因此,如果写出这样的语句,EDA工具多半会报clock skew > data delay,造成建立/保持时间的冲突。本人曾经也写出过这样的语句,当时是为了做分频,受大二学的数字电路的影响,直接拿计数器的输出做了后面模块的时钟。当初用的开发工具是max+plusII,编译也通过了,烧到板子上跑倒也能跑起来(估计是因为时钟频率较低, 6M ),但后来拿到QuartusII中编译就报clock skew > data delay。大家可能会说分频电路很常见的啊,分频输出该怎么用呢。我一直用的方法是采用边沿检测电路,用HDL语言描述大概是这样:always @ (posedge Clk)

begin

inputs_reg <= inputs;

if (inputs_reg == 1'b0 && inputs == 1'b1)

begin

...

end

...

end

这是上跳沿检测的电路,下跳沿电路大家依此类推。 2.异步时钟域信号的处理 这个问题也得分单一信号和总线信号来讨论 2.1单一信号(如控制信号)的处理 如果这个输入信号来自异步时钟域(比如FPGA芯片外部的输入),一般采用同步器进行同步。最基本的结构是两个紧密相连的触发器,第一拍将输入信号同步化,同步化后的输出可能带来建立/保持时间的冲突,产生亚稳态。需要再寄存一拍,减少(注意是减少)亚稳态带来的影响。这种最基本的结构叫做电平同步器。 如果我们需要用跳变沿而不是电平又该怎样处理呢,还记得1里面讲的边沿检测电路么?在电平同步器之后再加一级触发器,用第二级触发器的输出和第三级触发器的输出来进行操作。这种结构叫做边沿同步器。

always @ (posedge Clk)

begin

inputs_reg1 <= inputs;

inputs_reg2 <= inputs_reg1;

inputs_reg3 <= inputs_reg2;

if (inputs_reg2 == 1'b1 && inputs_reg3 == 1'b0)

begin

...

end

...

end

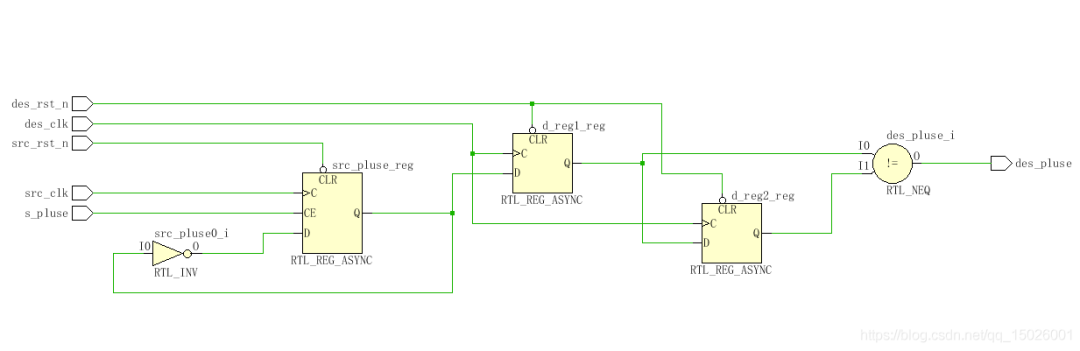

以上两种同步器在慢时钟域信号同步入快时钟域时工作的很好,但是反过来的话,可能就工作不正常了。举一个很简单的例子,如果被同步的信号脉冲只有一个快时钟周期宽,且位于慢时钟的两个相邻跳变沿之间,那么是采不到的。这时就需要采用脉冲同步器。这种同步器也是由3个触发器组成。 脉冲同步器 由于脉冲在快时钟域传递到慢时钟域时,慢时钟有时无法采样的信号奈奎是特采样定理,因此需要对信号进行处理,可以让慢信号采样到。脉冲同步器的结果如图: 2.2总线信号的处理

如果简单的对异步时钟域过来的一组信号分别用同步器的话,那么对这一组信号整体而言,亚稳态出现的几率将大大上升。基于这一观点,对于总线信号的处理可以有两种方式。

如果这组信号只是顺序变化的话(如存储器的地址),可以将其转换为格雷码后再发送,由于格雷码相邻码字只相差一个比特,上面说的同步器可以很好的发挥作用

但是如果信号的变化是随机的(如存储器的数据),这种方法便失效了,这时可以采用握手的方式或者采用FIFO或DPRAM进行缓存。RAM缓存的方式在突发数据传输中优势比较明显,现在高档一点的FPGA中都有不少的BlockRAM资源,且支持配置为DPRAM或FIFO,这种处理方法在通信电路中非常常用。

2.2总线信号的处理

如果简单的对异步时钟域过来的一组信号分别用同步器的话,那么对这一组信号整体而言,亚稳态出现的几率将大大上升。基于这一观点,对于总线信号的处理可以有两种方式。

如果这组信号只是顺序变化的话(如存储器的地址),可以将其转换为格雷码后再发送,由于格雷码相邻码字只相差一个比特,上面说的同步器可以很好的发挥作用

但是如果信号的变化是随机的(如存储器的数据),这种方法便失效了,这时可以采用握手的方式或者采用FIFO或DPRAM进行缓存。RAM缓存的方式在突发数据传输中优势比较明显,现在高档一点的FPGA中都有不少的BlockRAM资源,且支持配置为DPRAM或FIFO,这种处理方法在通信电路中非常常用。

精彩推荐 至芯科技12年不忘初心、再度起航2月11日北京中心FPGA工程师就业班开课、线上线下多维教学、欢迎咨询! 基于FPGA的千兆以太网ARP和UDP的实现 FPGA学习-基于FPGA的图像处理扫码加微信邀请您加入FPGA学习交流群

欢迎加入至芯科技FPGA微信学习交流群,这里有一群优秀的FPGA工程师、学生、老师、这里FPGA技术交流学习氛围浓厚、相互分享、相互帮助、叫上小伙伴一起加入吧!

点个在看你最好看

原文标题:FPGA同步转换FPGA对输入信号的处理

文章出处:【微信公众号:FPGA设计论坛】欢迎添加关注!文章转载请注明出处。

-

FPGA

+关注

关注

1625文章

21663浏览量

601670

原文标题:FPGA同步转换FPGA对输入信号的处理

文章出处:【微信号:gh_9d70b445f494,微信公众号:FPGA设计论坛】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

FPGA同步转换FPGA对输入信号的处理

FPGA同步转换FPGA对输入信号的处理

评论