RX内核的特性

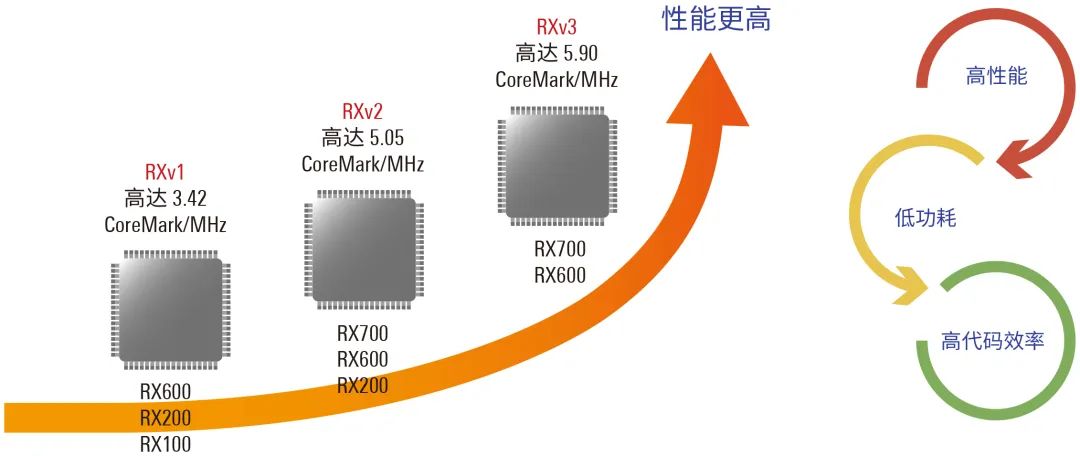

RX内核发展路线

增加附加值和系统复杂性的需求要求单片机具有更高的性能。同时,还要满足节能和延长电池寿命的需求,因此功耗也要降低。RX内核不断改进来满足这些需求。

RX产品家族特性:

https://www.renesas.com/products/microcontrollers-microprocessors/rx-32-bit-performance-efficiency-mcus/rx-features

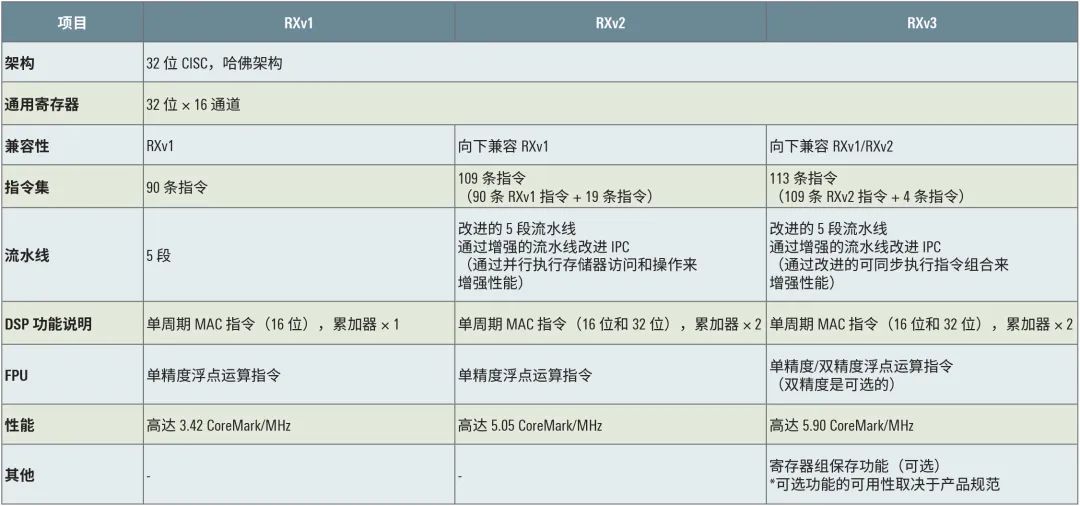

◆ RX内核比较

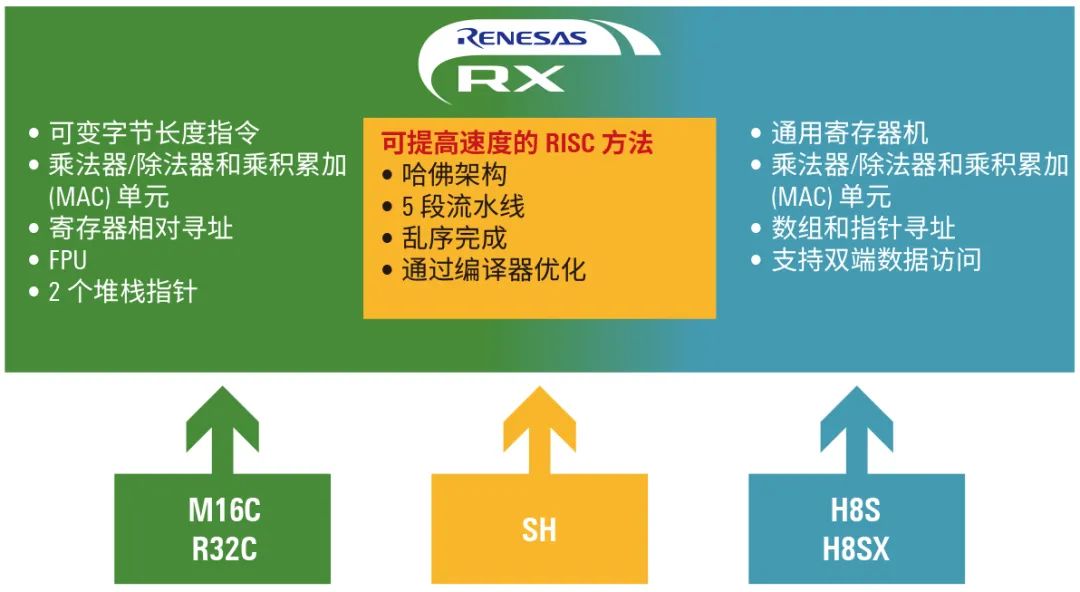

特性1:延续前代产品优势的独创CPU

RX内核兼具CISC和RISC的优势

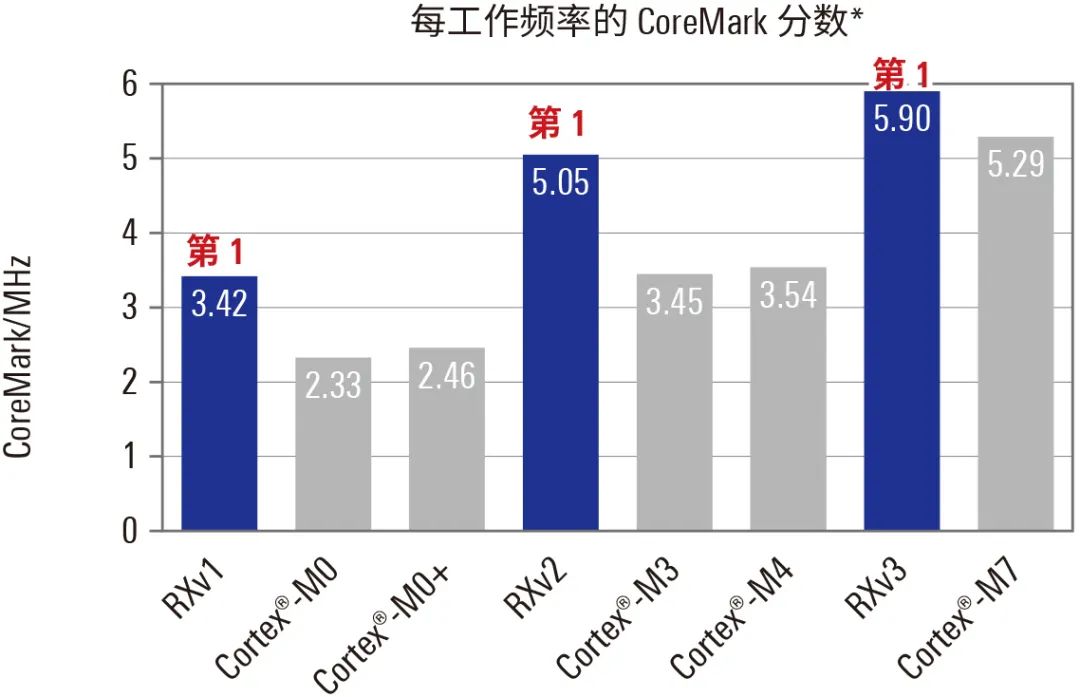

特性2:RX CPU内核具有业界领先的性能

* Cortex-M是Arm的标称值

CoreMark/MHz值 = 5.90

RX内核的特性

-

内部开发的CPU,可实现高效运行。

-

五段超标量架构。

-

针对电源效率和高性能进行了优化。

-

处理能力和代码效率与RISC相当。

-

改进了中断响应和FPU/DSP指令。

特性3:流水线级配置

-

哈佛架构支持并行执行取指令和数据访问。

-

五段流水线配置和乱序完成,执行速度更快。(如果后面的指令与前面的指令之间没有依赖关系,则允许不等待而直接执行后面的指令。)

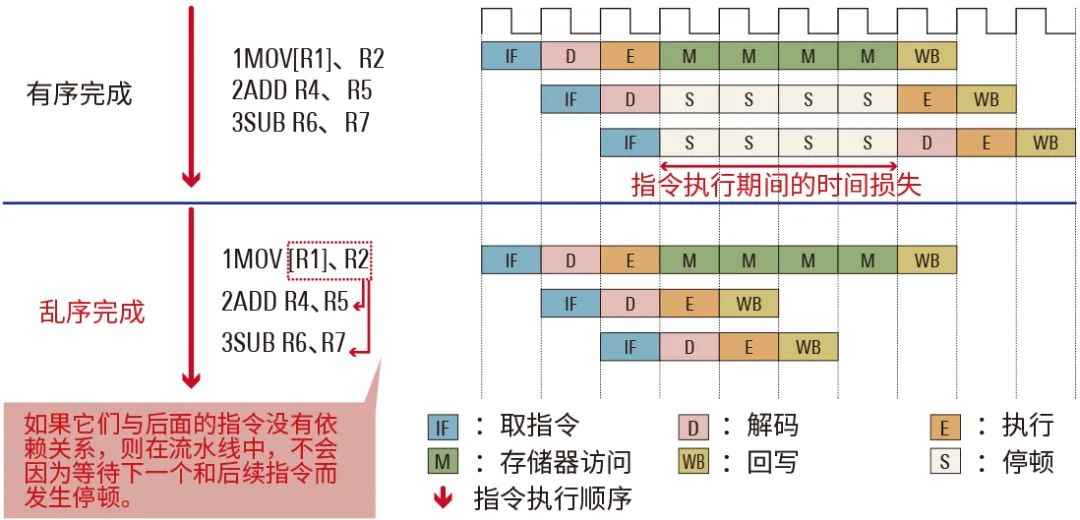

◆ 流水线级配置

-

5级流水线,处理速度更快。

-

通过对各类应用软件进行基准测试,处理性能较早期产品提高了一倍以上。

存储器访问阶段仅在访问存储器时使用。

乱序完成

-

乱序完成可提高指令执行的效率和速度。

RXv2内核的特性

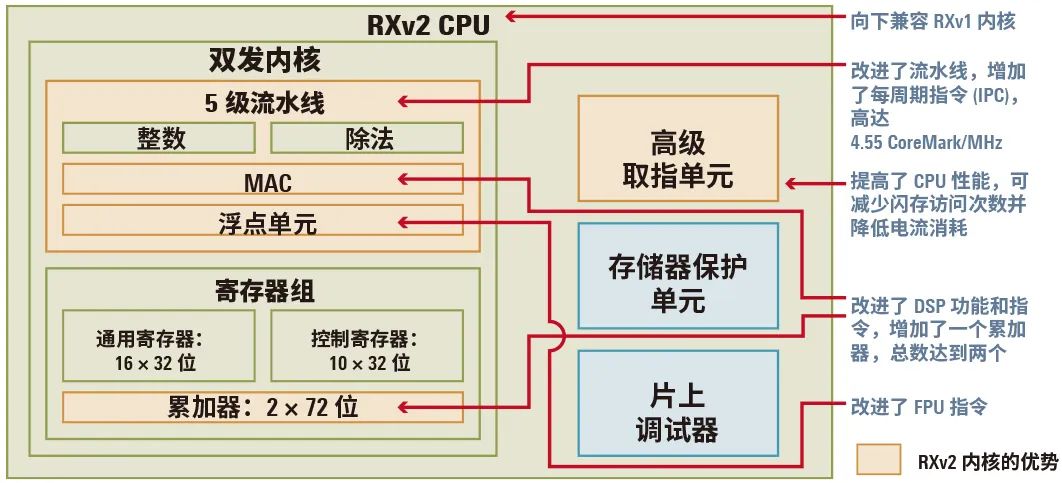

RXv2内核:CPU框图

进一步增强,同时仍与RXv1内核兼容

-

改进了流水线,可大幅增加每周期指令(IPC)。

-

具有改进的片上闪存接口的高级提取单元,可减少因分支指令产生的惩罚而引发的重新取指令,并可减少闪存访问次数,可在降低功耗的同时提高CPU性能。

-

改进了DSP和FPU功能的指令。

◆ RXv2 CPU配置框图

特性1:流水线改进

◆ RXv2 CPU配置框图

存储器访问阶段仅在访问存储器时使用。

改进了流水线处理和浮点运算的并行执行

-

浮点运算在执行阶段和存取器访问阶段并行进行。

-

整数运算指令和存储器访问或FPU指令可以同时执行。

-

有助于提高FPU执行速度和CPU性能。

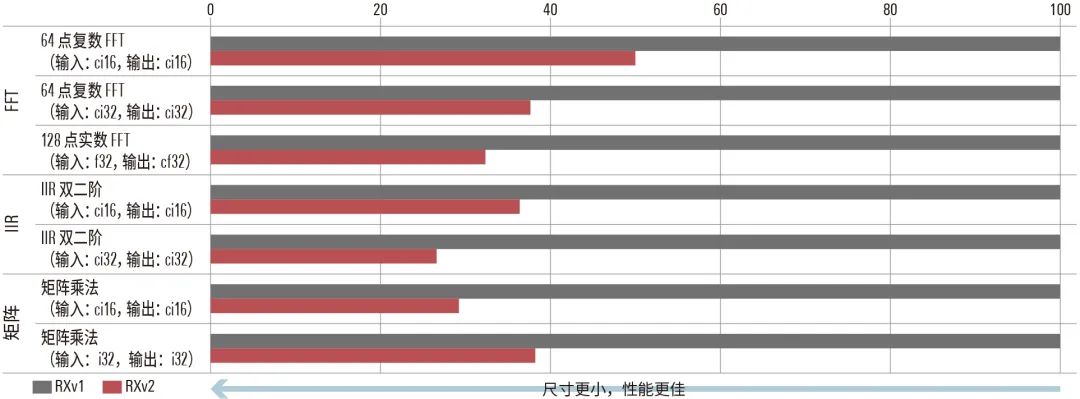

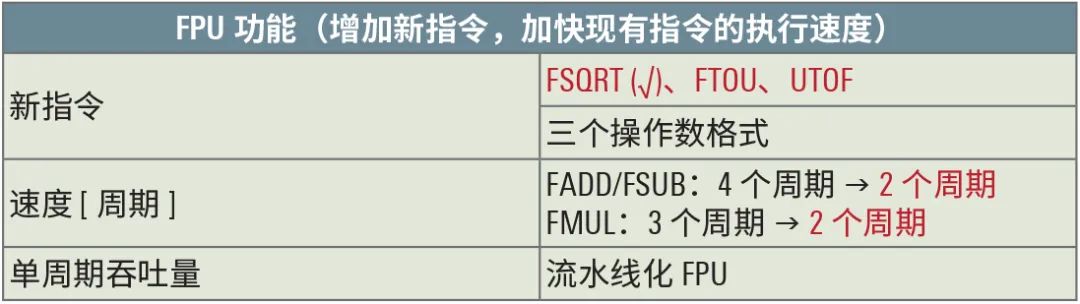

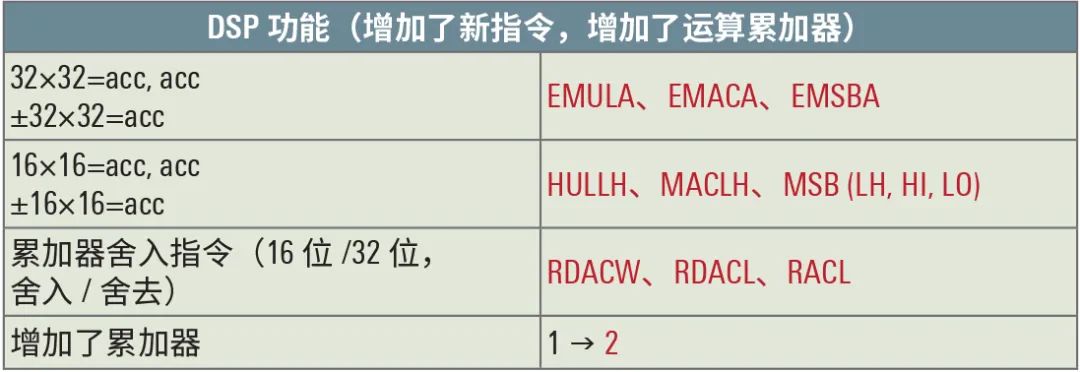

特性2:FPU和DSP功能增强

增强了FPU和DSP功能

-

减少了现有指令的执行周期计数并添加了新指令。

-

具有专用缓冲区的累加器数量已从1个增加到2个,提高了DSP运算的效率。

-

过滤操作的性能提高了四倍。

改进以红色字体显示

RXv3内核的特性

作为RXv2内核的后继产品,RXv3内核凭借新功能提高了性能,同时增加了双精度FPU和寄存器组保存功能。借助这些改进,RXv3内核在EEMBC CoreMark基准测试中获得的分数为5.82 CoreMark/MHz,CPU性能水平在业界名列前茅。对于各种需要实时处理的应用程序,RXv3内核有助于实现极其快速和高效的操作。

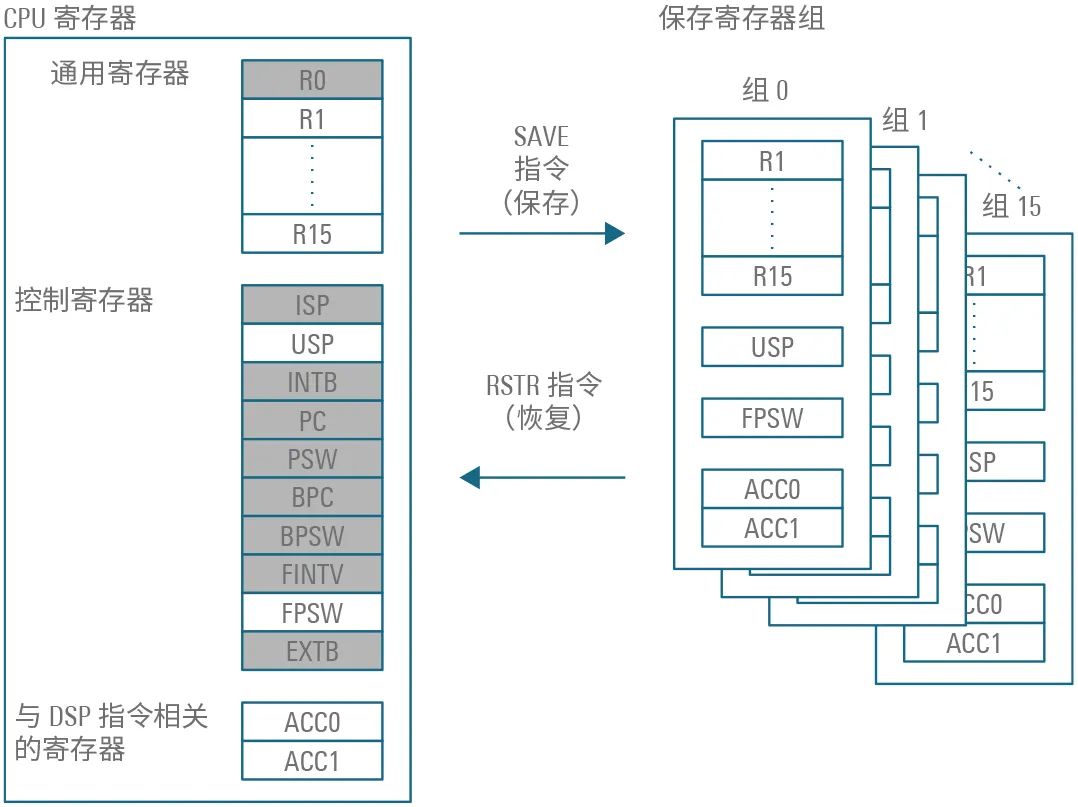

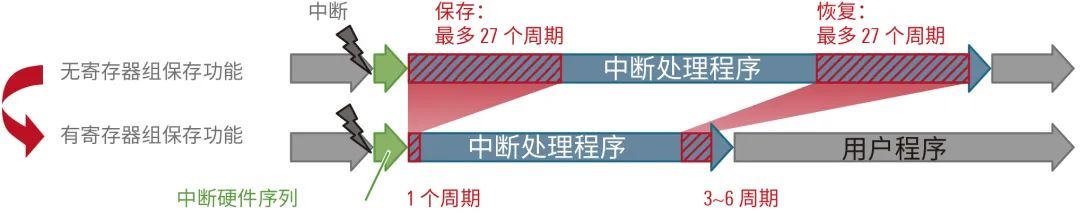

特性1:寄存器组保存功能

专用存取器可提高中断响应能力

-

提高了在CPU寄存器中保存/恢复数据的速度,改善了中断响应能力。

-

“寄存器保存组”作为寄存器保存功能的专用存储器提供。

-

用于访问寄存器保存组的专用指令(SAVE和RSTR)。

-

寄存器保存组数量:16 (RX72T)*¹

与传统产品的比较(将数据保存到所有寄存器)

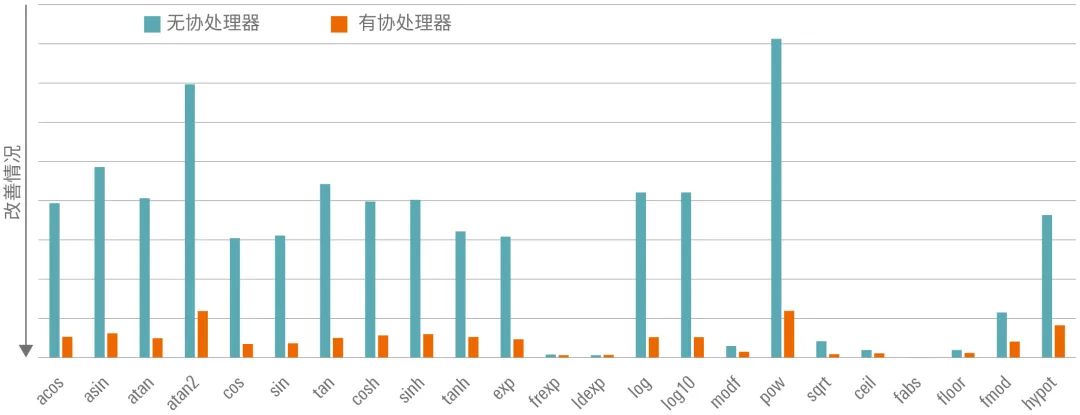

特性2:支持双精度FPU

-

首款搭载双精度浮点处理器的RX产品家族CPU内核。

-

显著提高了双精度浮点运算的处理性能(最多提高到八倍)。

原文标题:RX产品家族介绍手册 [3] RX内核的特性

文章出处:【微信公众号:瑞萨MCU小百科】欢迎添加关注!文章转载请注明出处。

-

mcu

+关注

关注

146文章

17521浏览量

355159 -

瑞萨

+关注

关注

36文章

22328浏览量

87247

原文标题:RX产品家族介绍手册 [3] RX内核的特性

文章出处:【微信号:瑞萨MCU小百科,微信公众号:瑞萨MCU小百科】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

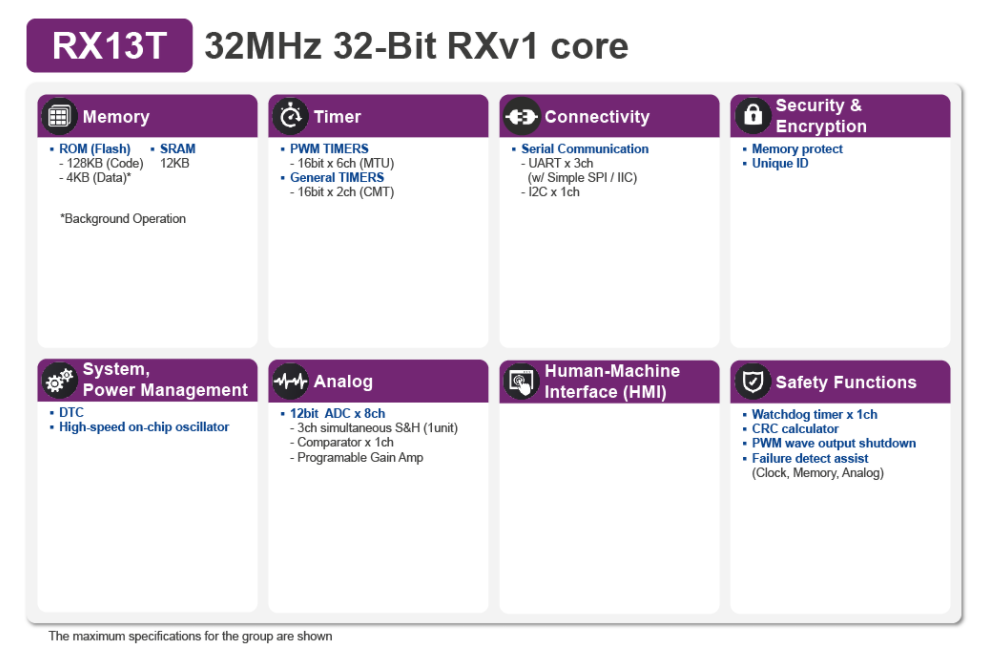

适用于单电机控制应用的RX13T系列32位微控制器数据手册

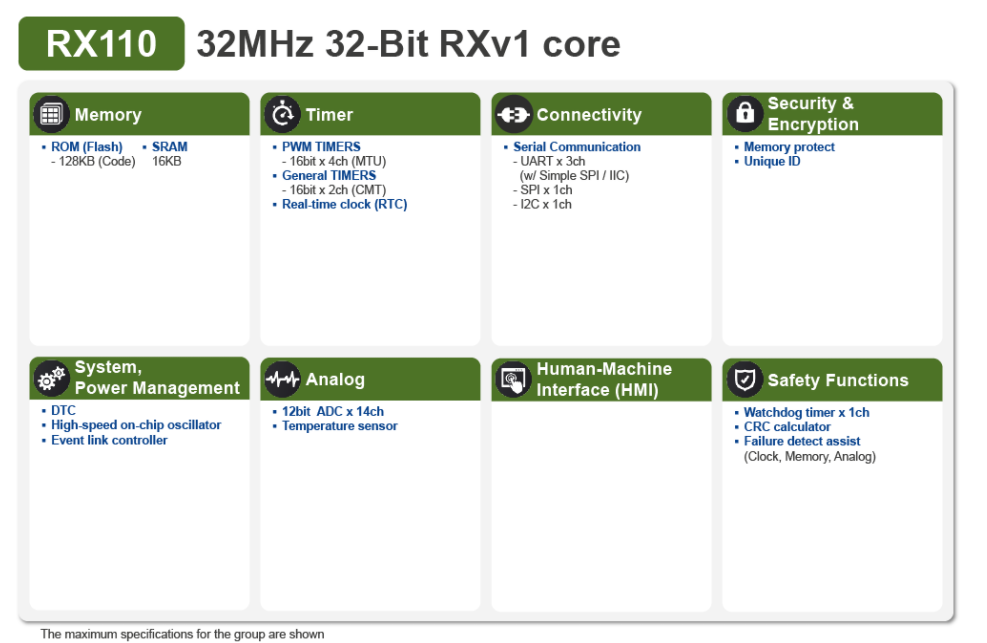

超低功耗的32位微控制器RX110系列数据手册

瑞萨电子推出RX261/RX260微控制器产品群

瑞萨电子推出RX261与RX260微控制器(MCU)产品群

AMD Radeon RX 7700 XT显卡的主要特性

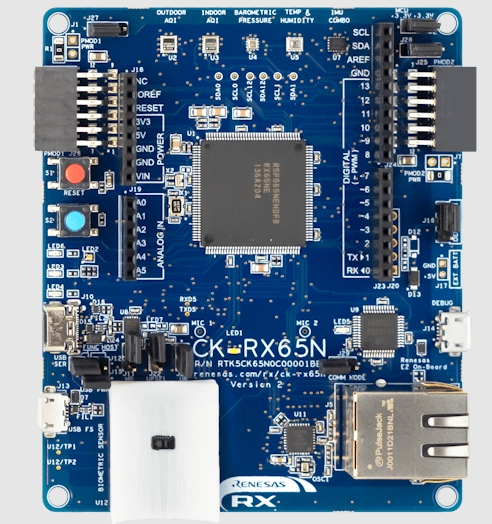

瑞萨RX MCU功能安全解决方案简介 硬件参考板

RX产品家族介绍手册 [3] RX内核的特性

RX产品家族介绍手册 [3] RX内核的特性

评论