接着上文,MCU芯片设计了mbist、scan chain之后,功能仿真失败?

有同学问,假设我们只是force ilm_sram的时钟使之偏斜可以不?答:仿真cpu必挂死,dlm也会有问题的,不信证明给你看。

定位到CPU指令预测跳转,该预测为跳转的指令进入到执行阶段时候,需要根据操作数据a、b是否相等来决定是否真正跳转,若预测错误即不跳转则flush pipieline,重新取跳转地址的指令。跳转则继续commit。

但是操作数a从cpu regfile取出来是x态,追踪发现操作数a是长指令回写到regfile的,是lsu长指令。

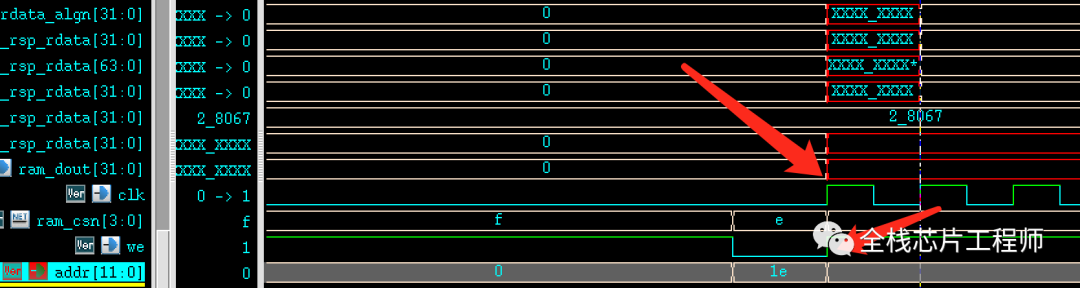

继续追踪到dlm_sram输出x态,显然dlm_sram也需要force一下时钟。又有同学问,和ilm_sram一起简单粗暴force为同一个时钟可以不?来吧,这样就又有新问题了。

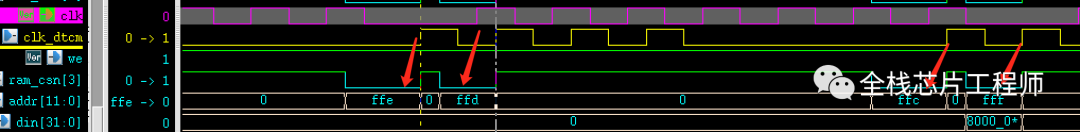

发现dlm_sram想把ffc ffd ffe三地址写0,fff想写0x8000, 却只有ffc ffd写入0,ffe fff皆写失败,因为时钟被force偏离了dlm_sram的要求,尽管满足了ilm_sram。为什么不满足dlm sram?因为各个sram的控制信号延时也不一样啊。

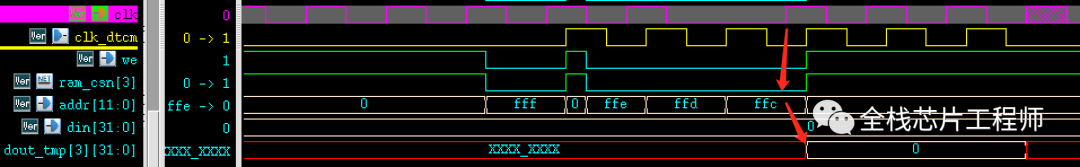

因此,下图看到sram读出ffc的值0,其他读出来都是x,导致pc值变成x态,取指令失败,cpu挂起。

因此,ilm sram和dlm sram被force为统一时钟后,也可能错误的,因为force的时钟满足了ilm sram的偏斜,却没能满足dlm sram的倾斜,因为cs/we等信号延时也不一样的。

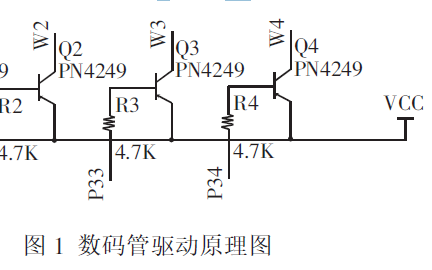

如下图,黄线是ilm_sram,行为ok,红线是dlm_sram,行为fail。

实际上,解决办法不是force,我们应该删除force语句,具体方法参见知识星球。

审核编辑:汤梓红

-

芯片

+关注

关注

455文章

50844浏览量

423837 -

mcu

+关注

关注

146文章

17154浏览量

351274 -

cpu

+关注

关注

68文章

10869浏览量

211854 -

仿真

+关注

关注

50文章

4086浏览量

133639 -

指令

+关注

关注

1文章

607浏览量

35722

原文标题:MCU芯片设计了mbist、scan chain之后,功能仿真失败(二)

文章出处:【微信号:全栈芯片工程师,微信公众号:全栈芯片工程师】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

为什么diable dcache能让mcu恢复正常?

请教Chipscope和boundary chain问题

帮你理解DFT中的scan technology

Arm PMC-100可编程MBIST控制器技术参考手册

DS26522 JTAG Scan Chain Mappin

一文读懂DC/AC SCAN测试技术

Proteus软件仿真失败的原因有哪些

【MCU】MDK错误:error in include chain (cmsis_armcc.h):expected identifier or ‘(‘

MCU芯片设计添加mbist、scan chain之后仿真失败如何解决

怎么配置DFT中常见的MBIST以及SCAN CHAIN

是否需要补插scan chain的isolation cell?怎么插呢?

芯片设计测试中scan和bist的区别

数模混合芯片scan chain问题解析

芯片后仿真要点

MCU芯片设计了mbist、scan chain之后,功能仿真失败?

MCU芯片设计了mbist、scan chain之后,功能仿真失败?

评论