本应用笔记介绍如何为MAX9217/MAX9247串行器和MAX9218/MAX9248/MAX9250解串器准备和使用评估板。

一般描述

MAX9217/MAX9218/MAX9247/MAX9248/MAX9250评估板(评估板)可供客户评估。评估板由两部分组成:右半部分包含一个单通道串行器元件(MAX9217或MAX9247),左半部分包含一个单通道解串器元件(MAX9218、MAX9248或MAX9250)。

评估板需要三个时钟信号,可由同一电源供电。串行器使用两个时钟信号:PCLK 和 DE_IN,其中DE_IN通常除以 PCLK 的 16 或 32 倍。解串器部分需要一个REFCLK,它可以来自同一源头,也可以由PCLK精度在2%以内的独立本地振荡器提供。

准备评估板的步骤

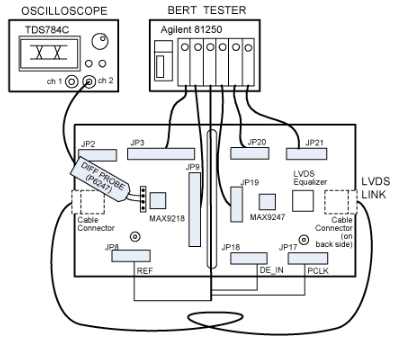

根据下面的配置表(表1-2)设置跳线,配置评估板(图1和图4)。

为评估板通电。一个3.3V直流单电源足以支撑评估板的每个部分;但是,如果需要对元件进行特性分析,建议为每个元件的电源引脚提供单独的电源(表 2)。

将PCLK、DE_IN和REFCLK时钟信号连接到评估板,如步骤2所述(另见以下示例)。安捷伦™ 8133A 脉冲发生器是从一个源提供所有三个时钟信号的理想选择。

将输入数据应用于串行器的输入引脚(位于评估板的右半部分),并使用逻辑分析仪和万用表检查解串器输出引脚。如果串行器的输入是视频信号,则可以使用液晶显示器(LCD),例如UNIGRAF的VTG-4116视频测试模式。

应特别注意串行器板上的跳线JP13。通过将该跳线连接到DVCC,JP17–JP21的接地引脚(10 x 2针座)连接到3.3V,固定数据模式可以施加到MAX9217/MAX9247串行器的数据输入端。应用外部数据模式时,此跳线应接地。

通过MAX9217/MAX9247生成伪随机位序列(PRBS)数据

MAX9217/MAX9247使用以下配置可以生成用于眼图测量的PRBS数据:

将/PWRDWN引脚接地。

将MOD0和MOD1引脚(MAX9247,这些引脚称为I.C.和PRE)连接至2.5V负直流电压。通过将差分探头连接到串行器板上JP2/JP3的引脚14和24(4引脚,单排接头),可以观察串行器眼图。解串器眼图位于解串器板的 JP2/JP3 引脚 5 和 6(4 引脚,单行接头)上。

图1.MAX9217评估板的电路原理图

图2.MAX9218评估板的电路原理图

快速功能检查

MAX9217/MAX9247/MAX9218/MAX9248/MAX9250评估板具有接头,用于连接逻辑分析仪、图形发生器或显示器。模式发生器(可以是逻辑分析仪系统的一部分),例如 HP16500C 系统,生成应用于串行器输入的并行测试字。测试字被序列化并通过LVDS链路发送到解串器。然后,逻辑分析器读取反序列化的测试字,并根据通过序列化程序和反序列化程序发送的引用或测试字检查错误。评估板也可以连接到图形发生器和LCD,用于串行链路的可视化测试。

串行链路的基本功能可以在没有逻辑分析仪、图形发生器或显示器的情况下进行检查。为了快速检查设置,串行器输入逻辑电平可以用跳线设置,相应的位/电压可以用解串器输出端的电压表读取。如需配置评估板以进行快速功能检查,请参考MAX9217/MAX9218评估板原理图,了解相关跳线和元件的名称和位置。请注意,当在跳线对上安装分流器时,芯片引脚被拉到逻辑高电平。如果任何跳线对上均未安装分流器,则芯片引脚被拉低。

配置跳线,以便快速检查评估板的功能(表1)。

| 部分 | 引脚名称 | 跳线 | 跳线功能 | 用于快速检查的跳线设置 |

|

MAX9218、MAX9248、 MAX9250 |

楼/楼 | JP1 | 选择上升沿或下降沿输出选通 | 低(下降沿) |

| RNG1 | JP4 | 选择锁相环工作范围 | 高频范围(参考数据手册) | |

| RNG0 | JP7 | 选择锁相环工作范围 | 高频范围 | |

| /PWRDWN有效 | JP11 | 选择芯片上电或关断 | 高(上电) | |

| 欧腾 (MAX9218/MAX9250), 不锈钢 (MAX9248) | JP12 | 选择输出启用或输出禁用 | 高电平(MAX9218/MAX9250使能输出),4%扩频模式(MAX9248) | |

| MAX9217、MAX9247 | (无) | JP13 | 用于硬连线输入的总线逻辑高电平 (DVCC) | DVCC |

| MOD1 (MAX9217), PRE (MAX9247) | JP15 | 选择输出调制电平 | 低电平(调制关断),MAX9247禁用预加重 | |

| MOD0 (MAX9217), I.C. (MAX9247) | JP16 | 选择输出调制电平 | 低电平(调制关断),内部连接引脚,用于MAX9247 | |

| /PWRDWN有效 | JP18 引脚 15 至引脚 16 | 选择芯片上电或关断 | 高(上电) | |

| RNG0 | JP22 | 选择锁相环工作范围 | 高频范围(参考数据手册) | |

| RNG1 | JP23 | 选择锁相环工作范围 | 高频范围 |

将电源连接至评估板(表2)。

| Part | Pin Name | EV Board Connection | Voltage |

|

MAX9217, MAX9247 |

VCCIN | IVCC | +3.3V |

| VCCPLL | PVCC | +3.3V | |

| VCCLVDS | LVCC | +3.3V | |

| VCC | DVCC | +3.3V | |

| (none) | VNEG | Ground | |

| PLL GND, LVDS GND, GND | GND | Ground | |

|

MAX9218, MAX9248, MAX9250 |

VCCPLL | PVCC | +3.3V |

| VCCLVDS | LVCC | +3.3V | |

| VCC | DVCC | +3.3V | |

| VCCO | OVCC | +3.3V | |

| (none) | VTEST | Open | |

| PLL GND, LVDS GND, VCCOGND, GND | GND | Ground |

连接所有时钟和控制信号(表3)。

| 芯片 | 芯片引脚名称 | 评估板连接 | 信号 |

|

MAX9217、 MAX9247 |

PCLK_IN | J18 PCLK (SMA 连接器) | 32兆赫 |

| DE_IN | JP18 引脚 13 | 1兆赫 | |

| RGB_IN和CNTL_IN | JP18, JP19, JP20, JP21 | 打开 | |

|

MAX9218、MAX9248、 MAX9250 |

REFCLK | J8 参考 (SMA 连接器) | 32兆赫 |

完成步骤1-3后,可以在MAX9218/MAX9248/MAX9250解串器的输出端观察到以下信号(表4)。

| 引脚名称 | 评估板连接 | 信号 |

|

RGB_OUT, CNTL_OUT |

JP3 和 JP9 | 低 |

| /有效锁定 | JP9 引脚 23 | 低 |

| PCLK_OUT | JP9 引脚 25 | 32兆赫 |

| DE_OUT | JP9 引脚 21 | 1兆赫 |

MAX9217/MAX9247 RGB_IN和CNTL_IN输入具有内部下拉电阻。当输入保持打开状态时,串行器会自动读取逻辑低电平。将一些输入连接到 JP3、JP3、JP11 和 JP12 接头上的 13.14V。这可以通过将 JP13 设置为 DVCC 位置并在这些 2 x 10 接头的相对引脚之间使用分流器来完成。MAX9218/MAX9248/MAX9250解串器上的相应输出应变为高电平。例如,如果RGB_IN0(JP14引脚1)连接到3.3V,则RGB_OUT0(JP7引脚27)应变为高电平。

使用示波器在MAX9217/MAX9247串行器输出(JP17/JP18)或MAX9218/MAX9248/MAX9250解串器输入(JP4/JP6)的LVDS信号线上连接差分FET探头来查看串行信号。

笔记

RNG0和RNG1在MAX9217/MAX9247和MAX9218/MAX9248/MAX9250上具有内部下拉电阻。为了激活逻辑低电平,这些引脚可以保持浮动状态。

DE_IN必须切换MAX9217/MAX9218芯片组才能正常工作。通常,图形控制器的数据使能引脚(ENAB)连接到MAX9217/MAX9247上的DE_IN,并从MAX9218/MAX9248/MAX9250的DE_OUT中恢复。DE_IN必须至少每 4,194,304 个PCLK_IN周期过渡一次。

时钟输入具有用于接地的 50Ω 端接电阻的焊盘。评估板出厂时不带这些电阻——未安装。干净转换在 PCLK、DE_IN 和 REF 输入上尤为重要。如果需要,安装50Ω输入端接电阻以减少反射。使用容差为 1% 或更好的电阻器,使输入紧密匹配。

链路操作不需要串联耦合电容(Rx侧为C28/C29,Tx侧为C55/C58)。对于直接耦合操作,用一个零欧姆电阻器短接串联电容焊盘。评估板出厂时安装0.1μF串联电容。

对于LVDS信号的端接,请使用100Ω差分(R3)端接或100Ω等效网络(R1/R2/R5/R4)。不要同时使用两者。安装两个端接会产生较大的反射(见图 3)。

MAX20原理图所示的电阻R46-R9217仅用于内部IC特性,未填充在评估板上。

MAX1所示的电容C15-C27和C41-C9218仅用于内部IC特性,未填充在评估板上。同样,评估板上未安装电阻R1-R3、R6-R7、R10和R11。

图3.LVDS 端接选项。仅使用上述终止选项之一;安装两个端接会产生较大的反射。

|

图形 控制器 输出 |

|

MAX9217输入 |

|

MAX9218输出 |

|

液晶输入 |

| R0 |

|

RGB_IN0 |

|

RGB_OUT0 |

|

R0 |

| R1 |

|

RGB_IN1 |

|

RGB_OUT1 |

|

R1 |

| R2 |

|

RGB_IN2 |

|

RGB_OUT2 |

|

R2 |

| R3 |

|

RGB_IN3 |

|

RGB_OUT3 |

|

R3 |

| R4 |

|

RGB_IN4 |

|

RGB_OUT4 |

|

R4 |

| R5 |

|

RGB_IN5 |

|

RGB_OUT5 |

|

R5 |

| G0 |

|

RGB_IN6 |

|

RGB_OUT6 |

|

G0 |

| G1 |

|

RGB_IN7 |

|

RGB_OUT7 |

|

G1 |

| G2 |

|

RGB_IN8 |

|

RGB_OUT8 |

|

G2 |

| G3 |

|

RGB_IN9 |

|

RGB_OUT9 |

|

G3 |

| G4 |

|

RGB_IN10 |

|

RGB_OUT10 |

|

G4 |

| G5 |

|

RGB_IN11 |

|

RGB_OUT11 |

|

G5 |

| B0 |

|

RGB_IN12 |

|

RGB_OUT12 |

|

B0 |

| B1 |

|

RGB_IN13 |

|

RGB_OUT13 |

|

B1 |

| B2 |

|

RGB_IN14 |

|

RGB_OUT14 |

|

B2 |

| B3 |

|

RGB_IN15 |

|

RGB_OUT15 |

|

B3 |

| B4 |

|

RGB_IN16 |

|

RGB_OUT16 |

|

B4 |

| B5 |

|

RGB_IN17 |

|

RGB_OUT17 |

|

B5 |

| 同步 |

|

CNTL_IN0 |

|

CNTL_OUT0 |

|

同步 |

| 垂直同步 |

|

CNTL_IN1 |

|

CNTL_OUT1 |

|

垂直同步 |

| 未分配 |

|

CNTL_IN2 |

|

CNTL_OUT2 |

|

未分配 |

| 未分配 |

|

CNTL_IN3 |

|

CNTL_OUT3 |

|

未分配 |

| 未分配 |

|

CNTL_IN4 |

|

CNTL_OUT4 |

|

未分配 |

| 未分配 |

|

CNTL_IN5 |

|

CNTL_OUT5 |

|

未分配 |

| 未分配 |

|

CNTL_IN6 |

|

CNTL_OUT6 |

|

未分配 |

| 未分配 |

|

CNTL_IN7 |

|

CNTL_OUT7 |

|

未分配 |

| 未分配 |

|

CNTL_IN8 |

|

CNTL_OUT8 |

|

未分配 |

| 显示启用 |

|

DE_IN |

|

DE_OUT |

|

显示启用 |

审核编辑:郭婷

-

振荡器

+关注

关注

28文章

3875浏览量

139643 -

脉冲发生器

+关注

关注

5文章

178浏览量

34354 -

解串器

+关注

关注

1文章

107浏览量

13493

发布评论请先 登录

相关推荐

MAX9217/MAX9218视频链路中的音频数据传输

MAX9248/MAX9250 pdf

配合MAX9217/MAX9218/MAX9247/MAX9

配合MAX9217/MAX9218/MAX9247/MAX9

MAX9217/MAX9218 视频链路中的音频数据传输

MAX9217/MAX9218中文资料

MAX9217/MAX9218视频链路中的音频数据传输

MAX9217/MAX9218 视频链路中的音频数据传输

MAX9247/MAX9218串行器/解串器芯片组的性能测试

MAX9217/MAX9218视频链路中的音频数据传输

MAX9217/MAX9218视频链路中的音频数据传输

利用MAX9217/MAX9218芯片组实现视频数据传输

串行器和解串器对的性能测试:MAX9247和MAX9218

与MAX9217/MAX9218/MAX9247/MAX9248/MAX9250评估板配合使用

与MAX9217/MAX9218/MAX9247/MAX9248/MAX9250评估板配合使用

评论