本应用笔记介绍了设计人员如何保护其 Xilinx FPGA 实现、保护 IP 并防止附加外设伪造。设计人员可以使用本应用笔记中描述的参考设计之一来实现这种安全性。这些设计在FPGA和DeepCover安全身份验证器之间实现了SHA-256或ECDSA质询和响应安全认证。

介绍

本应用笔记重点介绍SHA-256认证参考设计(RD),该参考设计采用MAXREFDES34#(用于1-Wire)和MAXREFDES43#用于I。2C. 每个参考设计 (RD) 都描述了状态机的 Verilog 实现或微控制器中的“C”裸机实现。每个实现方案都在相应的FPGA演示板上进行测试。

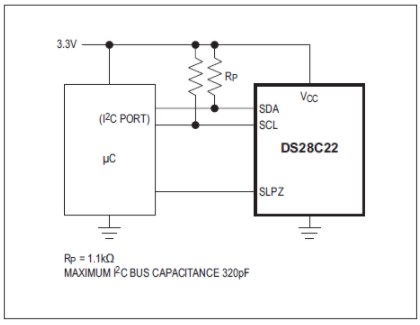

对于1-Wire设计,参考代码定义了主机FPGA上的组合SHA-256处理器和1-Wire主机。对于我®2C 设计,参考代码定义 SHA-256 处理器并利用现有的 FPGA I2C 协议。RD 使用以下安全身份验证器之一:

DS28E15DeepCover安全认证器,带1线SHA-256和512位用户EEPROM

DS28C22DeepCover 安全内存与 I2C SHA-256 身份验证、加密和 3Kb 用户 EEPROM

DS28E35DeepCover安全认证器,具有1线ECDSA和1Kb用户EEPROM

为了将Maxim安全认证器IC与FPGA演示板连接,每个RD都附带一个兼容的插件模块——Pmod™端口标准由 Digilent, Inc. 开发相应的IC焊接在Pmod板上。关于1-Wire设计,只需稍作调整,即可使用存储器密度更大的SHA-256认证器,例如DS28E22或DS28E25。

为什么要将安全性应用于FPGA系统?部分详细介绍了设计人员面临的重要安全问题。以下标题为“保护您的 FPGA”的部分演示了身份验证如何实际保护 FPGA 系统。

为什么要将安全性应用于 FPGA 系统?

外围设备的防伪保护

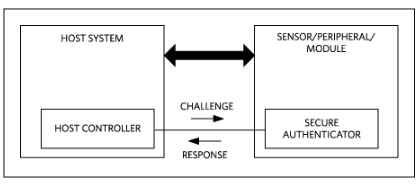

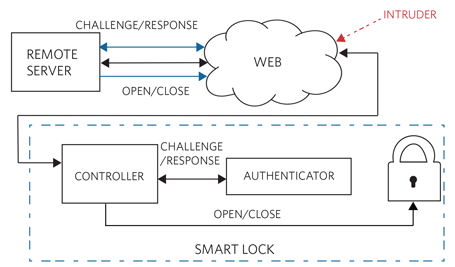

使用 FPGA 通信和操作替换外设、耗材、模块或传感器的系统通常成为造假者或未经授权的售后市场公司的目标。这些假冒版本的外设可能会带来安全问题,降低应用程序的质量,并且通常会对OEM解决方案产生负面影响。此外,OEM将外围设备的收入损失给这些造假者。在解决方案中引入安全认证使FPGA能够确保外设的真实性,并在检测到假冒产品时采取特定于应用的操作。如图1所示,在系统和连接的外设之间执行质询和响应序列以确认真实性。

FPGA 知识产权保护和实施保护

基于静态RAM(SRAM)的FPGA几乎没有保护措施来保护IP(即配置数据或FPGA实现)免受非法复制和盗窃。原因是一旦数据被加载,它就会保存在SRAM存储单元中,可以很容易地探测以确定其内容。此外,如果没有某种类型的安全机制来保护配置数据或位文件,然后再将其加载到芯片中,则该数据可以被窥探。浏览这些数据是可能的,因为位流通常存储在FPGA在上电时加载其配置模式时读取的单独存储芯片中。克隆者可以简单地复制配置文件并创建原始文件的克隆。这些类型的 FPGA 没有内置加密功能,否则可以保护配置文件不被复制。

功能管理、许可证管理和过度构建保护

功能管理。为了减少设计时间和工作量,设计人员将创建功能齐全的FPGA系统,并使用固件去除某些方面的功能,以实现不同的价位或功能级别。然而,这产生了一个新问题:需要多个功能齐全系统的聪明客户可以只购买一个功能齐全的单元和几个功能减少的单元。然后,复制软件,更简单的单元的行为类似于功能齐全的设备,但价格较低,从而缩短了系统供应商。

身份验证如何工作?

若要以最安全的方式实现身份验证,请使用以下内容作为一般准则:

确保随机质询是加密安全的随机数。

知道一个密钥(称为“FPGA 密钥”),该密钥可用于内部操作,但无法从外部发现。

计算涉及密钥、随机数和其他数据的哈希,就像安全内存一样。

比较哈希结果。

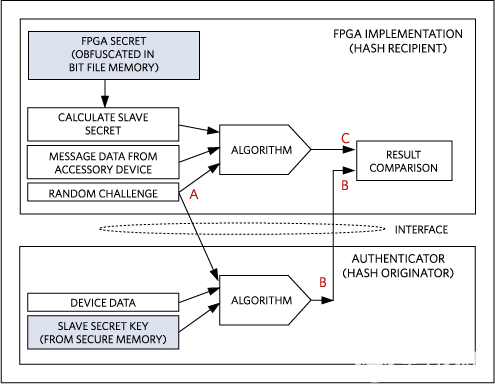

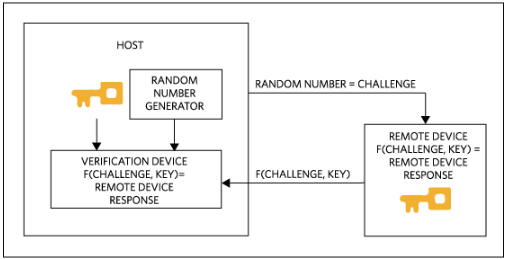

在 FPGA 环境中,质询和响应身份验证的工作方式显示在以下编号语句中。字母(例如 A、B、C)对应于图 2 中的数据流。本节介绍 SHA-256 对称身份验证。

生成一个随机数并将其作为质询 (A) 发送给安全身份验证器。

指示身份验证器根据其密钥、质询 A、其唯一 ID 和其他固定数据计算哈希。哈希是算法块 (B) 的输出。

根据安全身份验证器和 FPGA 密钥使用的相同输入和常量计算哈希 (C)。

将安全身份验证器 (B) 计算的哈希值作为响应,并将其与预期的响应 (C) 进行比较。

如果预期响应和实际响应相同,则FPGA知道身份验证器是真实的。如果是真实的,您的安全目标(IP保护,防伪保护等)就实现了。

图2.质询和响应身份验证流程更详细。证明哈希发起方(安全验证器)的真实性。

如前所述,FPGA 和安全身份验证器之间的身份验证实现了为什么要将安全性应用于 FPGA? 部分的第 1 点到第 3 点的安全性。现在,让我们观察如何根据以下框图物理设置安全系统。

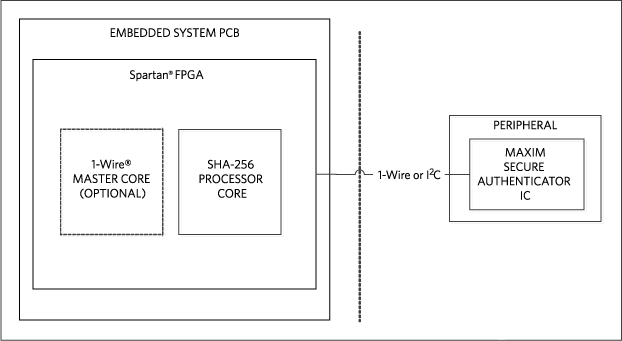

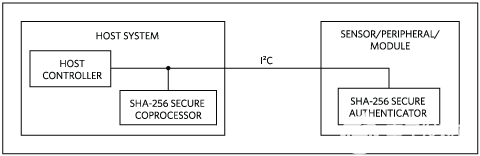

外围设备的防伪保护

要实现防伪保护,应使用如图3所示的系统配置。FPGA 及其相应的安全实现驻留在嵌入式系统中。一些外围设备(可能是传感器、一次性、消耗品或其他嵌入式系统)是作为设计师希望保护的对象。Maxim安全认证IC位于该外设中。

图3.外围设备防伪框图。

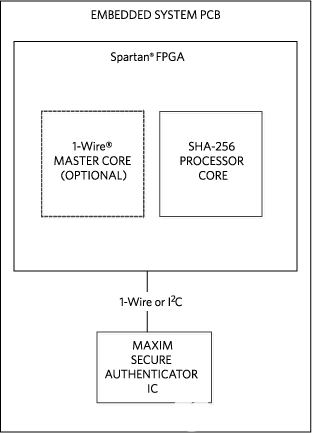

IP 保护、功能管理、许可证管理和过度构建保护

对于标题为“为什么要对FPGA应用安全性?”一节中描述的所有其他安全需求,应使用图4所示的硬件设置。FPGA及其相应的安全实现与Maxim安全认证IC一起位于嵌入式系统中。

图4.知识产权保护和其他应用的框图。

| 参考设计 | FPGA | 演示板 | 实现 | 使用的认证IC | 认证IC接口 |

| MAXREFDES34# |

赛灵思 斯巴达-6 |

安富利斯巴达-6 LX9 微板® | 威瑞洛格 | DS28E15 | 1-线 |

|

赛灵思 锌芯 |

微锌 | “C” | |||

| MAXREFDES43# |

赛灵思 锌芯 |

泽德板™ | “C” | DS28C22 | 我2C |

| MAXREFDES44# |

赛灵思 锌芯 |

微锌 | “C” | DS28E35 | 1-线 |

参考设计特定说明

采用DS43C28的MAXREFDES22#是独一无二的,因为它对FPGA和DS28C22之间通信的敏感数据实现了双向、小消息加密。此加密功能是可选的;最常见的用途是DS28C22位于连接的外设子系统内。或者,也许有必要加密敏感的传感器数据、校准数据、特征设置数据或个人数据(例如,患者心率或 SSN)。

采用DS44E28的MAXREFDES35#采用非对称ECDSA认证,而不是实现对称SHA-256认证。对于对称认证,FPGA和认证IC必须存储相同的密钥,因此敏感的密钥数据驻留在系统的两端。然而,对于非对称认证,FPGA只保存公钥,DS28E35保存私钥。唯一的敏感数据是私钥;公钥不需要保护。

从两个角度来看,使用非对称加密可能更具吸引力:

您正在将产品许可给客户或使用多个合同制造商。非对称身份验证提供了一个很好的管理工具,用于添加新许可证或由于使用证书而删除现有许可证。有关证书的更多信息,请参见应用笔记 5767 “ECDSA 认证系统的基础”。

FPGA 配置/位文件安全性较差的实现。如果 FPGA 密钥暴露,对这些应用使用 SHA-256 对称身份验证可能会有风险;但是,请注意,对于相关的参考设计(例如,用于Spartan-34 FPGA的MAXREFDES6#),已经采取了额外的步骤来保护FPGA端的密钥。事实上,如果您没有实现内置的FPGA加密功能(在适用的FPGA上,如Xilinx Zynq),或者如果您使用的是不保护配置/位文件的上一代FPGA,那么使用DS28E35是理想的选择。

带有DS34E28的MAXREFDES15#使用SHA-256实现对称认证。这些身份验证方案要求FPGA端密钥和安全身份验证器密钥都是安全的。由于以下原因,MAXREFDES34# 成功地保护了 FPGA 端的密钥:

密钥存储在闪存器件的FPGA位文件中。将位文件从位反转回Verilog代码是非常困难的(Spartan-6参考是用Verliog编写的)。因此,位文件的模糊性和笨拙性提供了第一层安全性。

位文件中的密钥与DS28E15中存储的密钥不完全相同。FPGA根据自己的密钥版本计算DS28E15密钥。

本应用笔记中未披露其他专有的FPGA秘密保护技术。

总结

FPGA 嵌入式系统的设计人员面临着许多潜在的安全威胁,包括伪造外设和复制 FPGA 实现等。将Maxim安全认证器与上述任一参考设计结合使用,可以保护FPGA系统免受这些潜在问题的影响。

审核编辑:郭婷

-

传感器

+关注

关注

2558文章

52020浏览量

760606 -

处理器

+关注

关注

68文章

19647浏览量

232443 -

FPGA

+关注

关注

1638文章

21883浏览量

610749

发布评论请先 登录

相关推荐

恩智浦推出经认证的全新EdgeLock安全身份验证芯片,简化物联网设备安全认证

HTTPServer可以支持基本的HTTP身份验证吗?

无线身份验证的门禁控制系统设计方案

Vivado和SDK身份验证错误

什么是身份验证和授权

什么是询问握手身份验证协议

为设计选择正确的安全身份验证方法

安全哈希算法的基础知识,如何使用算法进行身份验证

通过SHA-256主/从身份验证系统实现更高的安全性

使用加密和身份验证来保护UltraScale/UltraScale+ FPGA比特流

使用DeepCover安全身份验证器保护您的FPGA系统

使用DeepCover安全身份验证器保护您的FPGA系统

评论