质询和响应身份验证要求 MAC 发起方和 MAC 接收方根据隐藏的机密和公共数据计算消息认证代码。发起方通常是 SHA-1 身份验证器或具有 SHA-1 引擎的受保护内存。MAC 接收方是应用程序的主机处理器。本应用笔记介绍了DSSHA1可合成SHA-1协处理器,该协处理器可在专用集成电路(ASIC)或现场可编程门阵列(FPGA)中实现,作为DS2460 SHA-1协处理器或基于微处理器的替代方案。

介绍

质询和响应身份验证基于消息身份验证代码 (MAC) 的计算。该方法涉及两个实体,即 MAC 发起方和 MAC 接收方,它们共享一个隐藏的机密。为了证明 MAC 发起方的真实性,MAC 接收方会生成一个随机数,并将其作为质询发送给发起方。然后,MAC 发起方必须根据机密、消息和质询计算新的 MAC,并将其发送回接收方。如果发起方证明能够为任何质询生成有效的MAC,则非常确定它知道该机密,因此可以被认为是真实的。计算消息身份验证代码的彻底审查和国际认证的算法是SHA-1,它由美国国家标准与技术研究院(NIST)开发。

Maxim生产一系列采用SHA-1算法的认证器件。教程3675“通过安全认证保护研发投资”,以安全存储器和DS2460 SHA-1协处理器的形式解释了Maxim认证方案。DSSHA1存储器映射SHA-1协处理器允许DS2460的计算能力在专用集成电路(ASIC)或现场可编程门阵列(FPGA)中实现,无需开发软件即可执行复杂的SHA-1计算。DSSHA1或DS2460计算的MAC仅适用于Maxim SHA-1器件。

描述

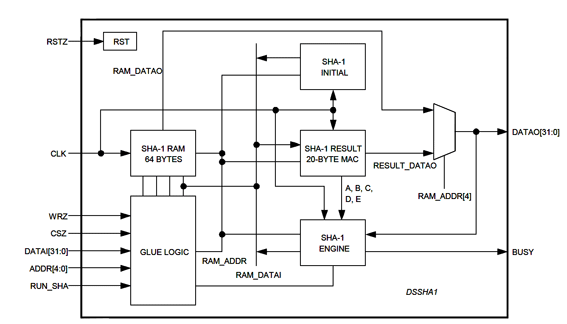

DSSHA1 是一款可合成的内存映射 SHA-1 协处理器,包括一个存储 64 字节消息的 64 字节通用 RAM。输入消息用于计算 SHA-1 MAC。DSSHA1 输入和输出端口信号设计用于内部连接到 32 位总线。通过积极的比较结果,在主机系统和从属附件之间实现了身份验证安全性。

图 1 显示了 DSSHA1 框图。表 1 描述了将 DSSHA1 连接到主机系统的信号。使用数据总线输入、地址和控制信号,将 64 字节 SHA-1 消息插入 RAM。将输入信号RUN_SHA触发至逻辑高电平将启动SHA-1计算。输出 BUSY 信号指示正在发生的计算。完成 BUSY 信号后,结果寄存器包含 20 字节消息摘要以供读取。

图1.方框图。

| 名字 | 类型* | 功能 |

| 时钟 | 我 | 时钟。在正边,信号 DATAI[31:0] 和 DATAO[31:0] 上的数据被输入和输出。 |

| RSTZ | 我 | /有效复位。RSTZ信号在CLK信号的正边沿的每个间隔处进行评估。有必要在每次加载 512 位消息和 MAC 计算之前进行重置。 |

| 南航股份 | 我 | /有效芯片选择。对于寄存器和存储器的所有访问,此信号必须为低电平。 |

| WRZ | 我 | 低电平有效写使能。在所有写入操作期间,此信号必须为低电平。 |

| 附加值[4:0] | 我 | 地址 [4:0]。这五个信号就是地址信号。 |

| 数据[31:0] | 我 | 数据总线输入。这32个信号是输入数据总线。 |

| 数据[31:0] | O | 数据总线输出。这32个信号是输出数据总线。 |

| 忙 | O | 忙。当信号为高电平时,此信号表示SHA-1协处理器正忙于执行计算。当此信号为高电平时,不应有数据访问。 |

| RUN_SHA | 我 | 运行 SHA-1。该信号必须只有一个时钟周期宽,并在CLK信号的正边沿启动SHA-1计算。 |

| *I = 输入,O = 输出。 | ||

详细寄存器说明

DSSHA1 存储器由 32 个 2 位字组成,从输入缓冲器开始,以寄存器结束,用于读取 MAC 结果(表 <>)。

| 地址(十六进制) | 类型 | 访问 | 功能 |

| 00h 至 0Fh | 公羊 | 读/写 | 64字节缓冲器输入。这是 512 位输入块,通常包括 64 位从设备密钥和由随机质询和各种数据组成的 448 位输入消息。 |

| 10小时至14小时 | 寄存 器 | 读 | 20 字节结果。这是用于与 SHA-1 从设备接收到的 MAC 进行比较的 MAC。 |

输入缓冲器(00h 至 0Fh)

SHA-1 引擎通过 64 字节输入缓冲区接收要处理的数据。此缓冲区保存 SHA-512 引擎处理以生成 MAC 的 1 位消息。机密和其他消息数据包含在输入缓冲区中。密钥的安全性是留给设计人员的任务。数据的格式由每个Maxim SHA-1从器件定义。

MAC 结果(10 小时至 14 小时)

SHA-20 计算的 1 字节 MAC 驻留在 MAC 结果地址空间中。

设备操作

DSSHA1在应用中的典型用途包括写入、读取和运行SHA-1引擎,并使用MAC结果将该模块与1-Wire SHA-1器件的MAC进行外部比较。所有这些活动都通过具有独立数据输入和输出线的 32 位接口进行控制,以便轻松连接到 ASIC 或 FPGA 内部总线。下面的 SHA-1 引擎控制部分介绍了数据输入和输出格式以及如何指示 SHA-1 引擎执行 MAC 计算。

SHA-1 发动机控制

DSSHA1执行SHA-1发动机的工作。输入缓冲区接受消息。MAC 输出缓冲区接收生成的 SHA-1 计算。图 2 说明了流入和流出 SHA-1 引擎的数据流。

应用电源复位启动使用 SHA-1 引擎的第一步。接下来,以表 3 的格式将消息加载到输入缓冲区中。消息加载完成后,用户向RUN_SHA输入信号发送脉冲。在 SHA-1 计算期间,BUSY 信号变为并保持逻辑高电平。当SHA-1计算完成时,忙信号再次变为逻辑低电平。所有五个MRR寄存器(见表4)都包含用于读取的MAC结果。

图2.数据流图。

| M0[31:24] = (IB + 0) | M0[23:16] = (IB + 1) | M0[15:8] = (IB + 2) | M0[7:0] = (IB + 3) |

| M1[31:24] = (IB + 4) | M1[23:16] = (IB + 5) | M1[15:8] = (IB + 6) | M1[7:0] = (IB + 7) |

| M2[31:24] = (IB + 8) | M2[23:16] = (IB + 9) | M2[15:8] = (IB + 10) | M2[7:0] = (IB + 11) |

| M3[31:24] = (IB + 12) | M3[23:16] = (IB + 13) | M3[15:8] = (IB + 14) | M3[7:0] = (IB + 15) |

| M4[31:24] = (IB + 16) | M4[23:16] = (IB + 17) | M4[15:8] = (IB + 18) | M4[7:0] = (IB + 19) |

| M5[31:24] = (IB + 20) | M5[23:16] = (IB + 21) | M5[15:8] = (IB + 22) | M5[7:0] = (IB + 23) |

| M6[31:24] = (IB + 24) | M6[23:16] = (IB + 25) | M6[15:8] = (IB + 26) | M6[7:0] = (IB + 27) |

| M7[31:24] = (IB + 28) | M7[23:16] = (IB + 29) | M7[15:8] = (IB + 30) | M7[7:0] = (IB + 31) |

| M8[31:24] = (IB + 32) | M8[23:16] = (IB + 33) | M8[15:8] = (IB + 34) | M8[7:0] = (IB + 35) |

| M9[31:24] = (IB + 36) | M9[23:16] = (IB + 37) | M9[15:8] = (IB + 38) | M9[7:0] = (IB + 39) |

| M10[31:24] = (IB + 40) | M10[23:16] = (IB + 41) | M10[15:8] = (IB + 42) | M10[7:0] = (IB + 43) |

| M11[31:24] = (IB + 44) | M11[23:16] = (IB + 45) | M11[15:8] = (IB + 46) | M11[7:0] = (IB + 47) |

| M12[31:24] = (IB + 48) | M12[23:16] = (IB + 49) | M12[15:8] = (IB + 50) | M12[7:0] = (IB + 51) |

| M13[31:24] = (IB + 52) | M13[23:16] = (IB + 53) | M13[15:8] = (IB + 54) | M13[7:0] = (IB + 55) |

| M14[31:24] = (IB + 56) | M14[23:16] = (IB + 57) | M14[15:8] = (IB + 58) | M14[7:0] = (IB + 59) |

| M15[31:24] = (IB + 60) | M15[23:16] = (IB + 61) | M15[15:8] = (IB + 62) | M15[7:0] = (IB + 63) |

| Mt = SHA-1 发动机的输入缓冲区;0 ≤ t ≤ 15;32 位字,起始地址为 00h,结束地址为 0Fh。 IB = 输入缓冲区。 | |||

表 4 显示了保存 MAC 的五个 32 位变量 A 到 E 如何映射到各自的位置。

| 地址(十六进制) | MAC 结果寄存器 (MRR) |

| 10小时 | MRR[31:0] = A[31:0](最不显著) |

| 11小时 | MRR[31:0] = B[31:0] |

| 12小时 | MRR[31:0] = C[31:0] |

| 13小时 | MRR[31:0] = D[31:0] |

| 14小时 | MRR[31:0] = E[31:0](最显著) |

MAC 比较

主站需要针对 DSSHA1 MAC 测试从属 MAC。如果从属 MAC 和 DSSHA1 MAC 的值相等,则验证真实性。如果从属 MAC 和 DSSHA1 MAC 不同,则会验证欺诈行为。

功能验证

要测试 DSSHA1,测试消息“abc”可以验证功能。此具有适当填充的测试消息可以转换为以下输入块:

| W[0] = 61626380 | W[8] = 00000000 |

| W[1] = 00000000 | W[9] = 00000000 |

| W[2] = 00000000 | W[10] = 00000000 |

| W[3] = 00000000 | W[11] = 00000000 |

| W[4] = 00000000 | W[12] = 00000000 |

| W[5] = 00000000 | W[13] = 00000000 |

| W[6] = 00000000 | W[14] = 00000000 |

| W[7] = 00000000 | W[15] = 00000018 |

使用表 3 的格式,此测试消息的输入块将是表 5 中的值。

| M0[31:24] = 61h | M0[23:16] = 62h | M0[15:8] = 63h | M0[7:0] = 80h |

| M1[31:24] = 00h | M1[23:16] = 00h | M1[15:8] = 00h | M1[7:0] = 00h |

| M2[31:24] = 00h | M2[23:16] = 00h | M2[15:8] = 00h | M2[7:0] = 00h |

| M3[31:24] = 00h | M3[23:16] = 00h | M3[15:8] = 00h | M3[7:0] = 00h |

| M4[31:24] = 00h | M4[23:16] = 00h | M4[15:8] = 00h | M4[7:0] = 00h |

| M5[31:24] = 00h | M5[23:16] = 00h | M5[15:8] = 00h | M5[7:0] = 00h |

| M6[31:24] = 00h | M6[23:16] = 00h | M6[15:8] = 00h | M6[7:0] = 00h |

| M7[31:24] = 00h | M7[23:16] = 00h | M7[15:8] = 00h | M7[7:0] = 00h |

| M8[31:24] = 00h | M8[23:16] = 00h | M8[15:8] = 00h | M8[7:0] = 00h |

| M9[31:24] = 00h | M9[23:16] = 00h | M9[15:8] = 00h | M9[7:0] = 00h |

| M10[31:24] = 00h | M10[23:16] = 00h | M10[15:8] = 00h | M10[7:0] = 00h |

| M11[31:24] = 00h | M11[23:16] = 00h | M11[15:8] = 00h | M11[7:0] = 00h |

| M12[31:24] = 00h | M12[23:16] = 00h | M12[15:8] = 00h | M12[7:0] = 00h |

| M13[31:24] = 00h | M13[23:16] = 00h | M13[15:8] = 00h | M13[7:0] = 00h |

| M14[31:24] = 00h | M14[23:16] = 00h | M14[15:8] = 00h | M14[7:0] = 00h |

| M15[31:24] = 00h | M15[23:16] = 00h | M15[15:8] = 00h | M15[7:0] = 18h |

| Mt = SHA-1 发动机的输入缓冲区;0 ≤ t ≤ 15;32 位字,起始地址为 00h,结束地址为 0Fh。 | |||

此块的计算输出为:

A[31:0] = 42541B35

B[31:0] = 5738D5E1

C[31:0] = 21834873

D[31:0] = 681E6DF6

E[31:0] = D8FDF6AD

Maxim器件首先将这些字作为最高有效字,将独立字节作为最低有效字节(LSB)。因此,MAC 的字节级传输序列将是:

| AD F6 FD D8 | F6 6D 1E 68 | 73 48 83 21 | E1 D5 38 57 | 35 1B 54 42 |

| (五) | (四) | (三) | (二) | (一) |

时序规格

图 3 和图 4 显示了写入和读取 DSSHA1 的时序图。表6显示了使用ARM TSMC CL50G(50.018μm通用工艺)0.18V SAGE-X标准电池库(版本1q8v2004)在+3°C下从1%电源到25%电源测量的延迟值。 输出信号未加载。输入信号以 0.200ns 的标准压摆驱动,电源的 10% 至 90%。

| 参数 | 象征 | 最小值 | 麦克斯 | 单位 | ||

| CLK循环(注1) | t中青 | 12.500 | 纳 | |||

| CLK上升沿前的芯片选择设置(注1) | t.CSS | 0.229 | 纳 | |||

| CLK上升沿后芯片选择保持(注1) | t中信 | 0.000 | 纳 | |||

| CLK上升沿前的地址和数据设置(注1) | t如 | 0.229 | 纳 | |||

| CLK上升沿后的地址和数据保持(注1) | t啊 | 0.000 | 纳 | |||

| 有效输出时间至DATAO有效(注释1、2) | t坳 | 0.984 | 纳 | |||

| 停用数据[31:0] (注1) | tD | 0.984 | 纳 | |||

|

注1:这些值取决于用于实现电路的过程。显示的值仅用于示例目的,并使用 ARM 台积电 CL018G(0.18μm 通用工艺)1.8V SAGE-X 标准细胞库 2004q3v1 进行建模。ARM 部件号为 A0082。 注2:此时间定义为典型拐角的有效输出的最长可能延迟。 |

||||||

图3.写入周期。

图4.读取周期。

应用信息

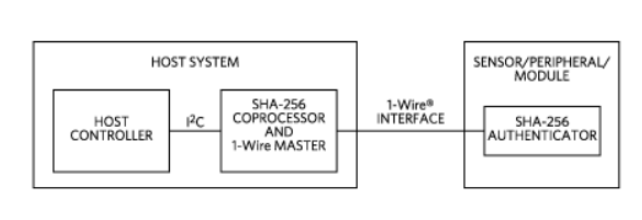

FPGA 或 ASIC 集成了设计的 DSSHA1。使用多个模块,可实现的身份验证方法使设计安全。在图5中,带有微处理器的设计模块可以将SHA-1计算卸载到DSSHA1。在图5中,设计人员首先制作一个随机生成的质询,并将DSSHA1的结果与DS28E01-100的响应进行比较。如果结果和响应匹配,则设计已经过身份验证,可以启用产品的功能。通常需要在软件和硬件的身份验证过程中进行更改。这使得成功攻击的可能性降低。

图5.典型的 FPGA 或 ASIC 应用。

物理估计

门数 6,423(NAND 2x1 用于计算)。

面积为85,470μm²,无布线。

面积为102,256μm²,布线估计值。

用于估算的库:

ARM 台积电 CL018G (0.18μm 通用工艺) 1.8V SAGE-X 标准电池库,版本 2004Q3V1。ARM 部件号为 A0082。

验证

业界通常使用以下约定来表示 IP 块的验证级别:

黄金IP一直是针对硅的。

银牌IP一直是FPGA中的硅目标。

铜牌 IP 已在具有逻辑时序收敛功能的硅模型中得到验证。

开发中的 IP 尚未得到验证。

注意:DSSHA1已获得银牌地位。

交付

DSSHA1 软件包随附:

Verilog HDL

威瑞格测试台

有关安装程序和脚本的自述文件

总结

DSSHA1可合成SHA-1协处理器是DS2460或基于微处理器的替代方案。它可以嵌入到FPGA或ASIC中,在那里它显示为存储器映射器件。对于操作,首先在 16 字输入缓冲区中填充用于 MAC 计算的数据。激活RUN_SHA信号将启动计算过程,从而将 BUSY 信号从低电平更改为高电平。在 BUSY 信号恢复为低电平后,MAC 准备就绪,可以从 5 字结果寄存器读取。主机处理器将 DSSHA1 计算的 MAC 与安全内存提供的 MAC 进行比较。如果两个 MAC 值相同,则确认真实性。

审核编辑:郭婷

-

处理器

+关注

关注

68文章

19706浏览量

232709 -

寄存器

+关注

关注

31文章

5397浏览量

122664 -

微处理器

+关注

关注

11文章

2355浏览量

83559

发布评论请先 登录

相关推荐

DS2465 SHA-256协处理器与1-Wire主机功能

如何通过使用FPGA高速实现SHA-1消息认证算法?

带有EEPROM的SHA1协处理器DS2460电子资料

基于SHA-1的邮件去重算法

为什么1-Wire SHA-1器件是安全的?

DSSHA1数据资料(英文)

Understanding the DSSHA1 Synthesizable SHA-1 Coprocessor

dssha1综合SHA-1协处理器

基于SHA-1算法的硬件设计及实现(FPGA实现)

安全协处理器/1-Wire® 主控器实现SHA-256认证

了解DSSHA1可合成SHA-1协处理器

了解DSSHA1可合成SHA-1协处理器

评论