前言

本文包括TC3xx MCU的复位系统,时钟系统和看门狗模块三部分内容。在复位系统部分主要介绍了各种复位类型。在时钟系统部分主要介绍时钟源选择,PLL倍频配置,时钟分发等内容。在看门狗模块部分主要介绍了开门狗复位的触发路径,看门狗模块的工作原理,CPU EndInit/Safe EndInit的实现原理等内容。

1.Reset

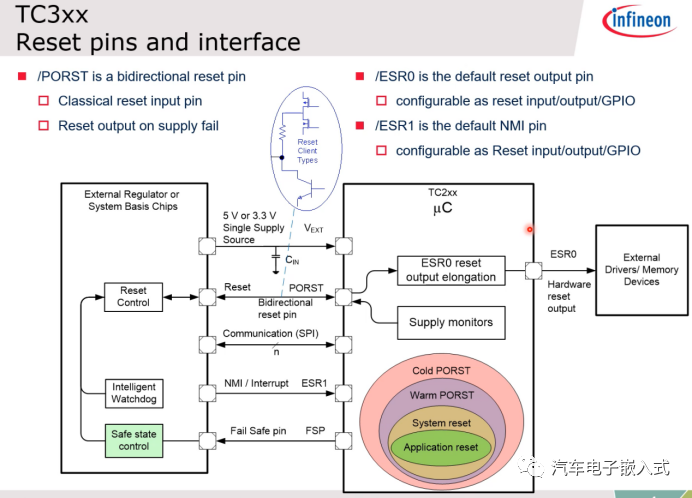

POST这个信号对于MCU来说是双向的,也就是说在上电过程中PORST是MCU的输出引脚,在完成上电过程后,PORST是MCU的输入引脚。ESR0是受PORST控制的,PORST输出低电平的时候,ESR0也会输出低电平。

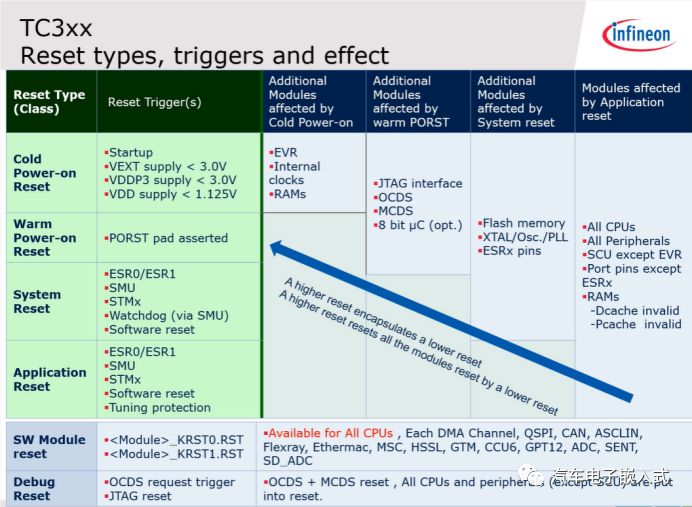

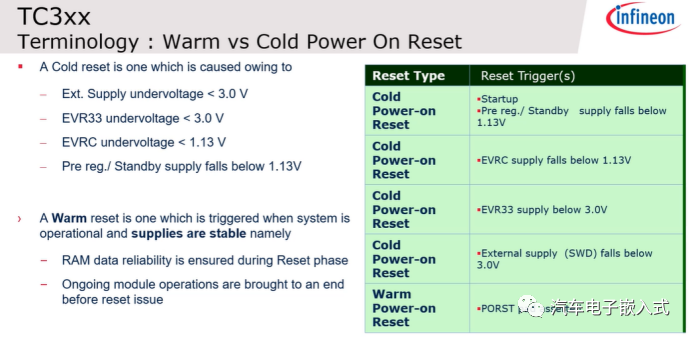

从POST引脚引起的reset就叫Warm Power On Reset,Cold PORST复位的范围最大,基本上MCU所有的模块都会Reset。

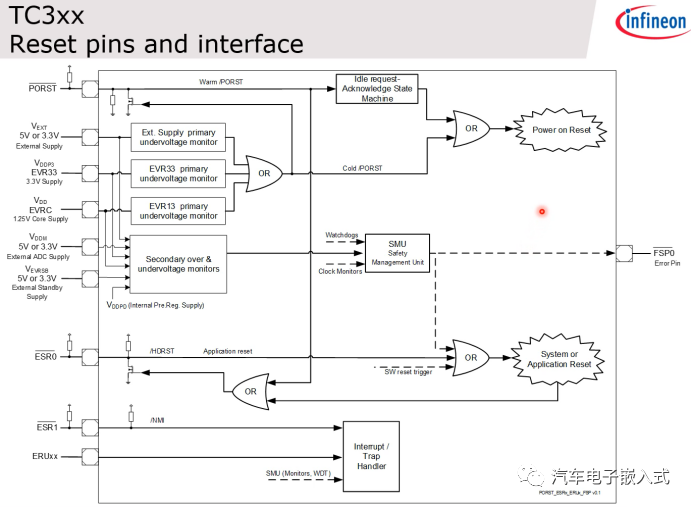

刚上电的时候,MCU的电压是从0往上升的,所以刚开始的时候MCU处于一个under voltage的状态,MCU主要监控VEXT, VDDP3, VDD三个输入电源,在刚开始的时候只要这三个电源有一个处于under voltage状态,或门(OR)就会输出点平导通MOS管,PORST就会被拉低到地。

所以在电源上升的过程中这三个电源有一个处于LBD Reset Hold(电源监控阈值)以下,MOS管就会被导通,PORST就会被一直拉低到地(输出状态,输出低电平)。

电压起来后(大于监控阈值),MOS管关断,PORST变为输入状态,如果PORST外接了一个IC或者复位按钮给了一个低电平,也会对MCU产生Reset(Warm Power On Reset)。

电压没起来前的Reset叫做Cold Power On Reset。

System or Application Reset包含的种类比较多:

1)Software reset

2)来自于SMU的reset

3)来自ESR0的复位请求

一些模块可以单独Reset(SW Module reset,Debug Reset)。

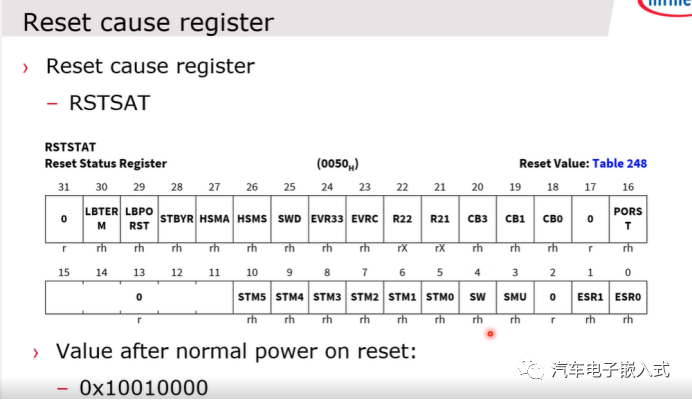

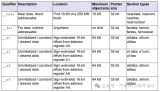

复位原因寄存器

STM0-STM5代码STM compare match造成的Reset

EVRC, EVR33,SWD代表三个低电压引起的Reset

STBYR表示Standby regulator的under voltage detect

正常情况下Reset后这个寄存器的值应该是0x10010000,也就是PORS和STBYR会被置位。

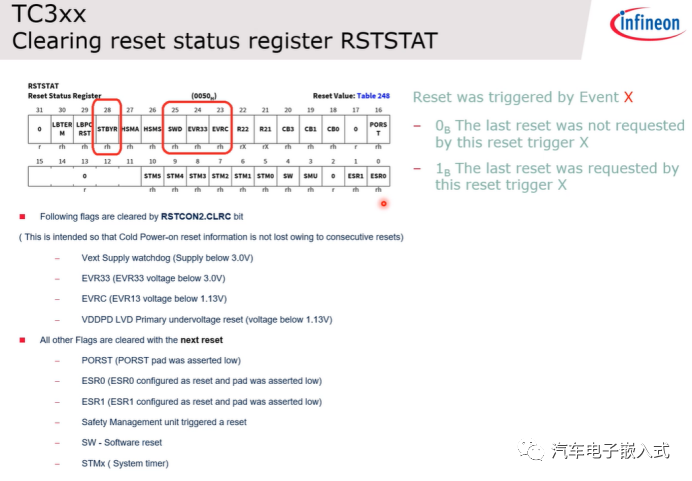

Reset status register中的关于cold power on reset的Flag需要软件清除(RSTCON2.CLRC),不然就会一直为1 。

第四种的cold reset原因是:EVR previous regulator的输出/standby supply电压小于1.13V。

Warm power on reset就是在POST变为输入状态后,外部对POST产生一个低电平引起的复位(RAM数据是可以保持的)。

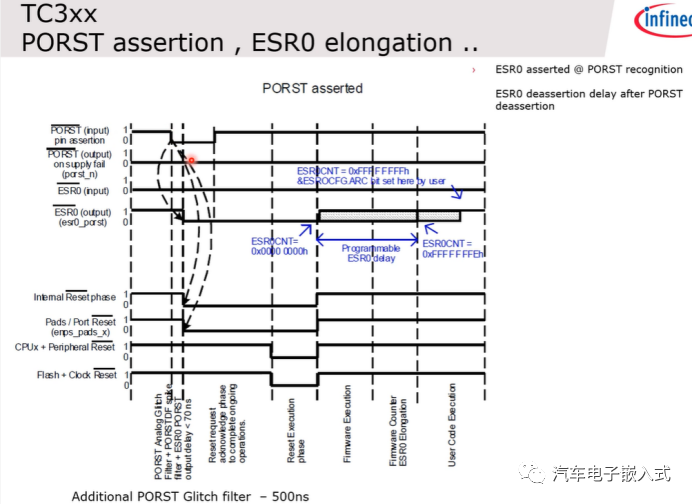

POSR和ESR0的复位时序:首先在POST(Input)上产生一个下降沿的负脉冲,通过MCU内部的一些逻辑电路产生延迟后ESR0被拉低,MCU内部的一些模块和电路(Pads/Port Reset)就会被Reset,在ESR0被拉下来以后,CPUx核、Peripheral、Flash、Clock就会发生复位,这些模块复位后ESR0就会被释放掉,从0变成1,从这个点开始,MCU的Firmware(Boot rom)开始执行(Execution)。

对于ESR0我们也可以配置一个ESR0的delay,当ESR0的delay大于Boot rom的执行时间后,Boot rom执行完准备跳转到User code前会去检测ESR0是不是被拉低,如果没有被拉低的话,就会等待ESR0被拉低后再跳转到User code。

2.Clock system

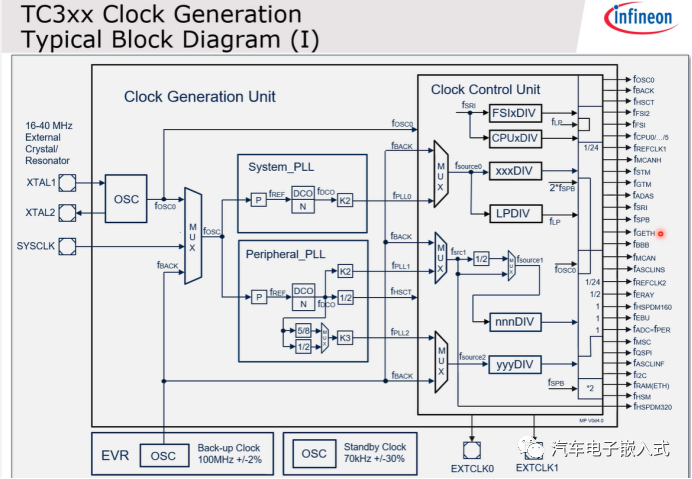

时钟选择部分:外部晶振接入作为MCU的source clock,SYSCLK这个Pin脚信号输入作为MCU的source clock,也可以使用fback这个100MHz的片内时钟作为source clock。

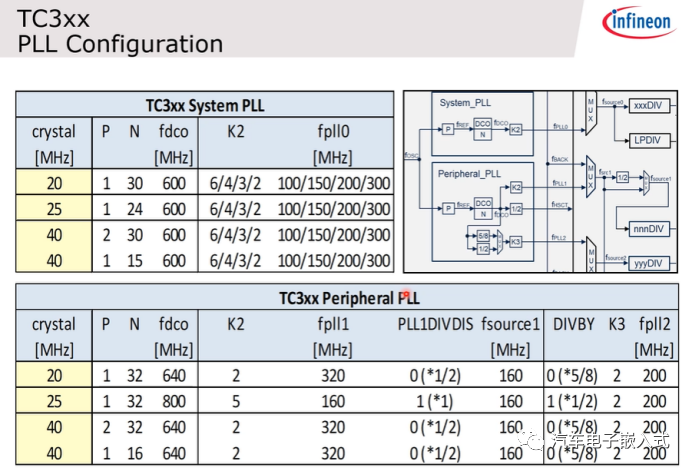

倍频PLL部分:在TC3xx里面有两个PLL:

1)System_PLL主要是倍频后给MCU的内核提供时钟。

2)Peripheral_PLL主要是倍频后通过一些分频给外设提供时钟。

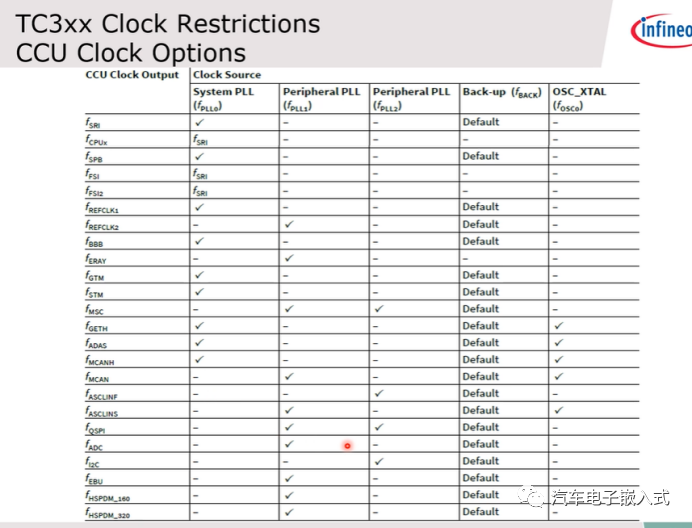

时钟分配(Distribution)部分:System_PLL产生倍频时钟fPLL0,Peripheral_PLL产生倍频时钟fPLL1和fPLL2,他们通过Clock Distribution

后通过时钟分频器可以产生各种各样的时钟频率供外设使用。

TC3xx有两种内部晶振:

1)100MHz的 Back-up Clock

2)70MHz的 Standby Clock,精度比较低,给SCR提供时钟。

EXTCLK0和EXTCLK1可以配置输出上面各种时钟用来观测。

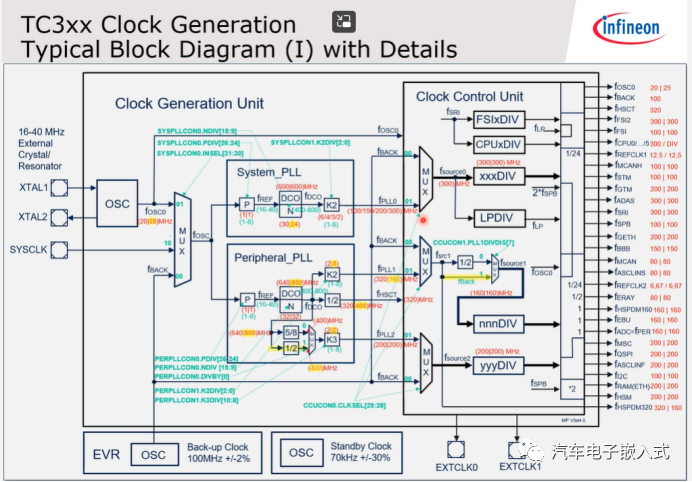

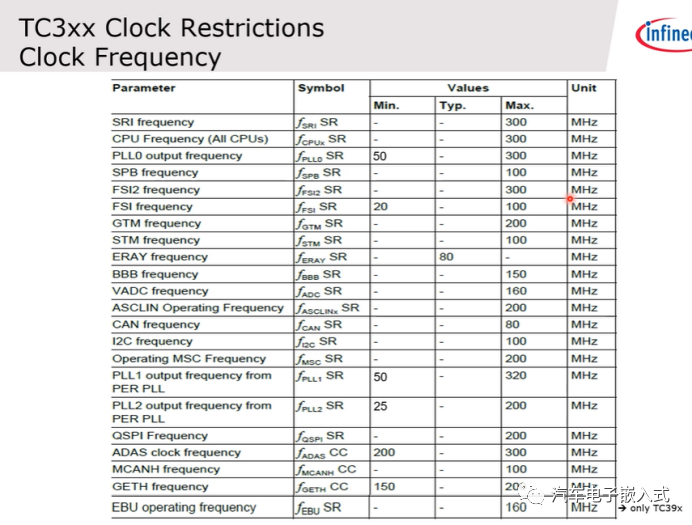

一般我们选择20MHz或者25MHz的外部晶振输入,通过System_PLL倍频后产生一个300MHz的fPLL0,fPLL0一般直接输出300MHz给CPU各个内核提供时钟。通过Peripheral_PLL产生160MHz的fPLL1和200MHz的fPLL2,再通过分配给各种外设提供时钟。

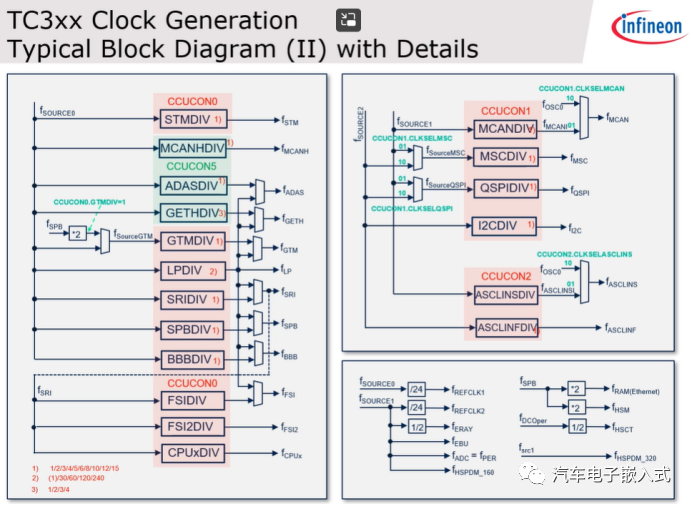

fsource0,fsource1,fsource2就是fPLL0,fPLL1,fPLL2通过各种xxxDIV分屏器产生时钟给各个模块使用,一般fCPUx是300MHz,fGETH为150MHz。

Note:fMCANH是给CAN模块的寄存器和RAM操作提供时钟的,fMCAN是给CAN波特率产生提供时钟的。

fSRI通过分频产生fCPUx给CPU提供时钟,三个CPU的时钟可以不同,CPU时钟的改变不会影响其他外设时钟。

但是注意系统时钟频率的改变会使得系统电流发生改变,影响系统的稳定性。

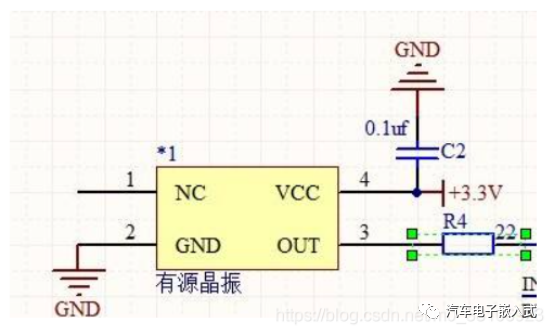

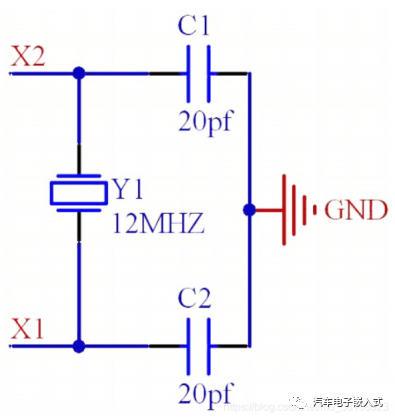

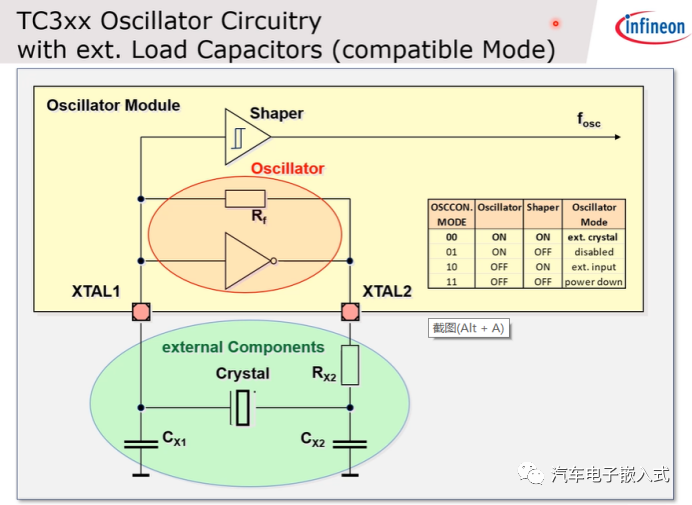

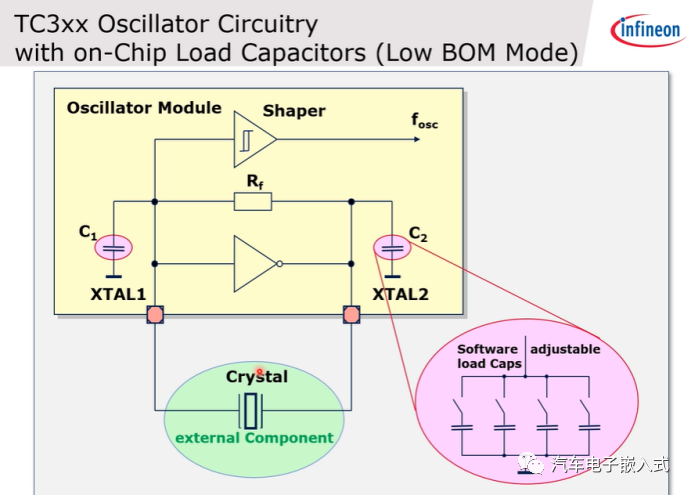

外接晶振有两种模式可以选择:

1)External Input Mode,这种模式下只需要用到输入的XTAL1就行了(XTAL2不需要),也就是在这种模式下需要接一个有源晶振。

2)External Crystal Mode,这种模式下XTAl1和XTAL2都会用到,外部接的无源晶振。

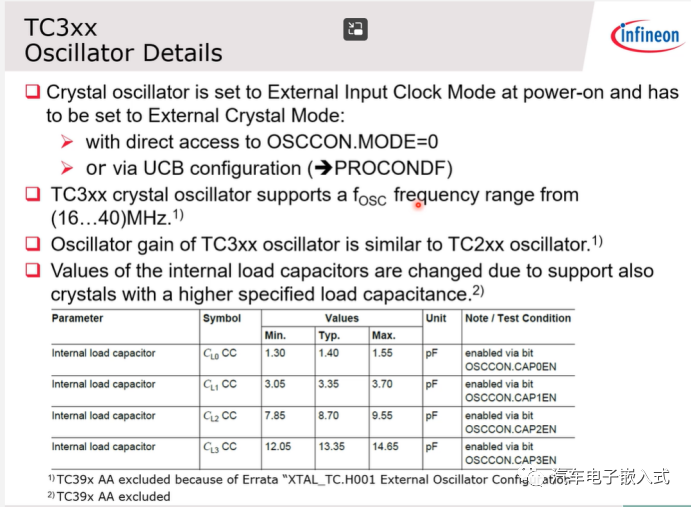

外部晶振频率范围是16MHz到40MHz。

在TC3xx里面还有有load capacitor(负载电容),也就是晶振的负载电容可以不用外部接,可以通过配置寄存器使用内部负载电容。

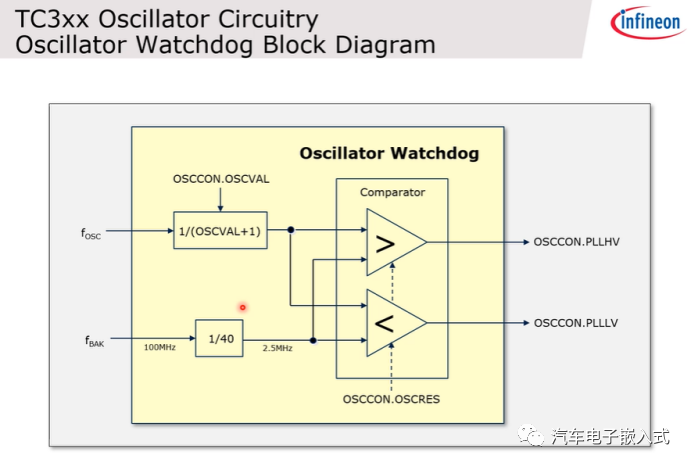

Oscillator Watchdog

在System_PLL里面有一块电路叫Oscillator Watchdog,这块电路主要用来检测输入的晶振在一定的范围里面。它的检测方法是通过内部的100MHz的fBAK通过1/40分频产生一个2.5MHz的Reference Clock,以这个Reference Clock对fosc经过1/(OSCVAL+1)分频后的时钟进行Monitor,如果对比后在一个Tolerance range范围外的话,就会置位OSCCON.PLLHV或者OSCCON.PLLLV两个寄存器位域。

。

。

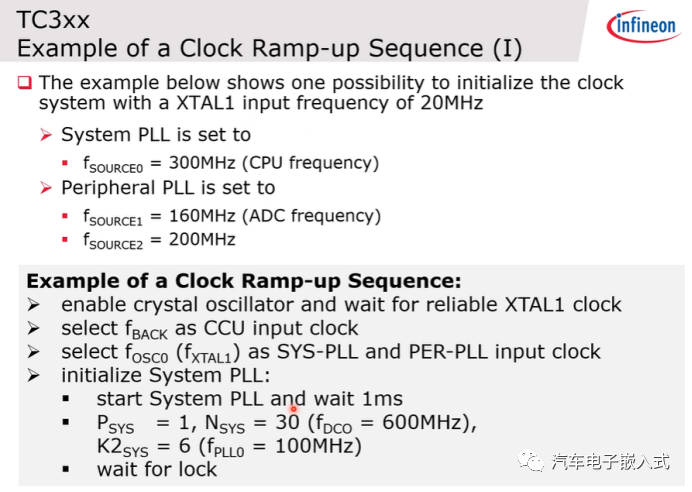

一般都是使用外部20MHz的输入晶振以及分频/倍频参数来参数CPU和外设时钟。

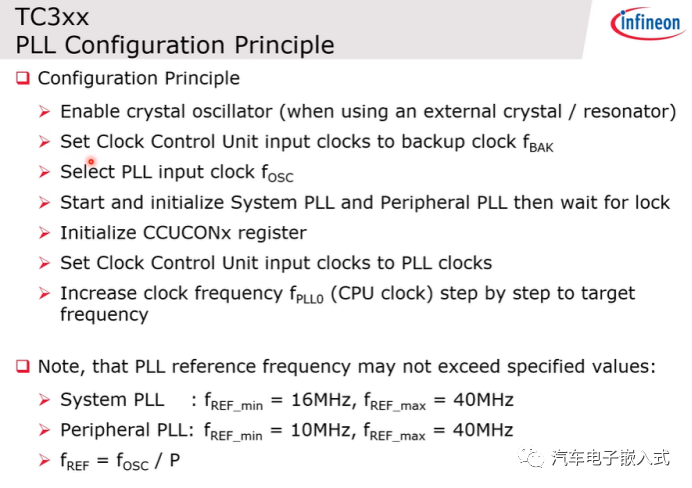

PLL配置流程:

1)使能使用外部晶振

2)Clock Control Unit的Input Clock选择fBAK,Clock Control Unit已经属于Clock Distribution了,没有选择fPLL而是选择fBAK作为它的输入时钟,所以这个时候CPU和Peripheral都是基于fBACK的。

3)选择fosc作为PLL的输入时钟。

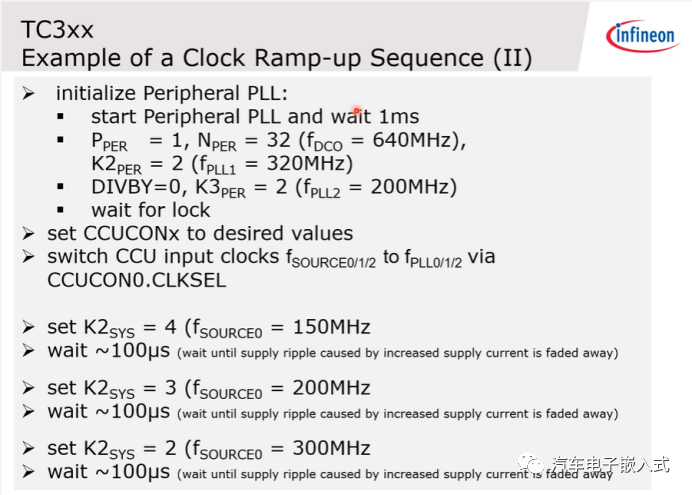

4)设置一个初始的PLL配置参数,比如我们先把System_PLL倍频到100MHz,Peripheral_PLL可以直接倍频到最终频率,比如Peripheral_PLL1到320MHz,Peripheral_PLL2到200MHz。

5)设置分频寄存器。

6)把Clock Control Unit的Input Clock选择从fBAK切换到PLL。

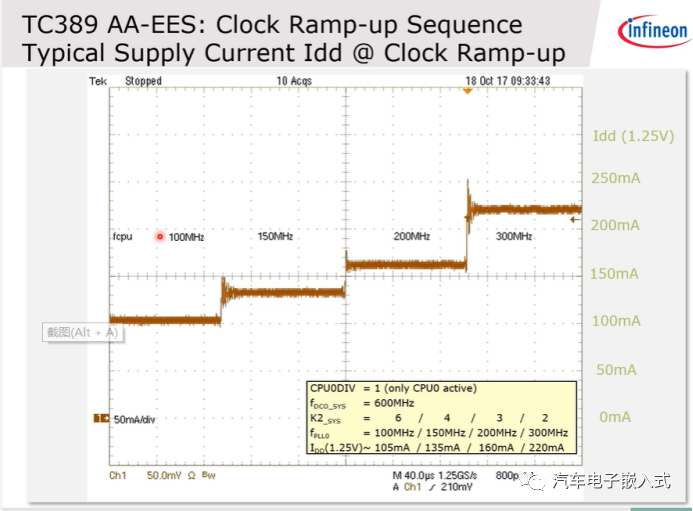

7)System_PLL也就是fPLL0慢慢从100MHz倍频到300MHz,是的系统的电流平稳上升。

CPU时钟慢慢倍频上去,让电流的变化平滑上升。

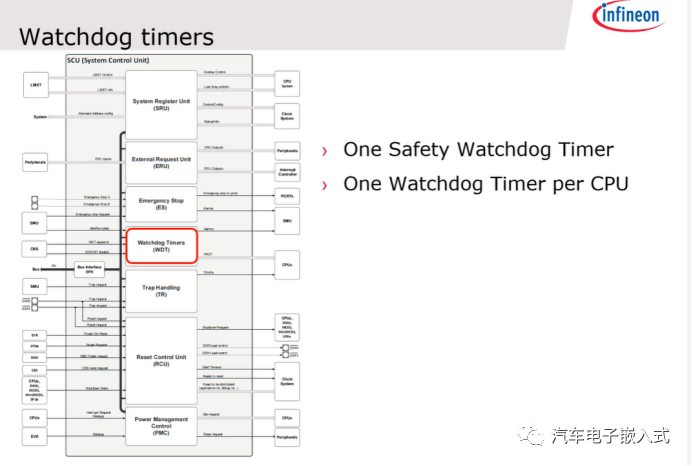

3.Watchdog

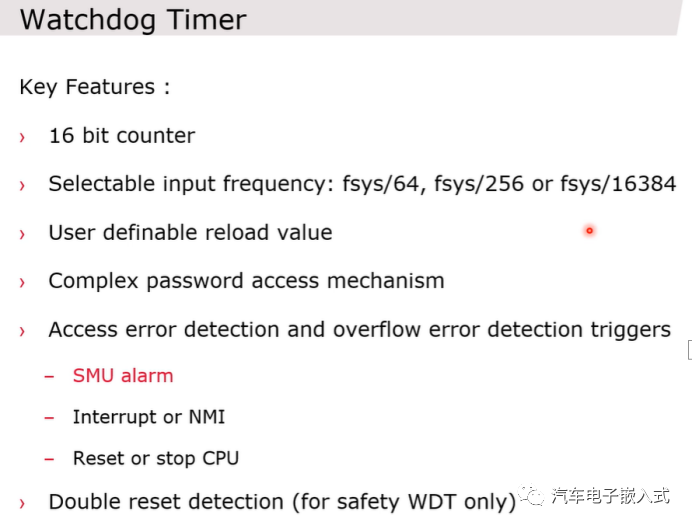

TC3xx芯片的Watchdog在SCU模块里面,Watchdog分为两种,一种是CPU Watchdog,一种是Safety Watchdog,每一个CPU都有自己的CPU Watchdog。

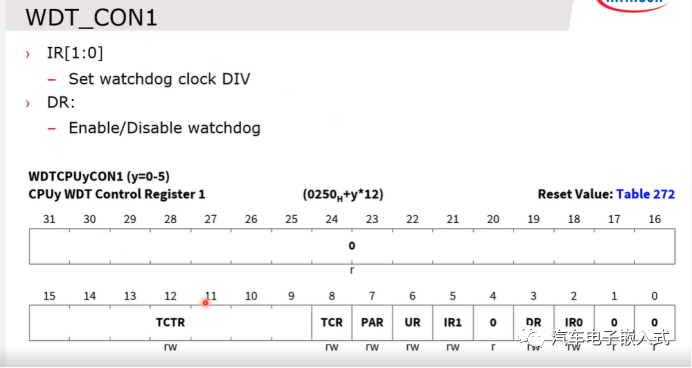

每个Watchdog有三个Register,WDTxCon0,WDTxCon1,WDTxSR。

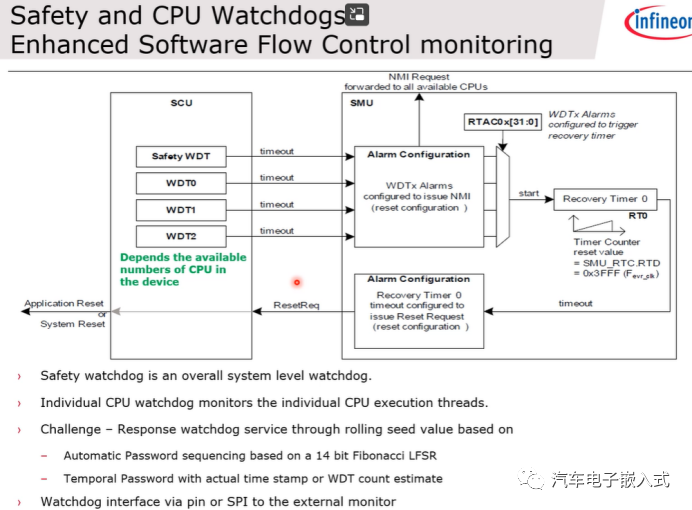

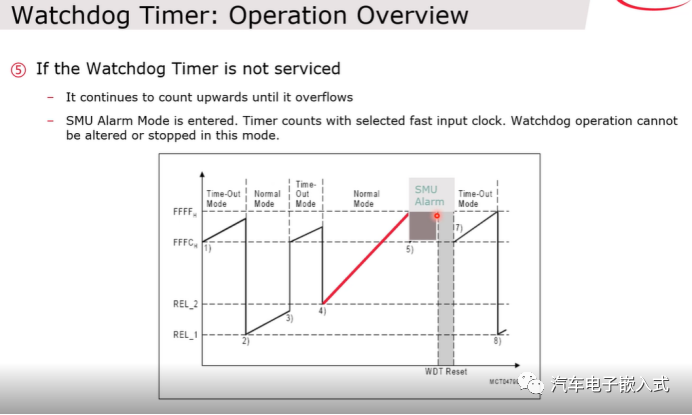

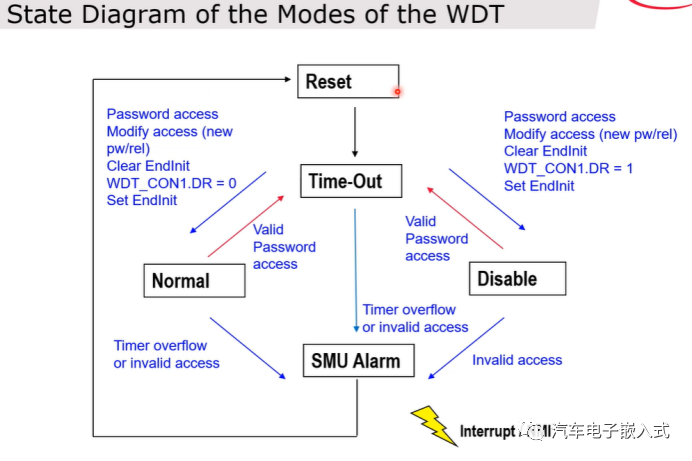

Watchdog一般情况下如果Watchdog time溢出了就会产生一个watch dog reset,在TC3xx中Watchdog的Timeout并不会直接触发Reset,而是经过配置SMU后会触发SMU里面的一个Recovery Timer启动,Recovery Timer的Timeout时间可以配置,单Recovery Timerout后就会产生一个Alarm,如果这个Alarm配置为Reset信号的话,就会触发Reset。

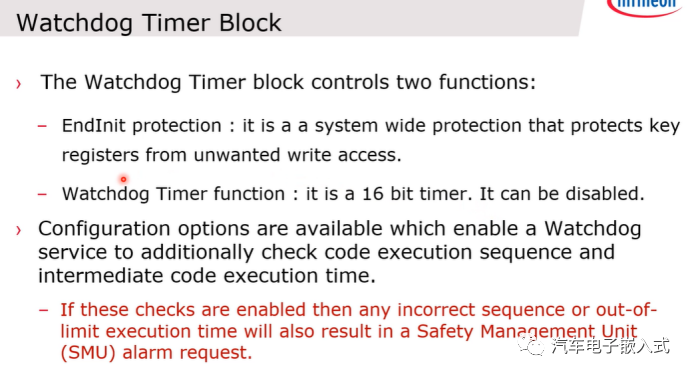

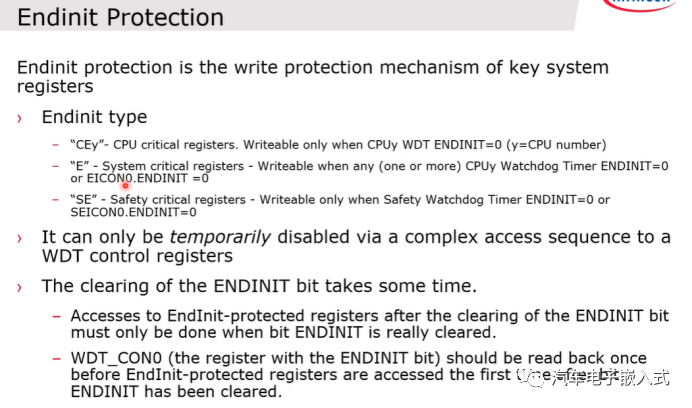

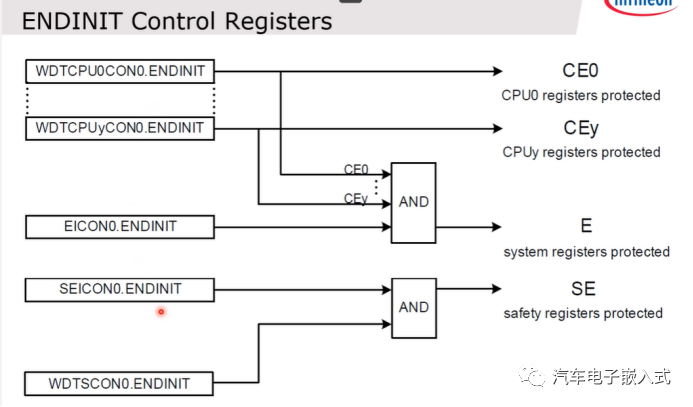

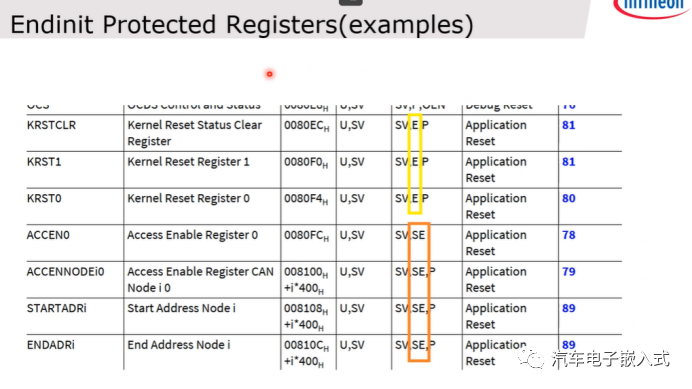

EndInit的保护有三种:

1)“CE”保护,只有把每一个CPU的ENDINIT设为0后,这个CPU的critical registers保护才被解除(可写)。

2)“E”保护,任意一个CPU的ENDINIT设为0后,所有CPU的system critical registers保护就解除了。

3)“SE”保护,Safety Watchdog的ENDINIT设为0后,Safety EndInit的保护就解除了。

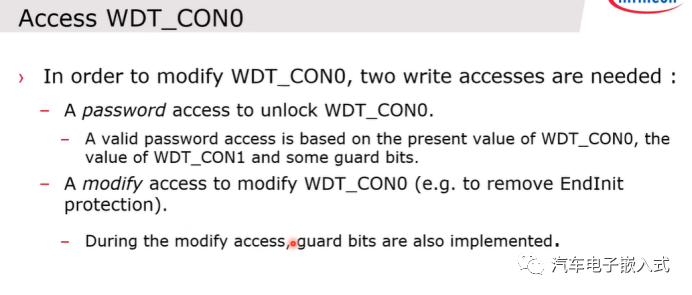

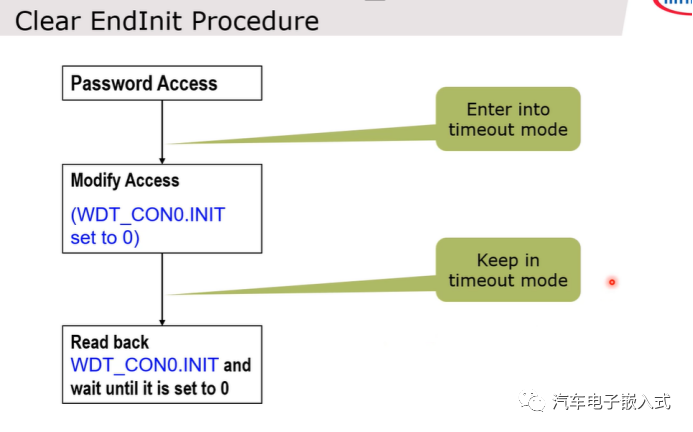

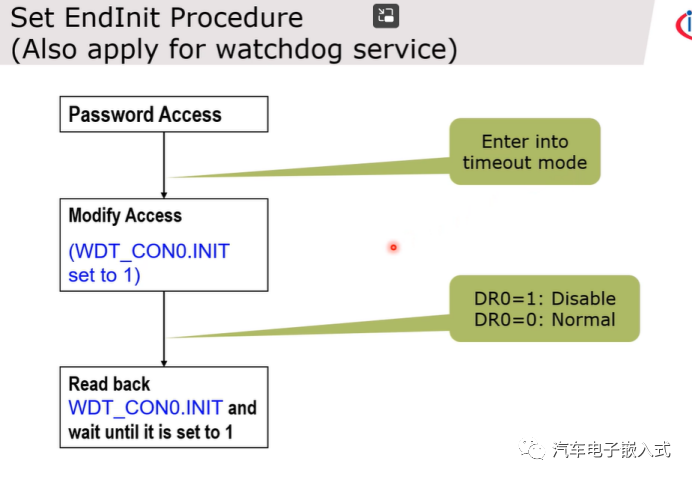

ENDINIT设置为0的操作,需要一套较为复杂的操作序列。

ENDINIT置为0需要一段时间,只有等到ENDINIT真的为0后才能执行往下的操作,不然可能会产生异常。

EICON0和SEICON0是两个Global的ENDINIT保护寄存器,如果不想改变Watchdog CPUx或者Safety Watchdog的ENDINIT值,但是又想解除保护,就可以使用Global的EICON0和SEICON0(前提是EndInit的保护等级是“E”或者“SE”)。

对于保护等级为“E”或者“SE”的寄存器,在操作它之前需要先解除EndInit保护。

fsys类似fspb,类似于外设总线频率。

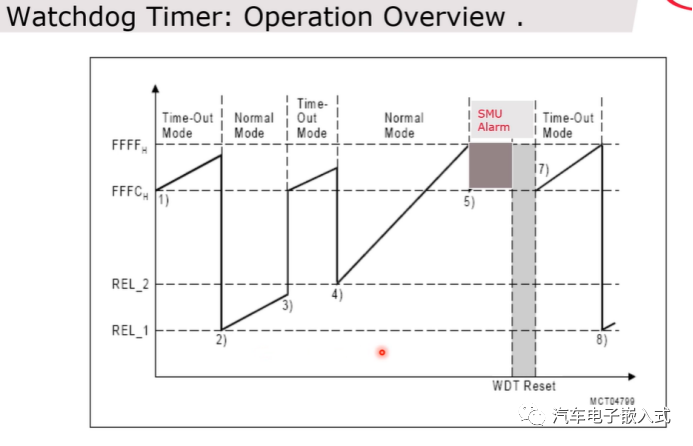

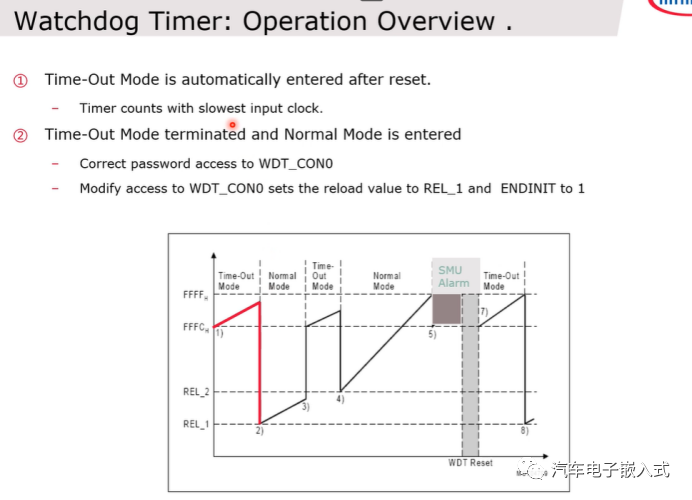

复位以后CPU的Watchdog默认是处在Time-Out Mode下的,WDT在Time-Out Mode下就会从0xFFFC开始往上计数,如果计数到0xFFFF就会溢出,如果在计数到0xFFFF之前对WDT_CON0进行了password access后对WDT_CON0进行了Modify access,重新对WDT进了reload value到REL_1值(写寄存器前ENDINIT值改为1了,也就是先要介绍ENDINIT保护),这样WDT从Time-Out模式切换到了Normal Mode,这个时候WDT开始从REL_1值晚上计数。

Note: 后面会介绍password access和Modify access

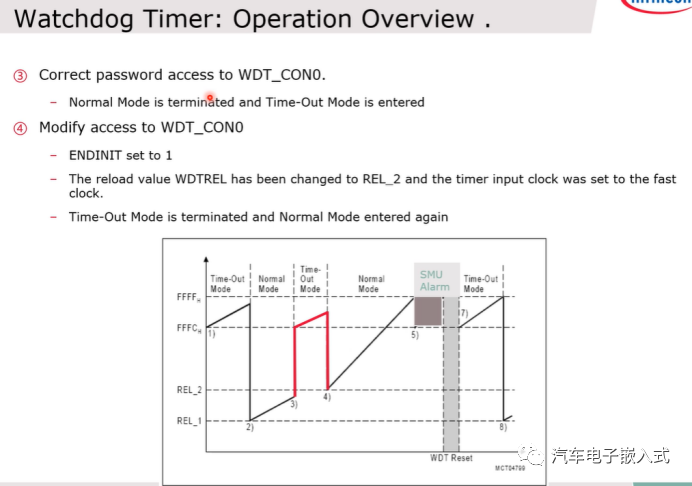

在上图中的3)的地方对WDT_CON0进行了password access,WDT就会切换到Time-Out Mode,WDT又从0xFFFC开始计数,如果在4)这个点,又对WDT_CON0做了password access就会切换WDT到Normal Mode,同时对WDT_CON0做了一次Modify access后,WDT从REL_2开始计数。

计数到0xFFFF后WDT就溢出了,触发SMU的Timeout的Alarm,这个Alarm会触发SMU里面的一个Recovery time进行计数,Recovery time也timeout后就会产生一个SMU的reset。

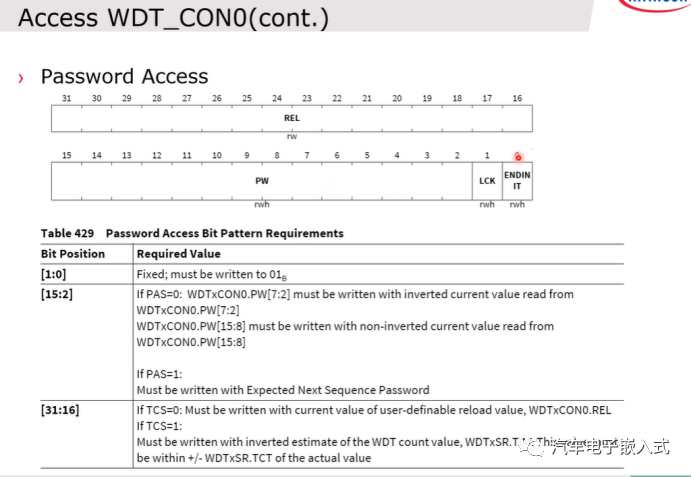

Password access的条件是LCK为0,ENDINIT为1。WDTxCON0.PW[7:2]写入当前WDTxCON0.PW[7:2]值的反转值,WDTxCON0.PW[15:8]写入当前WDTxCON0.PW[15:8]值,这样Password access就解锁了。

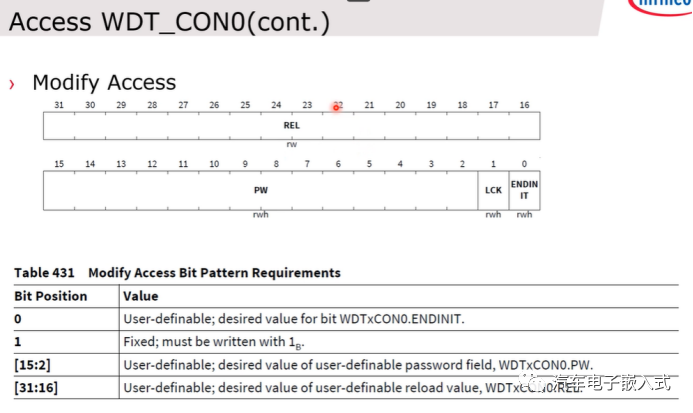

如果Password成功以后,就相当于这个寄存器被解锁了,然后就可以在PW中填入新的Password,REL和ENDINIT也可以写入新的值,当完成Modify access后,这个寄存器就又被lock住了,如果要改它就需要再来一次password access。

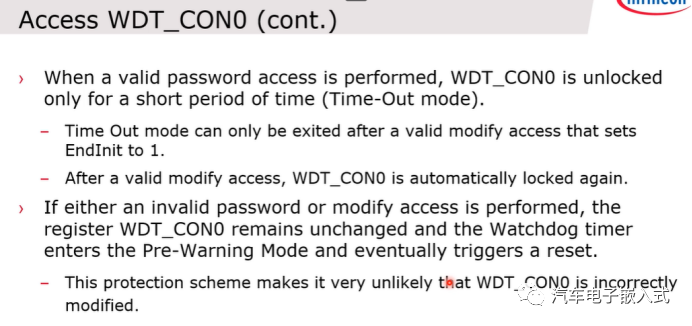

当WDT_CON0进行了一次Password Access之后WDT的状态会切换为Time-Out mode,也就是说接下来操作这个寄存器的时间必须要比较短,就是要在Watchdog Timeout之前完成操作。

Set EndInit的Modify Access动作会设置WDT_CON0.INIT为1,WDT的Reload timer会重新Reload一次,也就是和Watchdog的喂狗操作是一样的。

审核编辑:刘清

-

MOS管

+关注

关注

108文章

2452浏览量

67775 -

pll

+关注

关注

6文章

781浏览量

135369 -

MCU芯片

+关注

关注

3文章

255浏览量

11669 -

看门狗模块

+关注

关注

0文章

3浏览量

1454 -

时钟系统

+关注

关注

1文章

101浏览量

11817

原文标题:简析TC3xx Rest/Clock/Watch模块

文章出处:【微信号:eng2mot,微信公众号:汽车ECU开发】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

优化TC3xx系统运行效率的策略

请问AURIX TC3xx tricore架构下浮点运算和将浮点数小数点去掉变成整数来计算哪种方式更加节省算力?

TC367 SYS RESET/APP RESET之后RAM不会清除怎么解决?

ERAY (FlexRay) 模块卡在INTEGRATION_LISTEN状态,为什么?

TC2XX/3XX多核断点设置无效的原因?

aurix的TC397的上电时序要求是怎样的呢?

TC3XX系列IOM模块ECMSELR寄存器中的CTS和CES有什么区别?

TSIM是否支持TC3xx系列在没有硬件的情况下调试应用程序?

TC3xx的HSM中有没有单调计数器?

深入解析TC3xx芯片中的SMU模块应用

GCC和TASKING有什么区别?应该为AURIX™ TC3xx选择什么?

深入解析TC3xx芯片中的SMU模块应用

一文简析TC3xx Rest/Clock/Watch模块

一文简析TC3xx Rest/Clock/Watch模块

评论