我们一直在我们的私人咨询业务上花费大量时间,试图为各种逻辑和内存工艺节点的工具类型建立一个半导体工厂资本支出的模型。我们正在密切跟踪的项目是光刻支出如何在各种节点收缩之间演变。我们的起点是28nm,它从第一代 FinFET 节点发展到第一个 EUV 节点,再到第一个 Gate All Around Nanosheet 节点(3nm 和 2nm)。

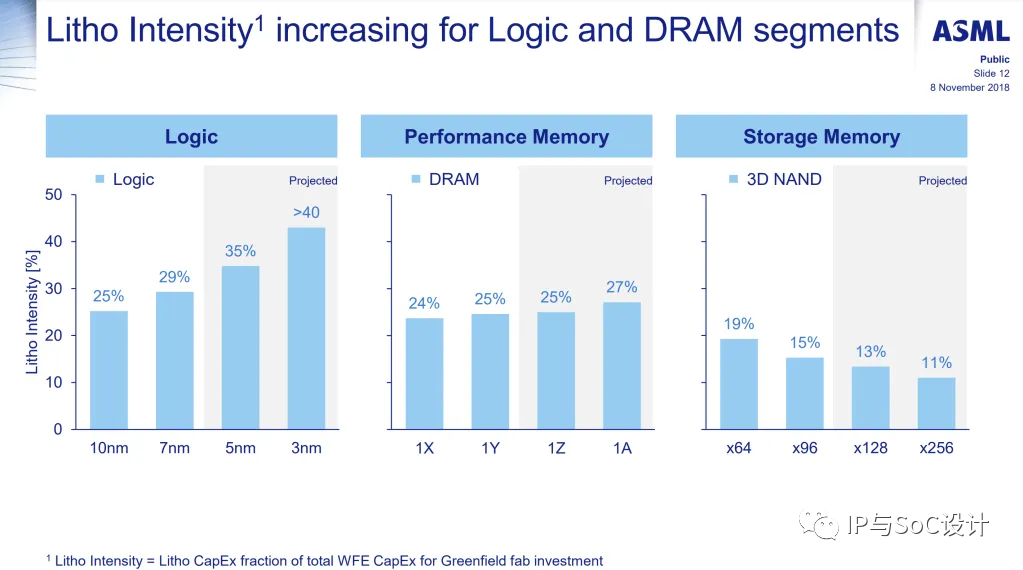

根据检查的节点不同,在光刻技术上花费的百分比会有很大差异。这里有一张关于该主题的旧 ASML 幻灯片。它似乎排除了很多各种晶圆厂的资本支出,但看起来很有趣。

光刻支出相对于沉积和蚀刻的演变对 ASML、Lam Research、Applied Materials、Tokyo Electron等公司的相对绩效有很大影响。在我们研究这个问题时,最重要的一个方面是每个DUV或EUV层的曝光成本,以及它们的数量。顺带一提,一些卖方分析师试图将每个节点的 EUV 曝光数计算到他们的 ASML 模型中,但结果大错特错。

此时您可能在想,这太棒了,但这与模具尺寸有什么关系?

传统观点认为,更大的模具成本成倍增加。我们认为我们所有的读者都知道这一点。较大的裸片尺寸会增加成本,因为缺陷更有可能影响较大的裸片。这是小芯片革命背后的主要推动力之一。我们在使用 AMD 小芯片数据中心 CPU 与英特尔单片数据中心 CPU 的高级封装系列中对此进行了比较。

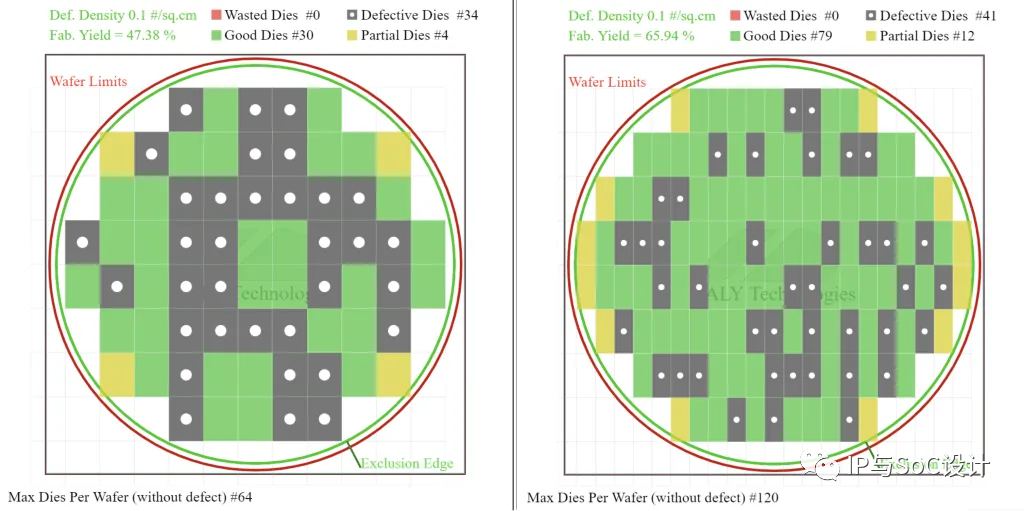

这种传统的思维过程可能是完全错误的。让我们使用一个带图片的假设示例来解释更小的芯片制造成本更高的原因。假设一个无晶圆厂芯片设计团队正在决定是制作一个大型单片芯片还是制作 2 个小芯片 MCM 设计。左边是一个装满 25 毫米 x 32 毫米、800 毫米 2 芯片的晶圆。

右边是一个装满 13.5 毫米 x 32 毫米、432 毫米 2 芯片的晶圆。2 个小芯片设计的每个小芯片仅多 8% 的硅,这与 AMD 当前的小芯片 CPU 的开销相似。尽管两个节点都被模拟为具有相同的每平方厘米缺陷数 (0.1),但两种设计中没有缺陷的裸片数量差异很大。

单片设计每个晶圆有 30 个好管芯,而小芯片 MCM 设计每个晶圆有 79 个好管芯。假设所有有缺陷的模具都必须扔进垃圾桶。如果没有die yield harvesting,设计公司单晶设计只能卖30个产品,但是chiplet MCM设计可以卖39.5个。

通过使用小芯片和 MCM,每个晶圆的产品数量增加了约 30%。如果假设每个晶圆的成本为 17,000 美元,那么无缺陷硅芯片的单片成本为 567 美元,小芯片 MCM 的成本为每个无缺陷硅芯片 215 美元,而 2 为 430 美元。显然,设计团队应该选择小芯片 MCM 选项,如果我们忽略任何功耗、芯片收集和封装成本差异,因为它们可以为每个产品节省 136 美元!

如果我们告诉您这种小芯片 MCM 设计更昂贵怎么办?

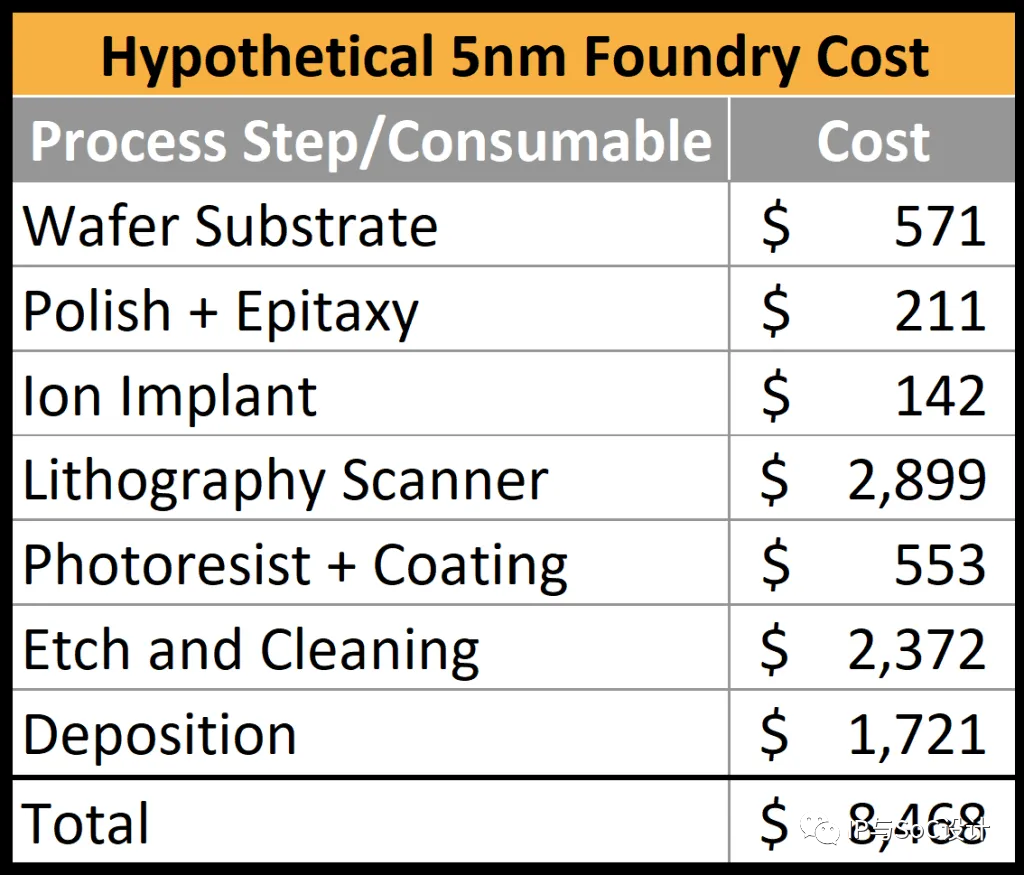

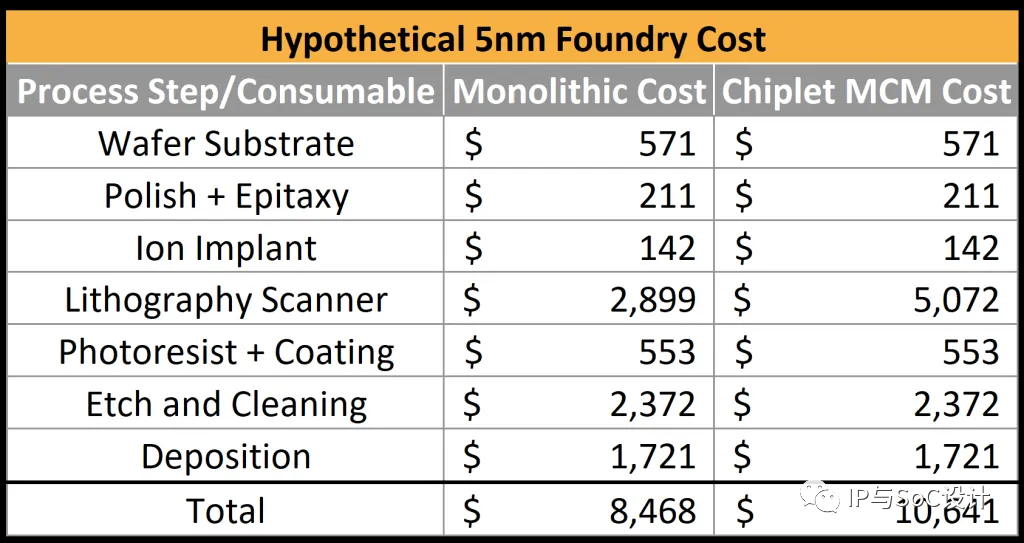

你可能不相信我们,但让我们来看看如何。在这个假设场景中,假设产品使用代工 5nm 级节点。假设这家代工厂以约 50% 的毛利率以约 17,000 美元的价格出售这些晶圆。以下是按消耗品或工艺步骤细分的成本,包括工具折旧、维护成本、电力使用、分配的员工成本等。

这些数字与我们的实际估计有很大偏差,但一致的是,最大的成本中心是光刻。它几乎占加工晶圆成本的 1/3。光刻成本只是一个平均假设。根据您选择的模具尺寸,它可能会有很大差异。

光刻工具不分青红皂白地曝光晶圆。它需要知道哪些地方可以用光刻曝光,哪些地方不可以曝光。光掩模包含芯片设计并阻挡光线或允许光线通过以曝光晶圆。领先的 5nm 代工厂设计将有十几个 EUV 光掩模和另外几十个 DUV 光掩模。这些光掩模中的每一个都对应于晶圆上的一个特征或特征的一部分,并且对于每个芯片设计都是唯一的。通过光刻和所有其他工艺步骤的循环,这家代工厂可以在大约 10 周的时间内在晶圆上制造出特定的 5 纳米芯片。下面是 DUV 光掩模的图片。

标准光掩模为 104 毫米 x 132 毫米。然后,光刻工具通过光掩模进行曝光,以 4 倍的缩小率在晶圆上印刷特征。该区域为 26 毫米乘 33 毫米。大多数设计并不完全符合 26 毫米 x 33 毫米。

标线利用率的概念出现了。

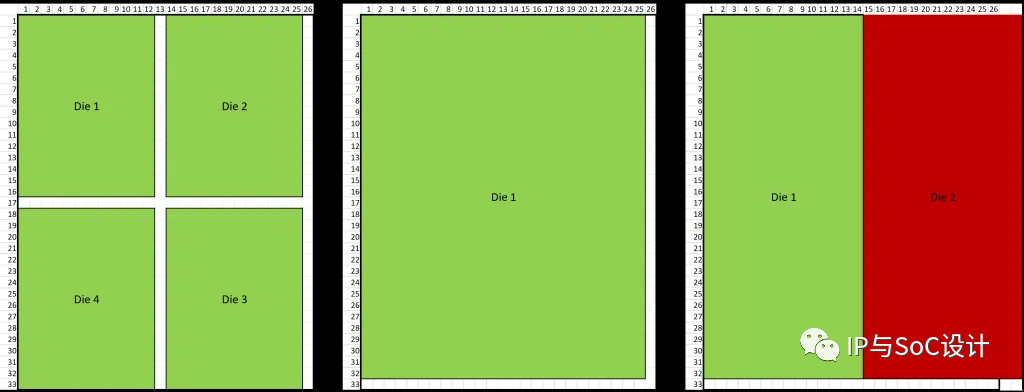

通常,芯片设计较小,因此光掩模可以包含多个相同的设计,如上图所示。即便如此,大多数设计也不会完全适合 26mm x 33m 的区域,因此通常光掩模的一部分也不会曝光。

如果一个芯片是 12 毫米 x 16 毫米,我们可以在每个标线片上安装 4 个芯片。这里的分划板利用率非常高,因为只有一小部分分划板没有暴露。对于 25mm x 32mm 的单片芯片,我们不会在狭缝和扫描方向上使用 1mm。十字线的利用率同样很高。对于我们的 chiplet,尺寸为 13.5mm x 32mm。这个模具太大,不能并排放置 2 个模具,因此每个模具只能有 1 个模具。下图显示了上述示例的一些可视化效果。

你可能会问,光罩利用率低有什么问题?

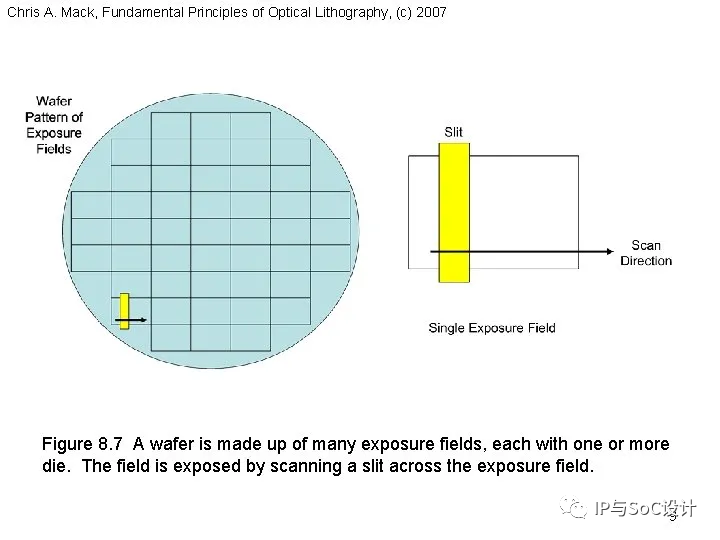

这成为一个巨大的成本问题,因为当我们缩小到晶圆级处理过程时会发生什么。放置在光刻工具和工具中的晶圆一次暴露晶圆 1 的光罩区域的一部分。如果使用完整的 26mm x 33mm 掩模版,光刻工具以最少的步数跨过 300mm 晶圆,宽 12 个掩模版,高 10 个掩模版。如果光罩利用率较低,则工具必须在每个方向上多次跨过晶圆。

将每个晶圆上的 25mm x 32mm 单片芯片与 13.5mm x 32mm 小芯片 MCM 设计进行比较时,我们需要跨过晶圆 1.875 倍!

现代 DUV 和 EUV 工具具有狭缝和扫描。狭缝 (26mm) 是曝光的部分,它扫描 (33mm) 整个标线板区域。Andreas Schilling 分享的下方这张来自 ASML 的关于 High-NA EUV 的 gif 展示了这个概念。对于 High-NA EUV,狭缝最大仍为 26mm,扫描减半。生产力的主要损失在于晶圆台必须移动多快。

想象一下,如果相反,狭缝减半。吞吐量影响会大得多。

将我们的单片设计与小芯片 MCM 设计进行比较时,我们的光刻工具时间显着增加,因为晶圆必须扫描 1.875 倍。这是因为狭缝的很大一部分没有得到充分利用。虽然在晶圆装载时间方面仍有一些效率,但光刻工具的大部分成本与扫描时间有关。因此,每片晶圆的内部成本显着上升。

在这种假设情况下,代工厂现在每片晶圆的光刻成本要多花费 2,174 美元。这是一个巨大的成本增加,代工厂无法承受已经拥有非常紧张的利润交易的大批量客户。假设代工厂按利润定价,因此无论设计如何都保持 50% 的毛利率。

未充分利用掩模版上的狭缝导致的成本增加意味着代工厂不会以 17,000 美元的价格出售这些晶圆以维持 50.2% 的毛利率。相反,他们将以 21,364 美元的价格出售这些晶圆。单片产品的无缺陷硅成本仍为 567 美元。每个芯片的无缺陷硅成本不是 215 美元,而是 270 美元。每件产品不再是 430 美元,而是 541 美元。

Chiplet 还是 Monolithic 的决定现在变得更加困难。一旦您考虑了封装成本,单片芯片很可能制造起来更便宜。此外,小芯片设计还存在一些电力成本。在这种情况下,构建大型单片芯片绝对比使用 chiplet/MCM 更好。

这个例子是最坏的情况选择来展示分划线利用率的点。这种简单化和假设性的分析也有很多注意事项。此外,与其他工艺步骤相比,5nm 之前以及我们进入全栅时代之后的大多数其他工艺节点的光刻成本更低。大多数小芯片架构可能会提高光罩利用率而不是降低它。

审核编辑:刘清

-

amd

+关注

关注

25文章

5505浏览量

134773 -

半导体

+关注

关注

335文章

27851浏览量

223994 -

扫描仪

+关注

关注

2文章

428浏览量

68023 -

EUV

+关注

关注

8文章

609浏览量

86208 -

ASMI

+关注

关注

0文章

8浏览量

3643

原文标题:博文:裸片尺寸和光罩难题——光刻扫描仪吞吐量的成本模型

文章出处:【微信号:IP与SoC设计,微信公众号:IP与SoC设计】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

如何将三维激光扫描仪与BIM结合使用

三维激光扫描仪使用技巧 三维激光扫描仪测量精度分析

三维激光扫描仪应用领域 三维激光扫描仪与传统测量工具比较

大幅扫描仪扫描地图怎么操作

TMS320C6472/TMS320TCI6486的吞吐量应用程序报告

蔡司激光三维扫描仪有效扫描金属材料

何为电磁干扰(EMI)扫描仪,哪里需要它?

光刻扫描仪吞吐量的成本模型

光刻扫描仪吞吐量的成本模型

评论