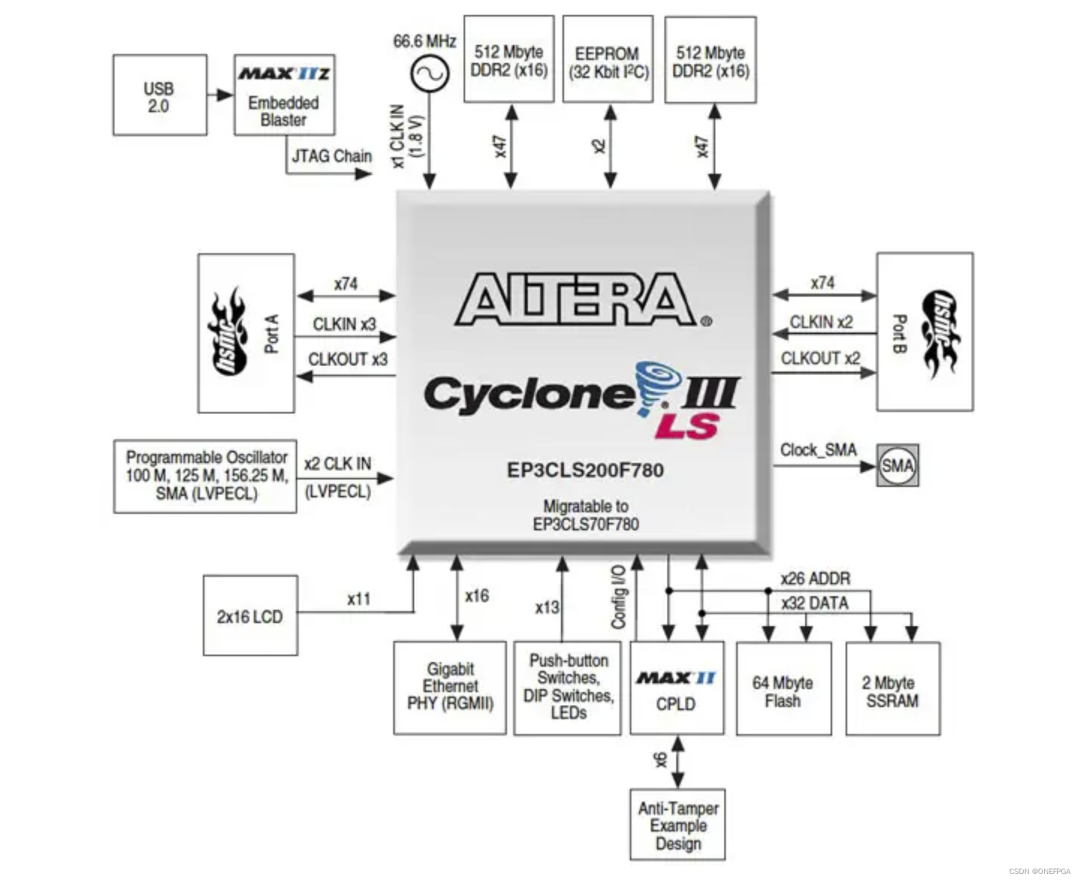

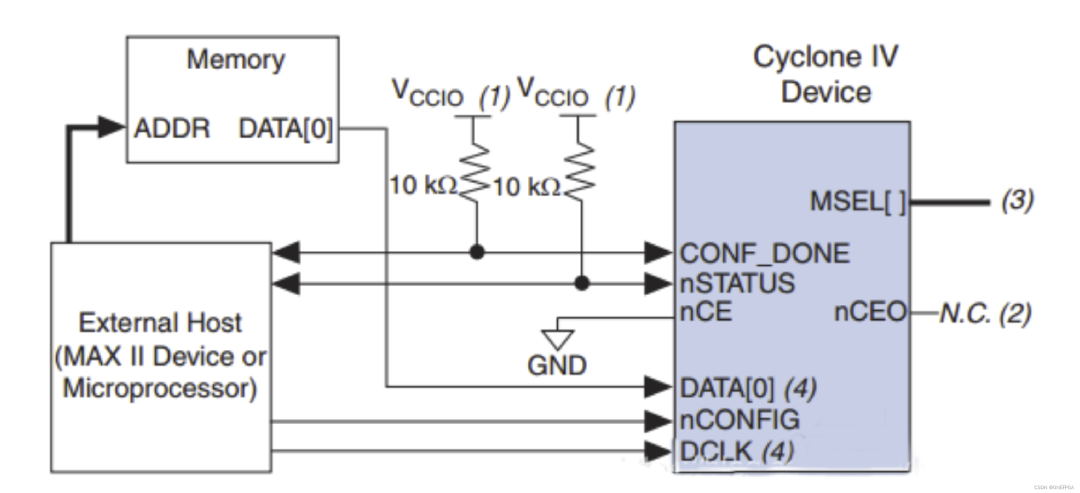

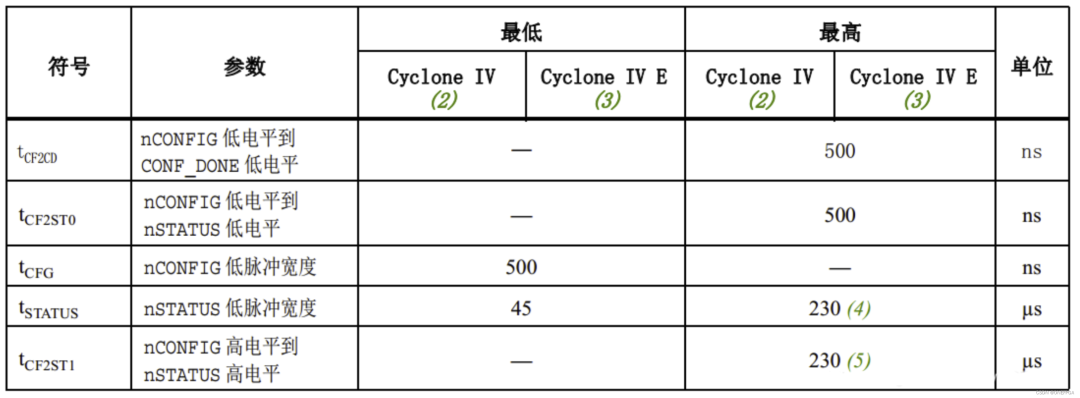

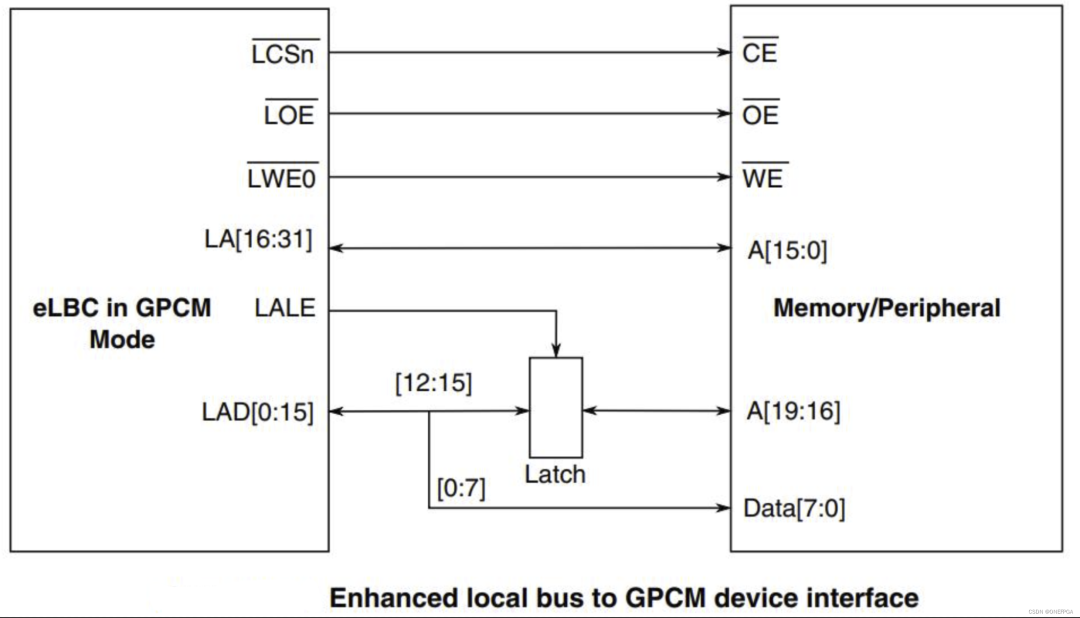

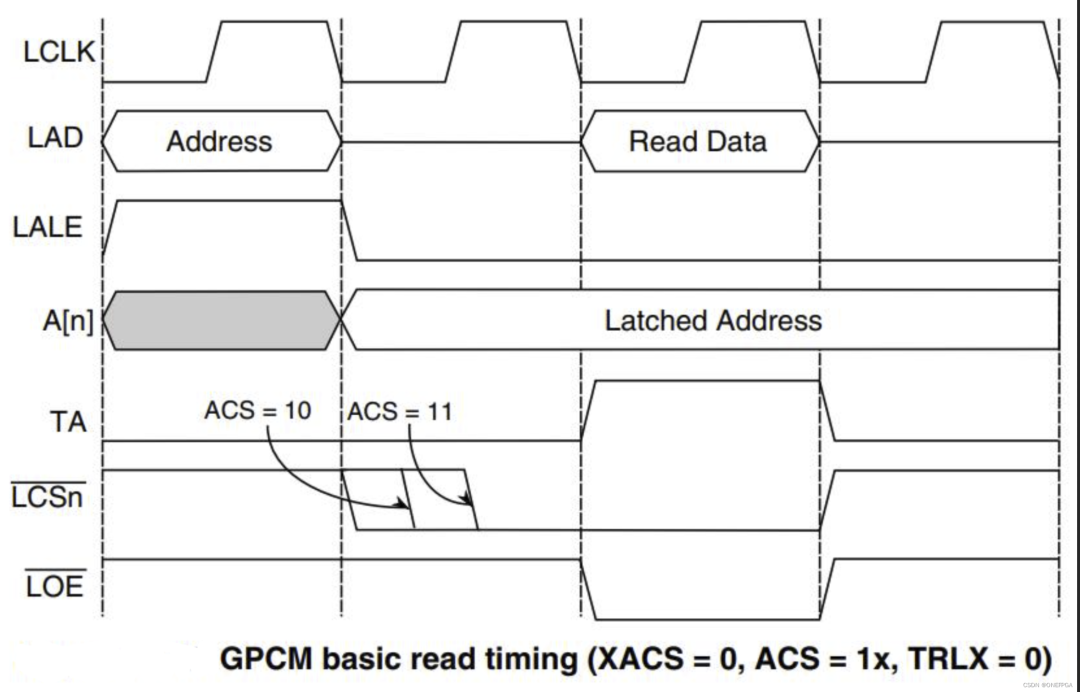

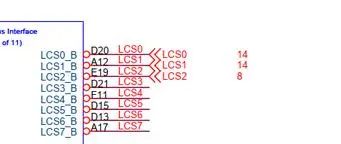

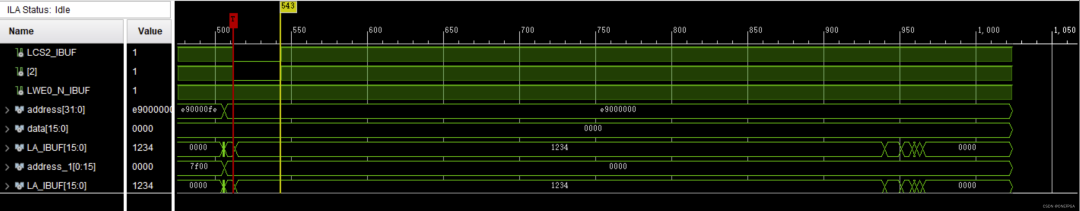

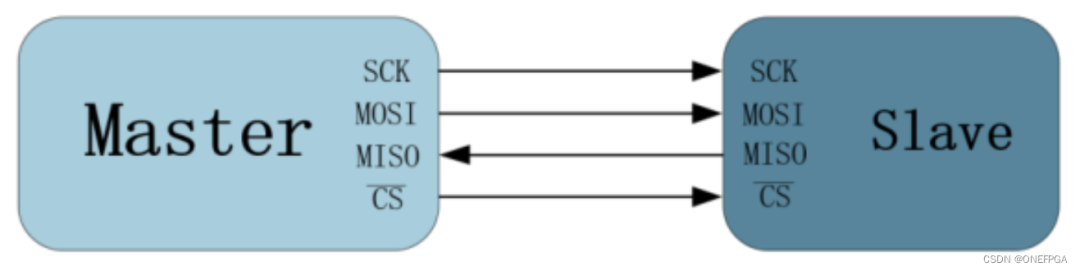

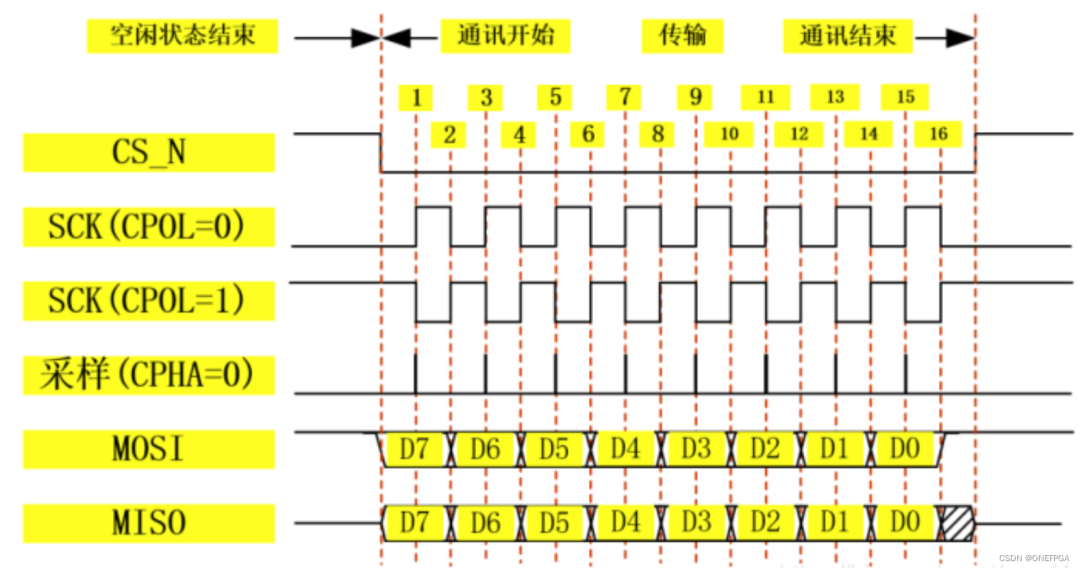

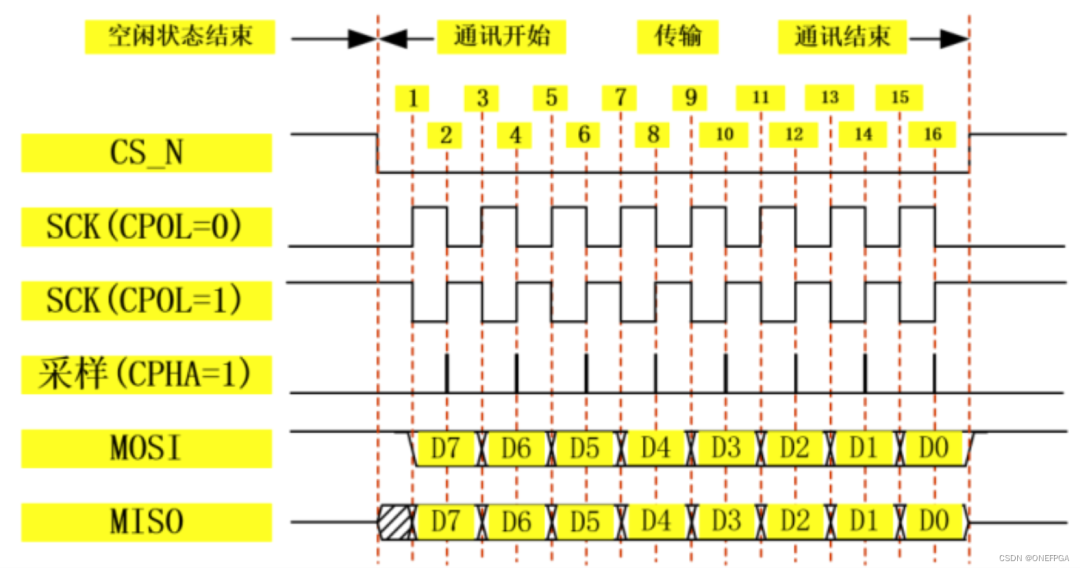

在芯片的研发环节,FPGA验证是其中的重要的组成部分,如何有效的利用FPGA的资源,管脚分配也是必须考虑的一个重要问题。一般较好的方法是在综合过程中通过时序的一些约束让对应的工具自动分配,但是从研发的时间段上来考虑这种方法往往是不可取的,RTL验证与验证板设计必须是同步进行的,在验证代码出来时验证的单板也必须设计完毕,也就是管脚的分配也必须在设计代码出来之前完成。所以,管脚的分配更多的将是依赖人,而非工具,这个时候就更需要考虑各方面的因素。 分配fpga管脚时该怎么选择,引脚有什么属性需要考虑,引脚有几个属性:Reserved,Group,I/O Bank,Vref Group,I/O standard(3.3-V LVTTL(default))分别是什么意思,要怎么设置? 1)、首先说IOstandard:这个是用于支持对应不同的电平标准。FPGAIO口的电压由IO bank上的VCC引入。一个bank 上引入3.3VTTL电平,那么此时整个bank 上输出3.3V的TTL 电平。设置这个的原因一是为了和current strength一起计算功率。二是为了用于在IO口上加载正确的上拉/下拉电阻。只要你设置完成,Quartus会按照你的电平标准自动布线。 2)、第二是IO Bank:你在quartus pin planner的top view下右键然后点击 show IO banks,这个时候就会看到FPGA的管脚被几种颜色划分开了。一种颜色下的IO口代表一组bank。把管脚的location约束完成以后,IOBank会自动填充完毕的。 3)、第三是Group:Group就是你所输出的信号的名字。比如你有一组信号叫cnt。你对cnt的某一根赋值,那么......这里的Group会自动填充为cnt。 4) 、第四是Reserved:这个是对管脚内部的IO逻辑进行约束的,你在下面可以看到一些值。 介绍几个吧。 bidrectional:双向; tri-state:三态等等。 这个约束的是FPGA在IO端的输入输出区域的逻辑。比如你选择tri-state。那么这个时候,在你IO口前部的IO区,quartus会自动给你生成一个三态门。 5)、第五个是Vref Group:这个Group是bank内部的细分区域,因为一个bank可能多达60个脚。为了快速定位,你可以利用这个vref group来找到某个管脚。(这个是非修改属性)无法修改。 以下是系统的介绍FPGA的引脚相关知识,大家需要的可以慢慢品读。这里说的硬件结构主要从FPGA的引脚功能方面描述,FPGA内部的电路逻辑暂不讨论。FPGA的引脚大致可以分为三类:功能引脚、IO引脚、电源和接地引脚。FPGA的功能引脚包含了FPGA配置程序加载、FPGA配置模式选择、状态及错误提示、JTAG调试等等。(1)DCLK、DATA0、NCONFIG、CONF_DONE这几个引脚是配置FPGA所必须的,(4)TDI、TDO、TMS、TCK四个脚是JTAG调试使用,一般会预留。FPGA的IO引脚是芯片与外部电路的接口部分,完成在不同电气特性下对输入/输出信号的驱动与匹配要求。FPGA的IO引脚按组分类,每组都能够独立地支持不同的IO标准。通过软件的灵活配置,可适配不同的电气标准与IO物理特性,可以调整驱动电流的大小,可以改变上、下拉电阻。为了便于管理和适应多种电器标准,FPGA的IO引脚被划分为若干个Bank,每个BANK的接口标准由其接口电压VCCIO决定。一个BANK只能有一种VCCIO,但不同的BANK的VCCIO可以不同,只有相同电气标准的端口才能接到一起。电源引脚为不同的电气需求提供不同的电压,包括VCCINT、VCCIO、VCCA、VCCD_PLL等。不同的BANK可以使用不同的IO电压,也可以连在一起使用相同的IO电压。接地引脚可以全部连在一起接到GND上。硬件上通过连接MSEL四个引脚的组合方式来选择使用哪种模式,主流方案使用的是被动串行配置(PS)方案。在 PS 配置方案中,可以使用微处理器控制从存储器件 (例如闪存)传输配置数据到目标 Cyclone IV 器件。可以将配置数据存储为 .rbf、 .hex 或 .ttf 的格式。(1)当其nCONFIG引脚被拉低时,器件处于复位状态,这时所有的配置RAM内容被清空,并且所有I/O处于高阻态,FPGA的状态引脚nSTATUS和CONFIG_DONE引脚也将输出为低。(2)当FPGA的nCONFIG引脚上出现一个从低到高的跳变以后,配置就开始了,同时芯片还会去采样配置模式(MSEL)管脚的信号状态,决定接受何种配置模式。随之,芯片将释放漏极开路输出的nSTATUS引脚,使其由片外的上拉电阻拉高,这样,就表示FPGA可以接收配置数据了。(3)FPGA在 DATA[0] 上接收配置数据,在 DCLK 上接收时钟。在 DCLK 的上升沿,数据被锁存到器件中。数据不断送入目标器件,直到 CONF_DONE 变高以及器件进入初始化状态。(4)主控必须一次一个位地将配置数据放置在 DATA[0] 上。如果使用的配置数据格式为 .rbf、 .ttf 或 .hex,必须首先发送每个数据字节的 LSB。例如,如果 .rbf 包含的字节序列为 02 1B EE 01 FA,那么必须发送到器件的串行比特流是 : 0100-0000 1101-1000 0111-0111 1000-0000 0101-1111(5)当配置数据被全部载入到FPGA中以后,FPGA上的CONF_DONE信号就会被释放,而漏极开路输出的CONF_DONE信号同样将由外部的上拉电阻拉高。(6)CONF_DONE引脚的从低到高的跳变意味着配置的完成,初始化过程的开始,而并不是芯片开始正常工作。(7)INIT_DONE是初始化完成的指示信号,它是FPGA中可选的信号,需要通过Quartus II工具中的设置决定是否使用该引脚。这个引脚不是必须使用的,很多FPGA方案中没有使用这个引脚。FPGA除了对IO引脚进行控制外,还可以和外界数据进行通讯。FPGA通常挂载在类似Nand控制器这样的总线上,比如VxWorks的Local Bus。类似Nand有8个数据脚,FPGA内部会配置出8个或者16个地址/数据脚来收发数据。整个通讯过程和读写Nand类似,当读写的地址区间在到FPGA映射的内存地址范围时,片选会自动识别到是FPGA的数据。这个图很关键,指明了要使用GPMC模式,就必须按照这种方式来接线。注意有一个很明显的地方就是P2020的低位数据接到了外设的高位数据 这点不仅是在寄存器设置的时候要注意,硬件连接也要注意。我们这里使用的是zynq,因此不用关系这个问题会带来灾难性的错误,重新配置下管脚约束不就好了。低位地址线需要锁存器来进行解复用。我们用的是FPGA,可以很灵活的解决这个问题。这里我们的硬件连接直接把P2020的LocalBus接到了xcz7045上面。看起来很简单,不分析时序了,直接在zynq上面编码就好了。这里还有很重要的一步,配置LocalBus的功能寄存器。LocalBus只需要配置两个寄存器eLBC_BR0和eLBC_ORg0,注意后面的数字代表的是对应的硬件管脚上面的片选信号。eLBC_BR0寄存器设置了基地址、总行功能模式、ECC校验、写保护、Machine select以及Valid bit。eLBC_ORg0寄存器配置了AM(地址掩码)以及访问时序。根据器件手册以及我们要实现的功能,在vxWorks中对这两个寄存器做如下配置:这里重0xe9000000映射了1M字节的空间到外设。首先把示波器调成下降沿触发,接到CS2管脚上。**触发,等待下降沿的到来。然后在shell中输入d 0xe9000000,这时候,vxWorks会读取0xe9000000上面的数据,如果LAW、MMU、LBS都配置正确,CS引脚会被拉低。1、先把信号全部设置成input,通过ILA来抓取信号,观察信号的规律;2、根据抓取到的信号进行解复用,解析出地址和数据;3、写接口只要在写使能信号有效的时刻,准备好相应的数据即可; address_high<={LA[0],LA[1],LA[2],LA[3],LA[4],LA[5],LA[6],LA[7],LA[8],LA[9],LA[10],LA[11],LA[12],LA[13],LA[14],LA[15]}; data<={LA[0],LA[1],LA[2],LA[3],LA[4],LA[5],LA[6],LA[7],LA[8],LA[9],LA[10],LA[11],LA[12],LA[13],LA[14],LA[15]};也可以定义几个引脚挂载在SPI总线上,只要时序能对应上就行。1 条时钟信号线、2 条数据总线和 1 条片选信号线, 时钟信号线为SCK,2 条数据总线分别为 MOSI(主输出从输入)、MISO(主输入从输出),片选信号线为CS,它们的作用介绍如下:(1) SCK (Serial Clock):时钟信号线,用于同步通讯数据。由通讯主机产生,决定了通讯的速率,不同的设备支持的最高时钟频率不同,两个设备之间通讯时,通讯速率受限于低速设备。(2) MOSI (Master Output, Slave Input):主设备输出/从设备输入引脚。主机的数据从这条信号线输出,从机由这条信号线读入主机发送的数据,数据方向由主机到从机。(3) MISO (Master Input,Slave Output):主设备输入/从设备输出引脚。主机从这条信号线读入数据,从机的数据由这条信号线输出到主机,数据方向由从机到主机。(4) CS(Chip Select):片选信号线,也称为 CS_N,以下用 CS_N 表示。当有多个 SPI从设备与 SPI 主机相连时,设备的其它信号线 SCK、MOSI 及 MISO 同时并联到相同的 SPI总线上,即无论有多少个从设备,都共同使用这 3 条总线;而每个从设备都有独立的这一条 CS_N 信号线,本信号线独占主机的一个引脚,即有多少个从设备,就有多少条片选信号线。I2C 协议中通过设备地址来寻址、选中总线上的某个设备并与其进行通讯;而 SPI协议中没有设备地址,它使用 CS_N 信号线来寻址,当主机要选择从设备时,把该从设备的 CS_N 信号线设置为低电平,该从设备即被选中,即片选有效,接着主机开始与被选中的从设备进行 SPI 通讯。所以 SPI 通讯以 CS_N 线置低电平为开始信号,以 CS_N 线被拉高作为结束信号。SPI 通讯协议一共有四种通讯模式,模式 0、模式 1、模式 2 以及模式 3,这 4 种模式分别由时钟极性(CPOL,Clock Polarity)和时钟相位(CPHA,Clock Phase)来定义,其中CPOL参数规定了空闲状态(CS_N 为高电平,设备未被选中)时 SCK时钟信号的电平状态,CPHA规定了数据采样是在 SCK时钟的奇数边沿还是偶数边沿。模式 0:CPOL= 0,CPHA=0。空闲状态时 SCK 串行时钟为低电平;数据采样在 SCK时钟的奇数边沿,本模式中,奇数边沿为上升沿;数据更新在 SCK 时钟的偶数边沿,本模式中,偶数边沿为下降沿。模式 1:CPOL= 0,CPHA=1。空闲状态时 SCK 串行时钟为低电平;数据采样在 SCK时钟的偶数边沿,本模式中,偶数边沿为下降沿;数据更新在 SCK 时钟的奇数边沿,本模式中,偶数边沿为上升沿。模式 2:CPOL= 1,CPHA=0。空闲状态时 SCK 串行时钟为高电平;数据采样在 SCK时钟的奇数边沿,本模式中,奇数边沿为下降沿;数据更新在 SCK 时钟的偶数边沿,本模式中,偶数边沿为上升沿。模式 3:CPOL= 1,CPHA=1。空闲状态时 SCK 串行时钟为高电平;数据采样在 SCK时钟的偶数边沿,本模式中,偶数边沿为上升沿;数据更新在 SCK 时钟的奇数边沿,本模式中,偶数边沿为下降沿。CPOL为时钟极性,也就是在信号片选未选中时,时钟信号的高低,CPOL = 0 时,片选未选中 SCK = 0。反之。而CPHA为时钟相位。CPHA = 0 是,数据采样为计数沿,否则为偶数沿采样。

至芯科技12年不忘初心、再度起航3月6日西安中心FPGA工程师就业班开课、线上线下多维教学、欢迎咨询!

欢迎加入至芯科技FPGA微信学习交流群,这里有一群优秀的FPGA工程师、学生、老师、这里FPGA技术交流学习氛围浓厚、相互分享、相互帮助、叫上小伙伴一起加入吧!

原文标题:FPGA引脚简介

文章出处:【微信公众号:FPGA设计论坛】欢迎添加关注!文章转载请注明出处。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

原文标题:FPGA引脚简介

文章出处:【微信号:gh_9d70b445f494,微信公众号:FPGA设计论坛】欢迎添加关注!文章转载请注明出处。

相关推荐

最近在做DLP DIscovery 4100 的FPGA开发,我想问一下上位机软件发送给开发板的图像数据为几位,在FPGA里面的引脚信号是哪个

发表于 03-03 08:17

概述: 利用FPGA实现AD芯片的时序,进一步实现与AD芯片数据的交互,主要熟悉FPGA对时序图的实现,掌握时序图转换Verilog硬件描述语言技巧后与其它芯片进行数据的交互也是类似的。 说明

![的头像]() 发表于

发表于 12-17 15:27

•773次阅读

你好,我在FPGA接收ADC的DCLKP和DCLKM引脚(也即接收DCLK信号),用ILA抓出来的波形如下图所示,可以发现DCLK信号会出现规律性持续为0,且在有DCLK信号的时候,他的波形并不是

发表于 11-19 08:08

在 FPGA 设计中,复位起到的是同步信号的作用,能够将所有的存储元件设置成已知状态。在数字电路设计中,设计人员一般把全局复位作为一个外部引脚来实现,在加电的时候初始化设计。全局复位引脚与任何

![的头像]() 发表于

发表于 11-16 10:18

•780次阅读

闪电定位仪应用简介

发表于 11-13 16:34

•0次下载

本文将首先介绍FPGA的基础知识,包括FPGA的工作原理以及为什么要使用FPGA等,然后讨论设计和执行FPGA应用所需的工具。

![的头像]() 发表于

发表于 11-11 11:29

•1485次阅读

电子发烧友网站提供《TI 降压转换器多功能引脚及其应用的简介.pdf》资料免费下载

发表于 09-10 10:26

•0次下载

FPGA和MCU各有其独特的优势和适用场景。以上都是官方的话术,然后我来说一下我的理解:

高并行处理能力

它可以做到某个引脚和其他引脚相关联,某个引脚又和另外的

发表于 07-29 15:45

基本简介 P4 Suite for FPGA是一款 综合性工具套件, 可在数字网络的不同领域提供广泛功能,该套件能够以高达200 Gbps甚至更高的数据传输速率支持FPGA。这一

![的头像]() 发表于

发表于 07-25 14:55

•1197次阅读

前言

对于需要在PCB板上使用大规模FPGA器件的设计人员来说,I/O 引脚分配是必须面对的众多挑战之一。由于众多原因,许多设计人员发表为大型FPGA 器件和高级BGA封装确定I/O引脚

发表于 07-22 00:40

用Spartan-6 FPGA驱动ADC AD9265,由于原理图设计问题(SVDD=1.8V) ,部分引脚控制线(AD9265的DFS引脚)接收的电平标准应该是1.8V,但是所有FPGA

发表于 06-27 10:12

今天给大侠带来 Xilinx ISE14.7 LVDS应用,话不多说,上货。

最近项目需要用到差分信号传输,于是看了一下FPGA上差分信号的使用。Xilinx FPGA中,主要通过原语实现差分信

发表于 06-13 16:28

FPGA的学习。

在学习中才发现,FPGA远不是门电路那么简单。FPGA中有各种需要的资源,比如门电路、存储单元、片内RAM、嵌入式乘法器、PLL、IO引脚等。等于是说,可以根据需求,

发表于 05-22 18:27

引脚

橙群微电子

发布于 :2024年05月21日 16:25:59

AMD FPGA在配置了适当的启动模式后,上电即会按该模式去加载配置文件。以7系列FPGA为例,假设设置模式引脚M[2:0]=3’b001,上电后FPGA会以Master SPI方式尝

发表于 04-25 12:49

•776次阅读

FPGA引脚简介

FPGA引脚简介

评论