闪存模数转换器,也称为并行ADC,是将模拟信号转换为数字信号的最快方法。闪存ADC适用于需要超大带宽的应用。但是,这些转换器消耗相当大的功率,分辨率相对较低,并且可能非常昂贵。这限制了它们通常无法以其他方式解决的高频应用。典型示例包括数据采集、卫星通信、雷达处理、采样示波器和高密度磁盘驱动器。

建筑细节

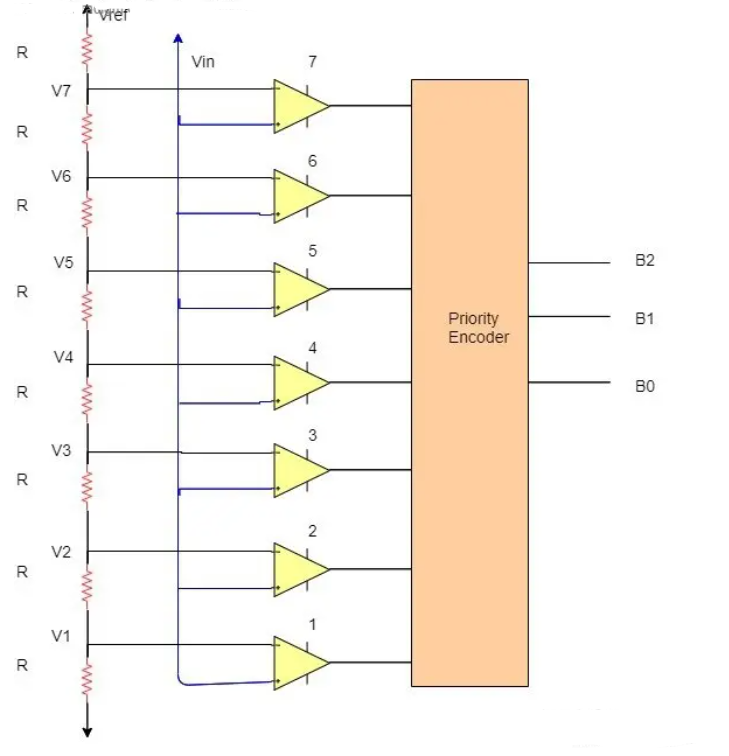

闪存ADC由级联高速比较器组成。图1所示为典型的闪存ADC框图。对于N位转换器,电路采用2N-1 个比较器。电阻分压器,带 2N电阻提供基准电压。每个比较器的基准电压比其正下方比较器的基准电压大一个最小有效位(LSB)。当每个比较器的模拟输入电压高于施加在其上的基准电压时,每个比较器产生1。否则,比较器输出为0。因此,如果模拟输入在V之间X4和 VX5、比较器 X1通过 X4产生1s,其余比较器产生0s。代码从 <> 变为 <> 的点是输入信号小于相应比较器基准电压电平的点。

图1.闪存 ADC 架构。如果模拟输入介于 V 之间X4和 VX5、比较器 X1通过 X4产生1s,其余比较器产生0s。

这种体系结构称为温度计代码编码。之所以使用这个名称,是因为该设计类似于水银温度计,其中汞柱始终上升到适当的温度,并且在该温度以上不存在汞。然后将温度计代码解码为适当的数字输出代码。

比较器通常是宽带低增益级级的级联。它们是低增益的,因为在高频下很难同时获得宽带宽和高增益。比较器设计用于低压失调,因此每个比较器的输入失调小于ADC的LSB。否则,比较器的失调可能会错误地使比较器跳闸,导致数字输出代码不代表温度计代码。每个比较器输出端的再生锁存器存储结果。锁存器具有正反馈,因此最终状态被强制为 1 或 0。

鉴于这些基础知识,需要进行一些调整来优化闪存转换器架构。

闪光代码

通常,比较器输出将是温度计代码,例如00011111。错误可能会导致类似00010111的输出,这意味着结果中存在虚假零。这种乱序0称为闪光,这是由不完美的输入建立或比较器时序不匹配引起的。误差的大小可能非常大。MAX109/MAX104等现代转换器在ADC前面采用输入采样保持以及抑制闪烁码的编码技术。

亚稳态

当比较器的数字输出不明确(既不是1也不是0)时,输出定义为亚稳态。通过留出更多再生时间可以降低亚稳态。格雷码编码一次只允许输出中的1位变化,可以大大提高亚稳定性。.因此,比较器输出首先转换为格雷码编码,然后根据需要解码为二进制。

当亚稳输出驱动两个不同的电路时,会出现另一个问题。一个电路可以将输入声明为1,而另一个电路认为输入为0。这可能会产生重大错误。为了避免这种冲突,只有一个电路应检测潜在的可测量输出。

输入信号频率依赖性

当输入信号在所有比较器完成其任务之前发生变化时,ADC的性能会受到不利影响。最严重的影响是随着模拟输入频率的增加,信噪比(SNR)加失真(SINAD)下降。

测量无杂散动态范围(SFDR)是观察转换器性能的另一种好方法。ADC实现的“有效位”是输入频率的函数;通过在ADC前面增加一个采样保持(T/H)电路,可以对其进行改进。T/H电路允许显著改善,特别是当输入频率接近奈奎斯特频率时,如图2所示(取自MAX104数据资料)。没有 T/H 的零件在 SFDR 中显示出显着下降。

图2.无杂散动态范围与输入频率的函数关系。

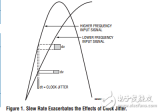

时钟抖动

当采样时钟中存在抖动时,SNR会降低。对于高模拟输入频率,这一点变得很明显。为了获得准确的结果,为ADC提供低抖动采样时钟源至关重要。

架构权衡

ADC可以通过采用各种架构来实现。这些替代方案之间的主要权衡是:

完成转换所需的时间(转换时间)。对于闪存转换器,转换时间不会随着分辨率的提高而发生重大变化。然而,逐次逼近寄存器(SAR)或流水线转换器的转换时间随着分辨率的提高而近似线性增加(图3a)。对于集成ADC,分辨率每提高一位,转换时间就会翻倍。

电路中的元件匹配要求。闪存ADC组件匹配通常将分辨率限制在8位左右。校准和调整有时用于改善芯片上可用的匹配。组件匹配要求随着分辨率的提高而翻倍。此模式适用于闪存、逐次逼近或流水线转换器,但不适用于集成转换器。对于集成转换器,元件匹配不会随着分辨率的提高而大幅增加(图 3b)。

芯片尺寸、成本和功耗。对于闪存转换器,分辨率每提高一位,ADC内核电路的尺寸就会增加一倍。功率也翻了一番。相比之下,SAR、流水线或Σ-Δ型ADC芯片尺寸将随着分辨率的提高而线性增加;积分转换器内核芯片尺寸不会随着分辨率的增加而发生实质性变化(图 3c)。最后,众所周知,芯片尺寸的增加会增加成本。

图3.架构权衡。

闪存 ADC 与其他 ADC 架构的比较

闪存 ADC 与 SAR ADC

在SAR转换器中,单个高速、高精度比较器确定位,一次确定一位(从MSB到LSB)。这是通过将模拟输入与DAC进行比较来完成的,DAC的输出由先前确定的位更新,从而连续接近模拟输入。SAR的这种串行特性将其速度限制在不超过每秒几兆采样(Msps),而闪存ADC则超过每秒千兆采样(Gsps)转换速率。

SAR 转换器的分辨率高达 16 位。这种器件的一个例子是MAX1132。闪存ADC通常限制在8位左右。较慢的速度也使SAR ADC的功耗低得多。例如,MAX1106是一款8位SAR转换器,在100.3V时功耗为3μA,转换速率为25ksps。MAX104的功耗为5.25W,功耗比MAX16高约000,1106倍,最大采样速率快40,000倍。

SAR 架构也更便宜。1106k产量的MAX1售价超过一美元(美元),而MAX104的售价为几百美元(美国)。闪存转换器的封装尺寸更大。除了更大的芯片尺寸需要更大的封装外,封装还需要消耗相当大的功率,并且需要许多引脚来实现电源和接地信号完整性。MAX104的封装尺寸是MAX50的1106倍以上。

闪存 ADC 与流水线 ADC

流水线ADC采用并联结构,其中每级同时处理一到几位连续采样。这种设计以功耗和延迟为代价提高了速度,但每个流水线级都比闪存部分慢得多。流水线ADC要求DAC和级间放大器进行精确放大,这些级必须稳定到所需的线性度电平。相比之下,在闪存ADC中,比较器只需要低失调,并将其输入解析为数字电平;不涉及线性建立时间。一些闪存转换器需要前置放大器来驱动比较器。需要仔细指定增益线性度。

流水线转换器在 100 至 8 位分辨率下以大约 14Msps 的速度进行转换。流水线转换器的一个例子是MAX1449,这是一款105MHz、10位ADC。对于给定的分辨率,流水线ADC比类似分辨率的闪存转换器慢约10倍。流水线转换器可能是需要以高达100Msps左右的速率采样、分辨率为10位及以上的ADC的最佳架构。对于高达10位的分辨率和几百Msps以上的转换速率,闪存ADC占主导地位。

有趣的是,在某些情况下,闪存ADC隐藏在采用另一种架构以提高其速度的转换器内。

闪存与集成式ADC

单斜率、双斜率和多斜率ADC可实现16位或更高的高分辨率,价格相对便宜,功耗也更小。这些器件支持非常低的转换速率,通常每秒不到几百个样本。大多数应用用于监测仪器仪表和工业市场中的直流信号。这种架构与Σ-Δ转换器竞争。

闪存与Σ-Δ型ADC

闪存ADC不与Σ-Δ架构竞争,因为目前可实现的转换速率相差多达两个数量级。Σ-Δ 架构适用于带宽低得多(通常小于 1MHz)且分辨率在 12 至 24 位范围内的应用。Σ-Δ转换器能够在ADC中实现尽可能高的分辨率。它们需要更简单的抗混叠滤波器(如果需要)来在转换前对信号进行带宽限制。

Σ-Δ型ADC通过过采样来换取速度分辨率,然后进行滤波以降低噪声。然而,这些器件对于多通道应用并不总是有效的。此架构可以使用采样数据滤波器(也称为调制器或连续时间滤波器)来实现。对于更高的频率转换速率,连续时间架构有可能以6至8位的低分辨率达到数百Msps范围内的转换速率。这种方法仍处于早期研发阶段,与较低转化率范围内的闪存替代品竞争。

闪存ADC的另一个有趣用途是作为Σ-Δ电路内的构建模块,以提高ADC的转换速率。

子范围模数转换器

当需要更高分辨率的转换器或更小的芯片尺寸和功率以获得给定分辨率时,采用多级转换。这种架构称为子范围转换器,有时也称为多步或半闪存转换器。这种方法结合了逐次逼近和闪存架构的思想。

子范围ADC减少了要转换为较小组的位数,然后通过较低分辨率的闪存转换器运行。与闪存转换器相比,这种方法减少了比较器的数量,并降低了逻辑复杂性(图 4)。与闪存相比,这种权衡导致转换速度较慢。

图4.子范围 ADC 架构。

MAX153为8位、1Msps ADC,采用子量程架构。该电路采用两步技术。首先,使用4位转换器完成转换。产生残差,其中8位精度DAC将4位转换的结果转换回模拟信号。从输入信号中减去模拟信号。其次,该残余再次由4位ADC转换,并将第一遍和第二遍的结果组合在一起,提供8位数字输出。

工艺技术

闪存转换器的速度目前超过1Gsps。 2.2Gbps MAX109采用先进的SiGE工艺制造。MAX108 (1.5Gsps)、MAX104 (1Gsps)和MAX106 (600Msps)8位ADC采用Maxim专有的先进GST-2双极性工艺(“千兆”速度硅双极性工艺)制造。

与双极性技术产品相比,CMOS闪存转换器的分辨率较低。这些ADC通常用于集成到更大的CMOS电路中。CMOS、BiCMOS和双极技术将继续改进,产生越来越高的转化率。

结论

对于要求中等分辨率(通常高达8位)且采样频率高达数百MHz的应用,闪存架构可能是唯一可行的替代方案。用户必须提供低抖动时钟,以确保良好的ADC性能。对于具有高模拟输入频率的应用,所选的ADC应具有内部采样保持功能。

审核编辑:郭婷

-

转换器

+关注

关注

27文章

8707浏览量

147221 -

驱动器

+关注

关注

52文章

8241浏览量

146399 -

adc

+关注

关注

98文章

6500浏览量

544720

发布评论请先 登录

相关推荐

高速ADC时钟抖动的影响的了解

闪存存储器你了解多少

ADuC832:带嵌入式62 kB闪存MCU的MicroConverter、12位ADC和DAC产品手册

了解闪存ADC

了解闪存ADC

评论