自从2.5D/3D封装、Chiplet、异构集成等技术出现以来,CPU、GPU和内存之间的界限就已经变得逐渐模糊。单个SoC究竟集成了哪些逻辑单元和存储单元,全凭借厂商自己的设计路线。这样的设计其实为单芯片的能效比带来了一轮新的攀升,但也极大地增加了开发难度。即便如此,还是有不少厂商在不遗余力地朝这个方向发展,最典型的莫过于AMD。

AMD的存储堆叠之路

要说玩堆叠存储,AMD确实是走得最靠前的一位,例如AMD如今在消费级和数据中心级别CPU上逐渐使用的3D V-Cache技术,就是直接将SRAM缓存堆叠至CPU上。将在今年正式落地的第四代EPYC服务器处理器,就采用了13个5nm/6nm Chiplet混用的方案,最高将L3缓存堆叠至了可怕的384MB。

在消费端,AMD的Ryzen 7 5800X3D同样也以惊人的姿态出世,以超大缓存带来了极大的游戏性能提升。即将正式发售的Ryzen 9 7950X3D也打出了128MB三级缓存的夸张参数,这些产品的出现可谓打破了过去CPU厂商拼时钟频率、拼核心数的僵局,让消费者真切地感受到了额外的体验提升。

MI300 APU / AMD

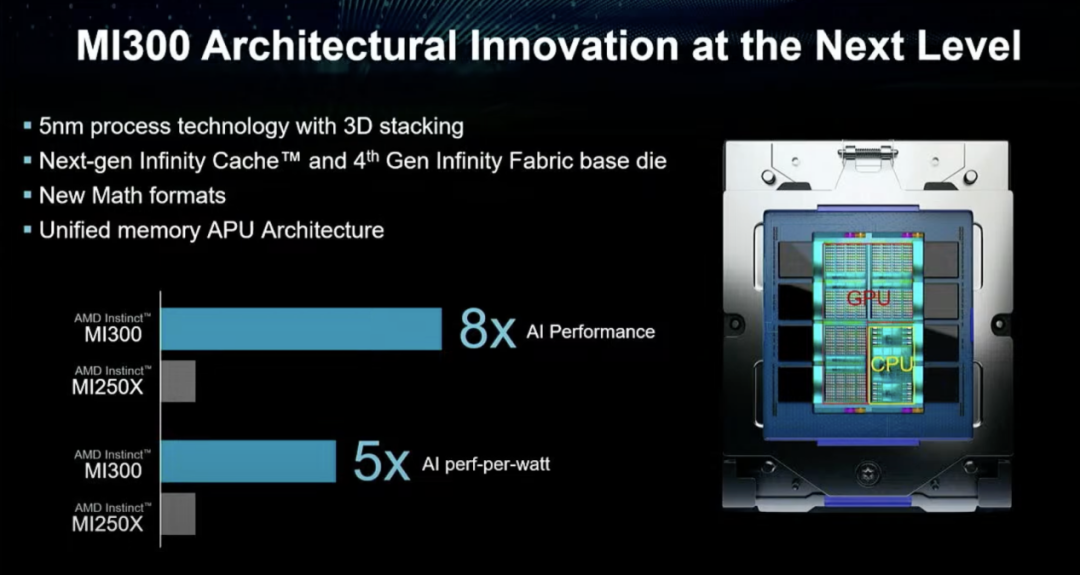

GPU也不例外,虽然AMD如今的消费级GPU基本已经放弃了HBM堆叠方案,但是在AMD的数据中心GPU,例如Instinct MI250X,却依然靠着堆叠做到了128GB的HBM2e显存,做到了3276.8GB/s的峰值内存带宽。而下一代MI300,AMD则选择了转向APU方案,将CPU、GPU和HBM全部整合在一起,以新的架构冲击Exascale级的AI世代。

其实这也是AMD收购Xilinx最大的收获之一,早在十多年前Xilinx的3DIC技术也已经为多Die堆叠打下了基础。在收购Xilinx之际,AMD也提到这次交易会扩张AMD在die堆叠、封装、Chiplet和互联技术上的开发能力。在完成Xilinx的收购后,也可以看出AMD在架构上的创新有了很大的飞跃。

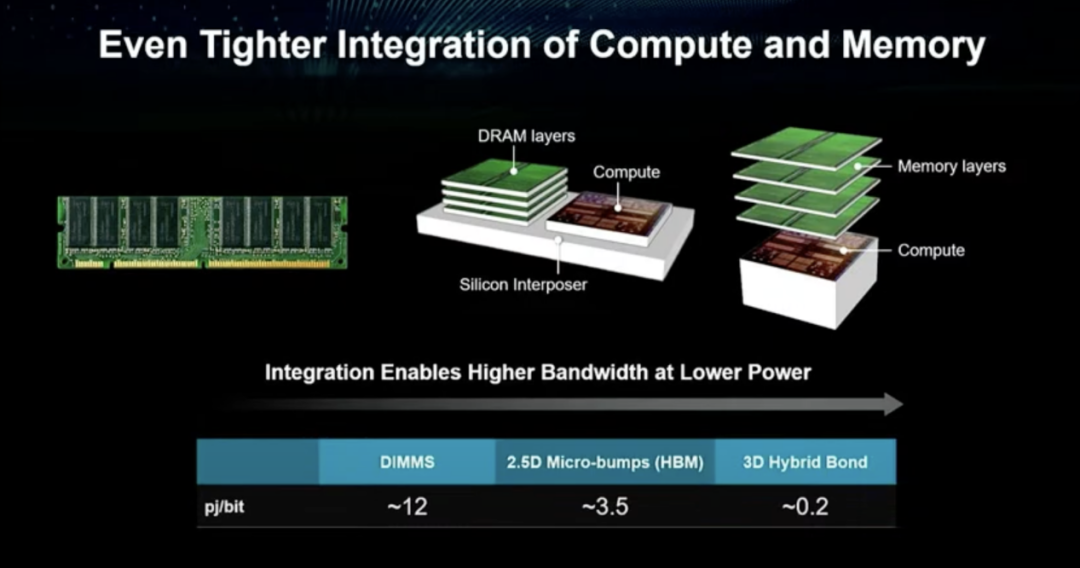

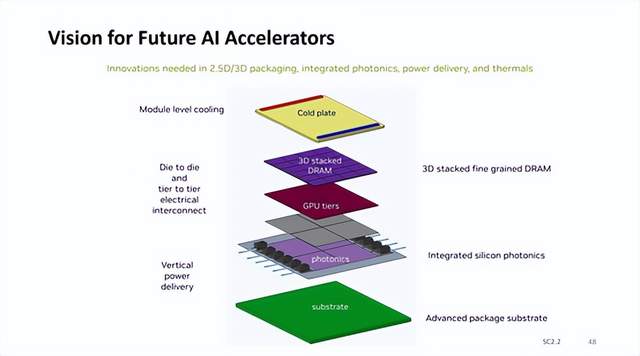

在近期的ISSCC 2023上,AMD CEO苏姿丰透露了他们的下一步野心,那就是直接将DRAM堆叠至CPU上。这里的堆叠并非硅中介层互联、存储单元垂直堆叠在一起的2.5D封装方案,也就是如今常见的HBM统一内存方案,AMD提出的是直接将计算单元与存储单元垂直堆叠在一起的3D混合键封装方案。

CPU与DRAM垂直堆叠

主流服务器性能的提升速度,已经快要赶上过去的摩尔定律了。根据AMD统计的CPU供应商数据,每过2.4年主流服务器性能就会翻一倍。可限制其继续发展的不再只是放缓的摩尔定律,还有内存上带来的限制。内存墙这样的性能瓶颈,不仅在限制CPU的性能发挥,同样限制了GPU的性能发挥。

考虑到明面上解决这个问题的主力军是存储厂商,所以提出的大部分创新方案,例如存内计算等等,也都是创造算力更高的存储器产品。苏姿丰博士也指出,从她这个处理器从业者的角度来说,这一路线有些反常理,但从系统层面来说,她也可以理解该需求存在的意义。而AMD这次提出的方案,则是从计算芯片出发,将存储器堆叠整合进去。

CPU与DRAM垂直堆叠 / AMD

从AMD给出的能量效率分析来看,DIMM这样的片外内存访问能量效率在12pj/bit左右,2.5D的HBM方案在3.5pj/bit左右,而3D垂直堆叠的键合方案却可以做到0.2pj/bit,从而利用更低的功耗来做到大带宽。况且由于计算单元和存储单元的集成度更高了,传输的延迟必然也会有显著的降低。

这套方案的出现意味着至少堆叠的内存容量足够大,服务器CPU甚至可以省去DIMM内存插槽,进一步减小空间占用。但这套方案具体能做堆叠多少内存,AMD并没有给出具体的数字,如果可堆叠的内存数量与如今的L3缓存一样仅有数百兆的话,那带来的性能提升很可能不值一提。

另外就是散热问题,从AMD给出的示意图来看,他们选择了内存单元在上,计算单元在下的方案,这种3D架构很可能会对散热产生一定负面作用,但性能损失会相对较少一些。比如MI300方案中,AMD就换成了CPU和GPU单元在上,缓存和互联在下的方案。

捆绑销售嫌疑?

在消费级领域,其实CPU与内存捆绑销售已经不是什么新鲜事了,就拿苹果的M系列芯片为例。自打苹果转向Arm阵营,推出M系列芯片后,Mac生态的定制空间就基本只存在于购买前了,虽然华强北的大神们依然能够找到一些方式来扩展固态硬盘闪存,但内存基本就与SoC彻底绑定了,用户只能忍受高昂的容量定价,才不会在高负载工作时出现内存不够用的窘境。

可在服务器市场,已经有了相当成熟的DIMM内存生态,甚至未来还有CXL内存虎视眈眈,AMD这套“捆绑销售”的方案究竟能否收获良好的市场反响我们无从得知,很明显这对内存模组厂商是存在一定威胁的。但话又说回来,AMD这套方案并没有彻底断绝扩展内存的可能性,在需要超大容量的内存池时,依然可以选择传统的扩展方案,而不是死磕堆叠内存的方案。

AMD的方案更像是给到了一个片上高速方案,从当下的工艺来看,应该还难以实现大容量的堆叠。所以在CPU上垂直堆叠DRAM,更像是AMD的另一套负载加速方案。毕竟根据苏姿丰博士的说法,AMD也很清楚现有的3D V-Cache SRAM堆叠方案只能提高特定负载的性能,DRAM堆叠方案的性能加速覆盖面无疑要更广一些。

写在最后

其实ChatGPT这样的应用出现,不仅带动了一波GPU订单量的狂飙,也让HBM、DDR5这些大带宽的内存有了用武之地,让人们终于看到了打破内存墙的应用价值,而不只是将其视为一个徒增成本的性能瓶颈。

而AMD虽然提出了将内存堆叠至CPU上的技术路线,也并没有放弃对其他方案的考量,比如他们也在和三星展开HBM2上的存算一体研究。如果AMD选择将CPU堆叠内存与存算一体结合在一起的话,或许会给其数据中心产品带来更大的优势。

审核编辑 :李倩

-

amd

+关注

关注

25文章

5466浏览量

134063 -

DRAM

+关注

关注

40文章

2309浏览量

183427 -

cpu

+关注

关注

68文章

10851浏览量

211533

原文标题:AMD要在CPU上堆叠DRAM内存,新一代捆绑销售诞生?

文章出处:【微信号:elecfans,微信公众号:电子发烧友网】欢迎添加关注!文章转载请注明出处。

发布评论请先 登录

相关推荐

佰维存储发布新一代LPDDR5X内存与DDR5内存模组

英伟达AI加速器新蓝图:集成硅光子I/O,3D垂直堆叠 DRAM 内存

AMD发布新一代AI芯片MI325X

主板自检cpu和内存灯一直来回闪

三星积极研发LLW DRAM内存,剑指苹果下一代XR设备市场

三星与海力士引领DRAM革新:新一代HBM采用混合键合技术

美光科技发布新一代GDDR7显存

AMD重磅发布新一代AI PC芯片

超微发布新款AMD H13代CPU服务器产品

SK海力士HBM4E内存2025年下半年采用32Gb DRAM裸片量产

华硕微星发布AGESA固件更新,确认兼容AMD新一代Ryzen处理器

JEDEC发布:GDDR7 DRAM新规范,专供显卡与GPU使用

澜起科技:DDR5第三子代RCD芯片将随新一代CPU平台规模出货

深度解析HBM内存技术

AMD要在CPU上堆叠DRAM内存,新一代捆绑销售诞生?

AMD要在CPU上堆叠DRAM内存,新一代捆绑销售诞生?

评论