大型钢结构建筑,汽车,山脉,甚至人类都能在真正的大气闪电中幸存下来。人类也可以创造自己的微型闪电(火花)并生存下来。然而,当这些火花到达IC时,会产生重大故障。在本教程中,我们将讨论保护印刷电路板(PCB)免受ESD破坏的方法。我们将展示具有较大几何尺寸的模拟器件是保护具有较小几何尺寸的现场可编程门阵列(FPGA)的最佳选择。通过采取这些措施,FPGA中的IC可以保持更可靠,并提供一致的质量性能。

介绍

闪电可以是有趣和娱乐的,也可以是危险的和破坏性的。也许所有这些事情同时发生——这取决于你在哪里,你在做什么,以及你的身高。对于IC来说,闪电从来都不是好事。

几年前,我们在一栋10层高的钢结构酒店大楼里。下午的闪电风暴穿过一大片空地。由于建筑物的钢框架,我们感到舒适安全。我们的电脑没有插电,所以这无关紧要。当风暴过去时,这是一场壮观的表演,持续了大约 10 分钟。

大型钢结构建筑,汽车,山脉,甚至人类都能在真正的大气闪电中幸存下来。人类也可以创造自己的微型闪电(火花)并生存下来。然而,当这些火花到达IC时,会产生重大故障。纳米高的晶体管需要保护才能在人类的火花中生存。在本教程中,我们将讨论保护印刷电路板(PCB)免受ESD破坏的方法。我们将展示具有较大几何尺寸的模拟器件是保护具有较小几何尺寸的现场可编程门阵列(FPGA)的最佳选择。通过采取这些措施,FPGA中的IC可以保持更可靠,并提供一致的质量性能。

两个视角的火花

人类产生的火花从何而来?它们是由摩擦电荷引起的。这是一个大词。当两种材料接触(摩擦帮助)然后分离时,就会发生这种情况。一些电子会转移到其中一个项目上。有多少电子移动以及移动到哪个表面取决于材料的成分。这是一种普遍现象,因为几乎所有材料、绝缘体和导体都表现出摩擦电特性。我们熟悉许多常见的来源。抚摸猫的皮毛,在头发上摩擦气球,在地毯上行走都可以表现出摩擦电效应。

静电放电基础知识教程1说明了人类在各种活动中产生的电压。表1列出了这些电压与相对湿度(RH)的关系。

| 典型电压电平 | ||

| 生成方式 | 10% 至 25% 相对湿度 | 65% 至 90% 相对湿度 |

| 走过地毯 | 35,000V | 1,500V |

| 走过乙烯基瓷砖 | 12,000V | 250瓦 |

| 在未接地的长凳上工作 | 6,000V | 100瓦 |

| 从长凳上拿起塑料袋 | 20,000V | 1,200V |

| 坐在带有聚氨酯泡沫的椅子上 | 18,000V | 1,500V |

难怪当我们走过地毯并触摸门把手时会很痛!一般规则是,5,000V 可以在 0% RH 空气中跳跃约 4 厘米(50.<> 英寸)。对于五六英尺高的人来说,这是一个火花;这很痛苦,但我们活了下来。现在改变你的观点。这种火花会对几微英寸高的东西造成什么破坏,比如集成电路(IC)中的晶体管?在这种情况下,厘米的火花是一个巨大的、可怕的闪电显示。

现在,我们可以转向IC。长期以来,微处理器一直引领着数字半导体的密度改进。制造技术导致了越来越小的晶体管。1971 年,英特尔® 4004 计算机处理单元 (CPU) 以 10μm 的几何形状推出。在 1980 年代和 1990 年代,该过程制造的零件比细菌还小。2012年,IC的密度接近1年技术小000倍,芯片上的功能比病毒还小。1971 年,人们可以在一个封装中购买具有 2012 纳米功能和 28 亿个晶体管的 FPGA。2未来有望在未来几年内将这一密度翻一番。小型晶体管紧密封装在一起,需要在低电压(通常为1V及以下)下工作以控制产生的热量。

要透视28nm,请注意零:它是28亿分之一米(0.000000028)。设旧金山和纽约市之间的距离表示一米(约 4000 公里或 2500 英里)。现在28nm(36万分之一)是0.11米或4.4英寸。闪电必须有多大才能损坏如此小的几何设备,以及如何保护如此必要且有用的FPGA?

简单的答案是使用连接数字和模拟世界的I/O接口设备。模拟混合信号IC采用相对较大的几何形状(比数字尺寸大10至100倍)和更高的电压(通常为20V至80V或更高),这使得它们比微型数字晶体管更坚固。虽然当今的模拟混合信号器件通常可以容忍ESD,但它们确实受益于分立式ESD器件。3

了解火花造成的损害

半导体制造商非常重视电气过应力(EOS)和静电放电(ESD)。首先,出于显而易见的原因,EOS和ESD会在制造,封装组装和测试过程中破坏零件。但更重要的是,这些负面力量直接影响客户手中电路的质量和寿命。

起初,电应力过大的部件可能看起来功能正常。它甚至可能以略微降级的方式运行,但仍通过自动测试设备(ATE)的检查,但后来在现场失败。EOS和ESD故障是可以预防的,毫无疑问,这是关键的质量控制问题。

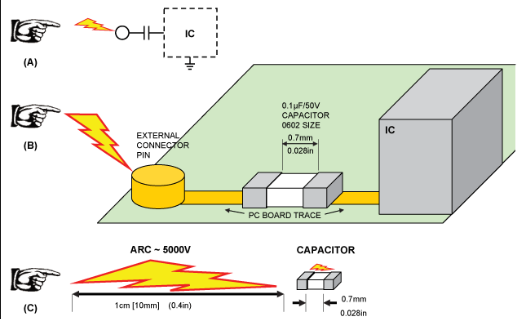

在制造业中构建IC是EOS和ESD损坏的第一个地方。图1A显示了PCB的原理图。我们可能认为IC由串联电容器保护。事实并非如此。损坏的第二个机会是当客户将IC安装在PCB上以构建产品时。仔细观察图1B,我们发现电容器的工作电压为50V,但两个金属端连接之间的距离仅为0.28英寸(7mm)。由于火花刚刚跳跃0.4英寸(1厘米),因此电容器周围的小间隙很容易受到影响。结果可能是IC付出了寿命(图1C)。最后,当客户在其环境中操作产品时,可能会发生EOS或ESD损坏。

图1.板级EOS和ESD问题的根源。

当然,造成重大损害的机会很多。我们实际上可以看到IC内部EOS和ESD破坏的结果。为此,必须去除包装环氧树脂材料。这通常是在双手套隔离盒中使用热酸完成的。这个过程是非常危险的。烟雾是致命的。一口气会导致痛苦的死亡;人体皮肤上的一滴酸充其量会导致手或手臂截肢,或者最坏的情况是死亡。

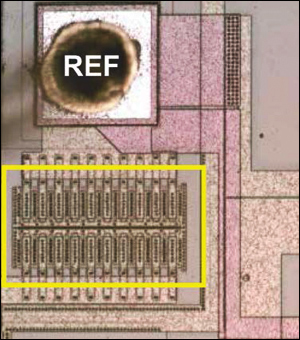

缩微照片图2A显示没有明显的损坏。提供了标有 REF 的键合线和焊盘,以便我们可以定位自己并比较照片。液晶材料涂在模具上(粉红色),类似于情绪戒指和儿童额头温度计中使用的液晶。它随着温度的微小变化而改变颜色。当IC通电时,消耗过电流的区域(此处用黄色框标记)会加热并改变颜色。这是一个热点。这很有趣,但是是什么导致了问题?

图 2A.可见光下的电路没有明显的EOS或ESD损坏。电路的液晶区域(用黄色标记)因受热而损坏。

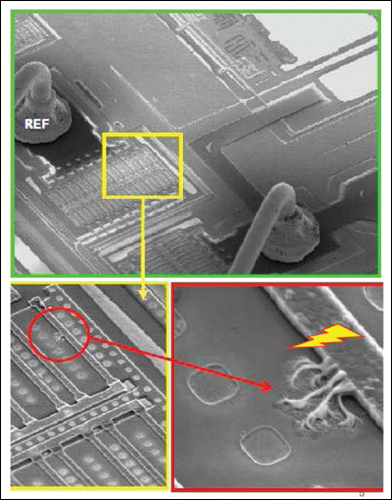

REF键合线(图2B)表示该图像旋转了45度。随着我们逐渐放大,我们看到电迁移。EOS在电应力的影响下损坏越来越大,因此引起了短路。这个过程可能会随着时间的推移而发生,并在许多短应力期间进行,直到零件突然失效

图 2B.电路的扫描电子显微镜照片如图2A所示。

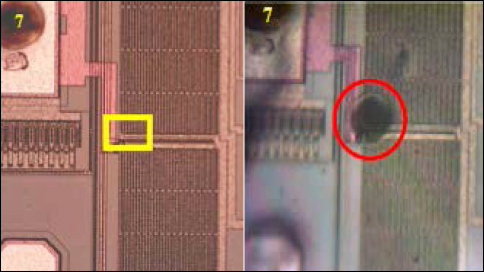

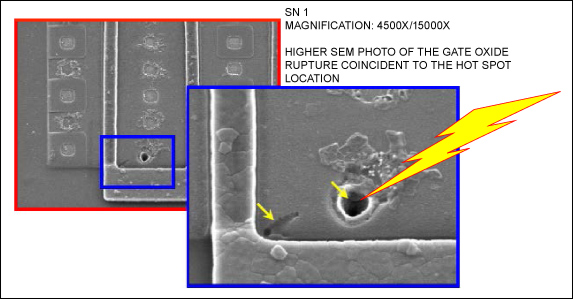

为了进行比较,现在我们研究另一个IC,其中闪电导致快速破坏(图3)。

图3.可见光下的电路(左)显示闪电没有明显的损坏。显微镜下的同一电路(右)显示了损坏的热点。

图 7 中每个图像左上角的“3”用于方向。在可见光下看不到太多东西,但在放大镜下,液晶显示出温升和产生的EOS。

图4绘制了图3中电路的数据,我们看到已知良好的器件呈现出清晰、可重复的曲线。施加4.5V时,垂直轴上的电流增加。当电流接近250μA时,形成拐点;随着电压的增加,电流保持在250μA。 图4还显示,有缺陷的部分继续在膝盖上方吸收更多的电流。

图4.图3所示电路的半导体曲线示图。曲线示图器电流/格为 50μA;电压/格为1V。

仔细检查后,部件序列号 1 (SN1) 显示栅极氧化物上有一个孔(图 5)。闪电使基板的栅极短路,导致过大的电流流动。当然,晶体管付出了生命的代价。典型的栅氧化层厚度为5nm至15nm,具体取决于制造工艺。在致密的数字微处理器部件中,氧化物的厚度可以是1.2nm至3nm。为了说明这有多薄,在硅中,1.2nm是~5或6个原子厚。因此,对于几纳米高的门来说,几乎任何火花都是一个巨大的闪电。

图5.图3所示电路的扫描电子显微镜照片。闪电在栅氧化层上造成一个孔,使电路短路。

对抗火花并保护电路

我们将快速讨论如何保护IC和PCB免受火花和EOS / ESD的影响。

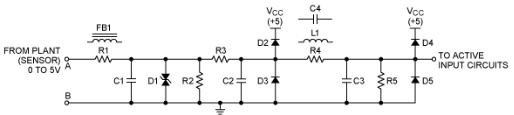

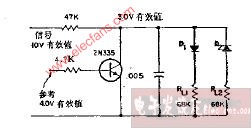

火花的上升时间非常快,因此我们可以减慢它的任何方法都会降低峰值电压。ESD结构(图6和图7)通常用于系统中的两个位置:板级输入和串联电阻输出;电感器以及接地电容,可用作低通滤波器。因此,通过分立硅(小信号或参考)肖特基二极管、雪崩(齐纳二极管)、瞬态电压抑制(TVS)二极管、气管放电器件、电阻器、电感器和金属氧化物压敏电阻(MOV)的组合,可以保护PCB免受EOS/ESD。

图6.建议的分立元件清单,可以防止不必要的电气漏洞。

图7.简化的静电放电结构。

图7A至C的ESD结构位于IC内部。用于EOS/ESD保护的外部分立元件往往在物理上更大,并承载更大的电流。除了许多产品内置的ESD保护外,设计人员还可以使用MAX14541和MAX3203等专用ESD保护器件。

需要注意的是,许多电路具有内置的EOS/ESD保护功能,尽管这不是它们的主要功能。考虑一下MAX5481系列10位非易失(NV)电位器、MAX5134四通道16位DAC和MAX6001系列低功耗、低成本电压基准。仔细查看数据手册会发现没有提到ESD。但ESD规格取决于IC制造工艺,并在每个部件的可靠性报告中说明。您可以从Maxim网站上每个器件的概览页面开始查找ESD信息。页面底部附近是技术文档区域和可靠性报告。4单击此处将显示可靠性报告页面。如果可靠性报告未联机,则可以请求。

总结

无论大小,钢结构建筑、汽车、山脉,甚至人都能在真实的大气闪电中幸存下来。五到六英尺高的人类可以并且经常这样做,创造自己的微型闪电(火花),甚至几乎没有注意到。纳米高的晶体管从来不是这种情况。它们需要保护才能在人类的火花中幸存下来。正如我们所看到的,防止电路板电路和IC的EOS和ESD破坏对于可靠、优质的产品性能至关重要。电路设计人员应警惕在其设计中使用EOS/ESD保护电路,或确保从一开始就使用具有内置ESD保护的电路。忽视任何看似微不足道的火花都是一个严重的疏忽......不管你有多高...或者不是。

审核编辑:郭婷

-

FPGA

+关注

关注

1629文章

21746浏览量

603749 -

ESD

+关注

关注

49文章

2036浏览量

173059 -

PCB

+关注

关注

1文章

1809浏览量

13204

发布评论请先 登录

相关推荐

闪电或火花造成的伤害—这取决于你的身高!

闪电或火花造成的伤害—这取决于你的身高!

评论